| | Aktion |

| 1 | Starten Sie Xilinx ISE Design Suite.

Click auf "Start/Xilinx Design Tools/ISE Design Suite xx.y/ISE Design tools/xx-bit Project

Navigator".

xx = 64 bei 64-bit OS, xx = 32 bei 32-bit OS.

Wenn ein Projekt offen ist, bitte mit File-> Close Project schließen.

|

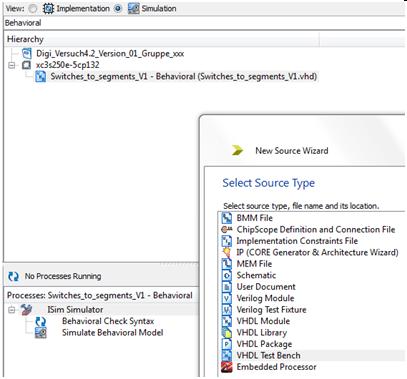

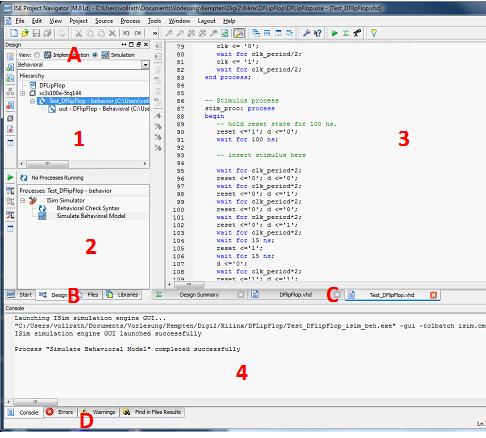

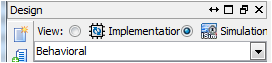

| 2 | Legen Sie ein Neues Project an: New Project.

Name:Digi_Versuch4_Version_01_Gruppe_> Gruppennummer<.

Dann click auf Next.

Top-level source type: auf HDL (Hardware Description Language, also textuelle Eingabe)

|

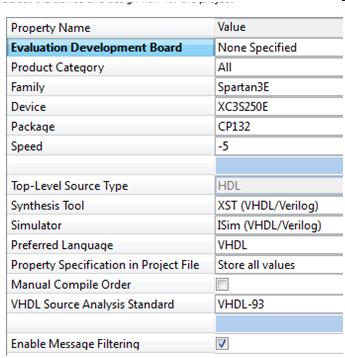

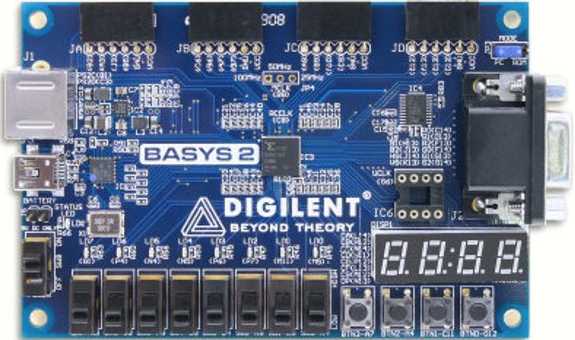

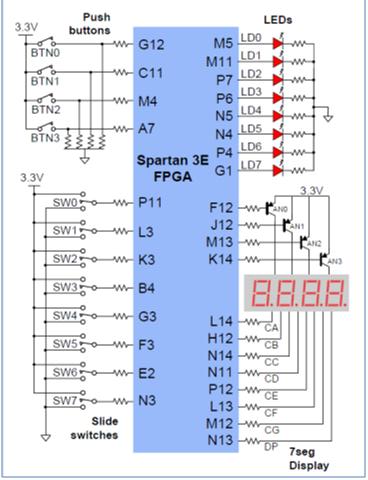

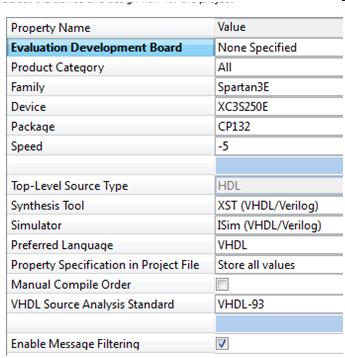

| 3 | Im nächsten Schritt -Project Settings- wählen Sie aus der

Family All/Spartan3E das richtige Device (XC3S250E) und

das richtige Gehäuse (z.B. CP132 für das BASYS 2).

Bei click auf Next bekommen Sie eine Zusammenfassung.

Mit Finish beenden Sie die Konfiguration.

|

| 4 | In diesem Schritt fügen Sie die zum Projekt nötigen Dateien hinzu:

Unter Project -> Add Copy of Source kopieren Sie die Dateien:

HEX2LEDAX.vhd

MainBasys2.ucf

VERSUCH3.vhd

aus dem Verzeichnis L:/skripte/vollrath/digitaltechnik/Versuch3

in das Projekt.

Alternativ können Sie die obigen Dateien lokal abspeichern und dann hinzufügen.

Die Datei und entity VERSUCH3 wird automatisch als Hauptschaltung (root) erkannt.

|

| 5 | Durch Doppelklick auf VERSUCH3 wird der Quelltext der Datei dargestellt.

Machen Sie sich mit dem Inhalt vertraut.

Zählen Sie hier die Eingänge und Ausgänge auf:

Welcher Schaltungsblock (COMPONENT) wird hier verwendet (Name)?

Wie sind die Eingänge und Ausgänge des Schaltungsblocks verbunden?

|

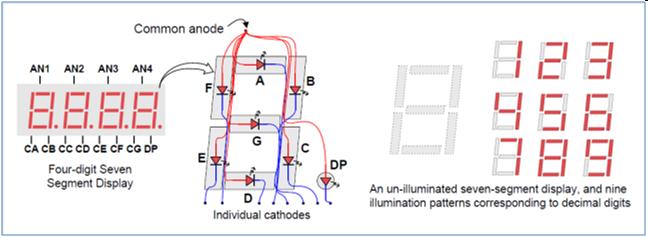

| 6 | Durch Doppelklick auf MainBasys2.ucf wird der Quelltext der Pinbelegungsdatei dargestellt.

Hier werden die Namen der Signale mit den Pins des Bausteins verbunden.

Kommentare werden durch das # Zeichen eingeleitet.

Mit welchem Pin des Bausteins ist dp verbunden?

|

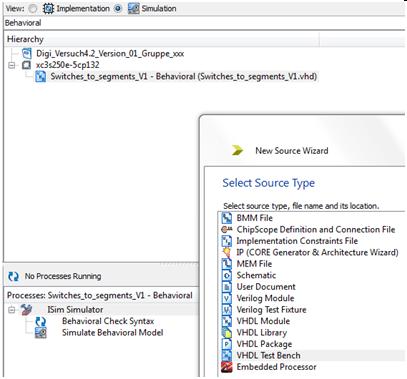

| 7 | Als Erstes soll nun eine Simulation der Digitalschaltung durchgeführt werden.

Dazu wird der View auf Simulation gestellt.

Beobachten Sie wie sich die Darstellung links in der Mitte ändert und neue Werkzeuge gezeigt werden.

Durch Klick auf das Plus Symbol lassen sich Teilwerkzeuge auswählen.

|

| 8 | Erzeugen Sie nun eine neue Simulationsdatei.

Rechtsklick auf Ihr VHDL Modul:

New Source -> VHDL Testbench

Tragen Sie als File name: Test_V3 ein und drücken Sie next.

Bei Associate Source wählen Sie das Modul VERSUCH3 aus. (next, finish)

Es erscheint der Quelltext für die Simulation.

|

| 9 | Einfügen der Testbedingungen, Testvektoren

Suchen Sie die folgende Zeile:

-- insert stimulus here

Dort können Sie nun den zeitlichen Ablauf der Eingänge bestimmen.

Bsp:

sw <= "00000000"; -- Alle Leitungen von sw werden auf 0 gesetzt.

wait for 100 ns; -- Es wird 100 ns gewartet

sw(0) <= '1'; -- Nur die Leitung sw(0) wird auf 1 gesetzt.

wait for 200 ns; -- Es wird 200 ns gewartet

sw(1) <= '1'; -- sw(0) bleibt auf '1' und sw(1) wird auch auf 1 gesetzt.

Fügen Sie genug Zeilen ein, um alle möglichen Kombinationen von sw(3 downto 0)

zu erzeugen.

Kopieren Sie die Zeilen hier hin.

|

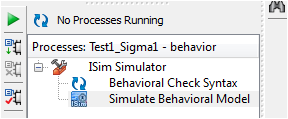

| 10 | Starten Sie die Simulation, indem Sie mit der Maus Test_V3 anwählen.

Im linken mittleren Fenster gibt es nun die Option:

"ISIM Simulator" und nach Klick auf das "+" plus Zeichen "Simulate Behavioral Model".

Durch Doppelklick starten Sie den Simulationsprozess,

der ein zweites Fenster öffnet.

Sie sollten nun ein ähnliches Bild wie unten sehen.

Startet der Simulationsprozess nicht, wird mit der rechten Maustaste über

"Simulate Behavioral Model" "Rerun All" gestartet.

Mit dem Knopf  wird die Grafik auf Fenstergröße skaliert. wird die Grafik auf Fenstergröße skaliert.

Mit dem Knopf  setzen Sie die Simulation zurück. setzen Sie die Simulation zurück.

Mit dem Knopf  simulieren Sie für einen Zeitabschnitt. simulieren Sie für einen Zeitabschnitt.

|

| 11 | Stellen Sie sicher, dass alle Testvektoren sichtbar sind.

Dokumentieren Sie ihr Ergebnis und fügen Sie hier den Screenshot ein:

Remove

Verhalten sich die Eingangssignale "sw" und die Ausgangssignale "led" und "seg" wie erwartet?

|

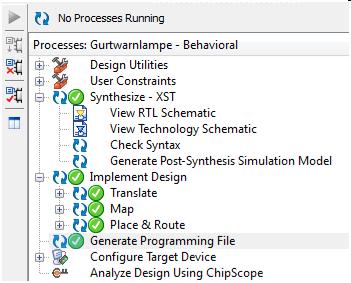

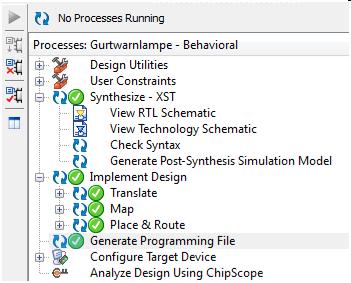

| 12 | Wechseln Sie auf die Ansicht Implementation.

Wählen sie das root Modul gekennzeichnet durch die drei Vierecke aus.

Nun findet sich im mittleren linken Fenster die Option "Generate Programming File".

|

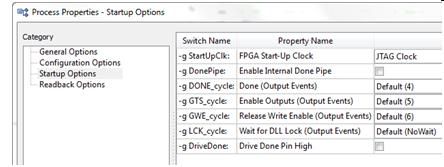

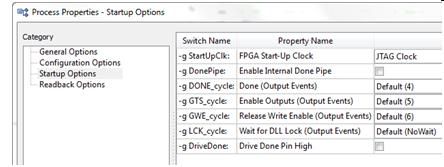

| 13 | Legen Sie einige Optionen fest durch:

Rechts-Click auf Generate Programming File -> Process Properties -> FPGA Start-Up

Clock auf JTAG Clock

|

| 14 | Sie erzeugen nun durch Doppelclick auf die Funktion Generate Programming File das

Programmierfile für das FPGA-Board:

Wie lange dauert es [s], bis dieser Schritt abgeschlossen ist?

Stoppen Sie die Zeit mit der Uhr oder sehen Sie im Design Summary Report nach.

Sie finden nun im Projektverzeichnis eine Datei VERSUCH3.bit,

File, Open, All Files, sortieren nach Typ.

Kopieren Sie diese Datei auf das H: Laufwerk und übertragen

Sie diese im nächsten Schritt zu Ihrem Board.

>

|

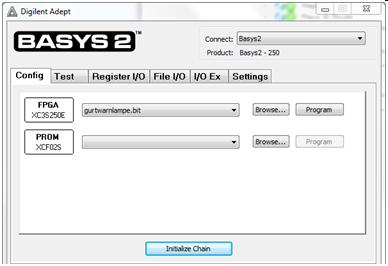

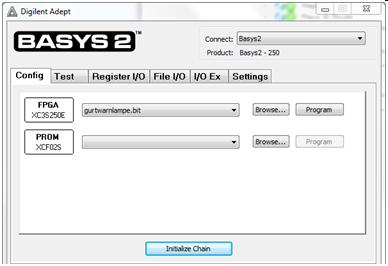

| 15 | Verbinden Sie-falls noch nicht geschehen-, das BASYS 2 board per USB mit dem Rechner.

Starten Sie nun die Software Adept.

Wird Initialize Chain mit der Meldung Initialization complete abgeschlossen,

dann ist die Kommunikation zwischen BASYS 2 und dem Rechner o.k.

Per Browse (obere Zeile) wechseln Sie in ihr Projektverzeichis und laden das .bit File.

Eine Warnung wg. der Startup clock

bestätigen sie mit Ja.

Dann click auf Program und das FPGA ist konfiguriert.

|

| 16 | Testen Sie nun die Funktion.

Setzen Sie die Schiebeschalter und beobachten die Ausgangsfunktion.

Passt alles?

Dokumentieren Sie hier Ihre Testergebnisse mit Wahrheitstabelle und Kommentar.

|

Ihre Daten wurden gesendet.

wird die Grafik auf Fenstergröße skaliert.

wird die Grafik auf Fenstergröße skaliert. setzen Sie die Simulation zurück.

setzen Sie die Simulation zurück. simulieren Sie für einen Zeitabschnitt.

simulieren Sie für einen Zeitabschnitt.