| | Aktion |

| 1 | Starten Sie Xilinx ISE Design Suite.

Click auf "Start/Xilinx Design Tools/ISE Design Suite xx.y/ISE Design tools/xx-bit Project

Navigator".

xx = 64 bei 64-bit OS, xx = 32 bei 32-bit OS.

Wenn ein Projekt offen ist, bitte mit File-> Close Project schließen.

|

| 2 | Laden Sie Ihr Project des vorigen Versuches "File" -> "Open Project".

|

| 3 | Durch einen Doppelklick auf "FUN0 - HEX2LEDAX" öffnen Sie die VHDL Datei HEX2LEDAX.vhd.

Suchen Sie die Zeile für die LED(4).

|

| 4 | Öffnen Sie den Internetbrowser Firefox und suchen Sie nach Segmentanzeige, Wikipedia.

Suche Sie die logische Funktion für Segment E heraus und erstellen Sie den entsprechenden VHDL code.

Dokumentieren Sie hier ihr Ergebnis:

|

| 5 | Simulieren Sie genauso wie im letzten Versuch (Schritt 10) die Funktion.

Stellen Sie sicher, dass alle Testvektoren sichtbar sind.

Dokumentieren Sie ihr Ergebnis und fügen Sie hier den Screenshot ein:

Remove

Verhalten sich die Eingangssignale sw und die Ausgangssignale led und seg wie erwartet?

Wie viele Zählschritte haben Sie simuliert?

|

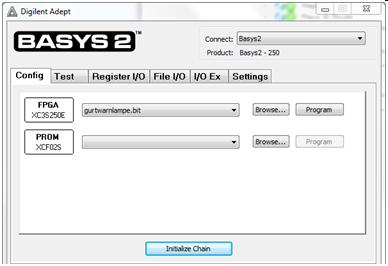

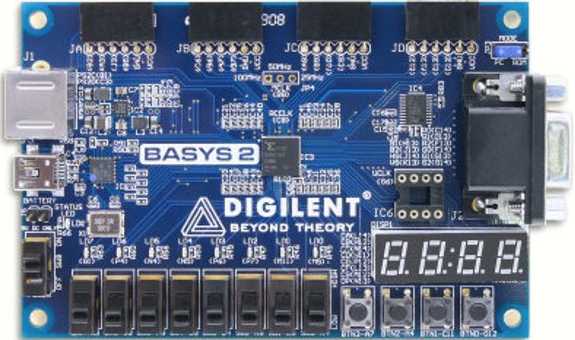

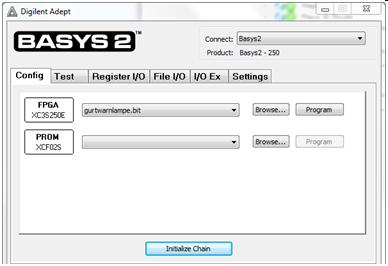

| 6 | Implementieren Sie die Funktion auf dem Basys 2 Board und

testen Sie die Schaltung.

Verbinden Sie-falls noch nicht geschehen-, das BASYS 2 Board per USB mit dem Rechner.

Starten Sie nun die Software Adept .

Wird Initialize Chain mit der Meldung Initialization complete abgeschlossen,

dann ist die Kommunikation zwischen BASYS 2 und dem Rechner o.k.

Per Browse (obere Zeile) wechseln Sie in ihr Projektverzeichis

und laden das .bit File.

Eine Warnung wg. der Startup clock

bestätigen sie mit Ja.

Dann click auf Program und das FPGA ist konfiguriert.

Dokumentieren Sie hier ihr Ergebnis:

|

Erstellung des Schaltplans (schematic) für den Clockteiler

Die 50 MHz Boardtakt werden mit einem Zähler auf 3 Hz zur Buttonabfrage

herunter geteilt.

|

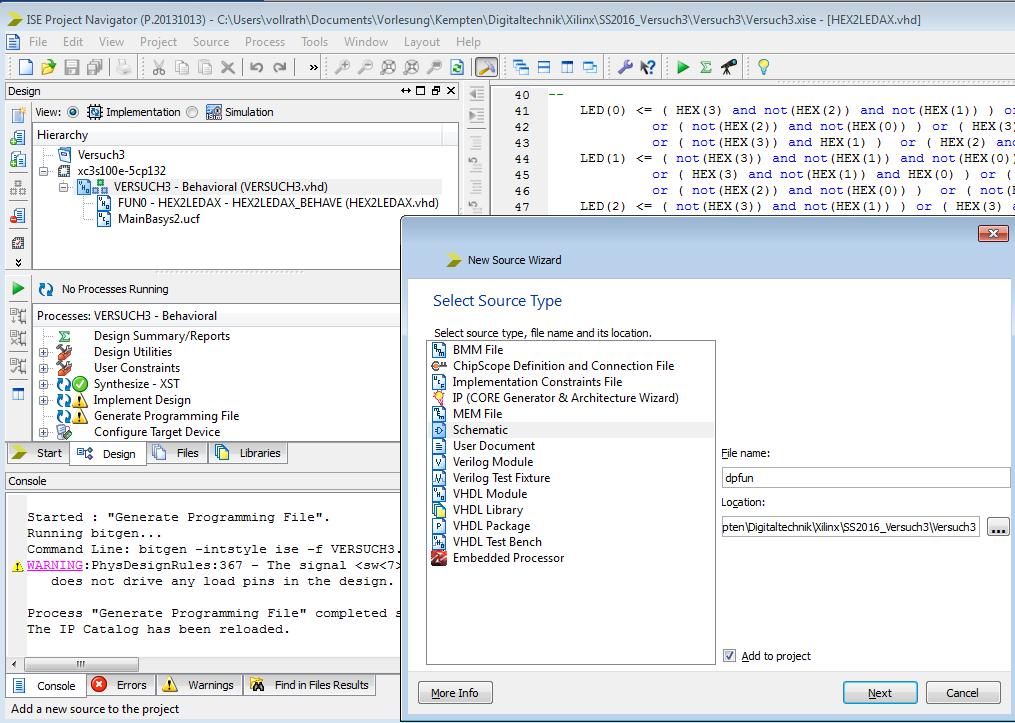

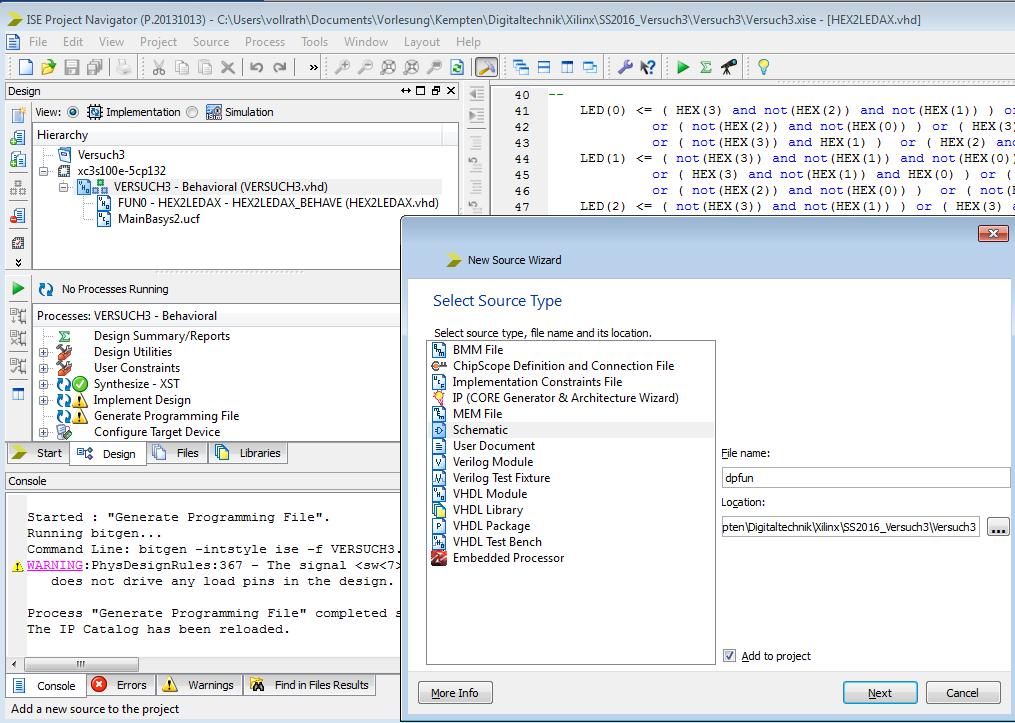

| 7 | Wählen Sie nach Rechtsklick "New Source" -> "Schematic"

Benennen Sie die Schaltung, indem Sie "clkdiv" bei file name eingeben.

Drücken Sie "next" und "finish".

Der Schaltplaneditor erscheint.

|

| 8 | Wählen Sie den Reiter 'Symbols' unter dem linken mittleren Fenster.

Unter dem Punkt 'Categories' wählen Sie 'Counter' aus.

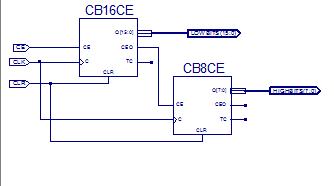

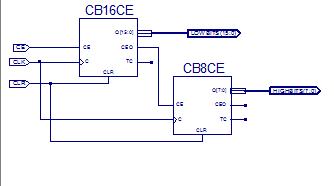

Unter dem Punkt 'Symbols' wählen Sie CB16CE aus und platzieren Sie das Symbol.

Informieren Sie sich durch Klick auf den Schalter "Symbol Info" über die Funktion des Schaltungsblocks.

Unter dem Punkt Symbols wählen Sie dann CB8CE aus und platzieren Sie das Symbol.

Legen Sie Drähte (Verbindungen)  von der Schaltung CB16CE und

erzeugen Sie Eingänge von der Schaltung CB16CE und

erzeugen Sie Eingänge  für CE, CLK ud CLR. für CE, CLK ud CLR.

Eingänge und Ausgänge kann man nur am Ende einer Leitung setzen.

Durch einen Doppelklick auf den Eingang kann man den Namen editieren.

Verbinden Sie den Ausgang CEO von CB16CE mit dem Eingang CE von CB8CE.

Verbinden Sie C und CLR von CB8CE mit den entsprechenden Leitungen von CB16CE.

Erzeugen Sie die Ausgänge LOWBITS(15:0) und HIGHBITS(7:0) (OUTPUT).

Die Schaltung sollte dann folgendermaßen aussehen.

|

VHDL code zum Einbau des Zählers in die Schaltung wird erzeugt.

|

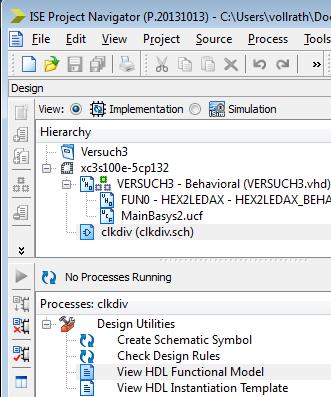

| 9 |

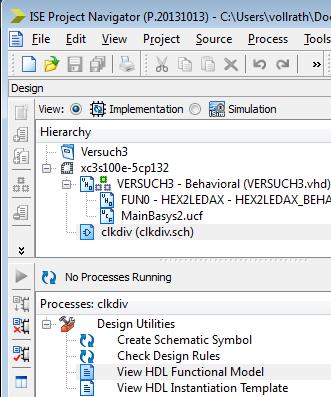

Dazu gehen Sie zum Reiter "Design", wählen clkdiv.sch aus und

erzeugen mit "View HDL Instantiation Template" den zugehörigen VHDL code,

um die Schaltung einzubauen.

|

Bearbeitung von Versuch3.vhd zum Einbau des Zählers.

|

| 10 |

Um clkdiv zu benutzen kopieren Sie nun den Abschnitt COMPONENT in den architecture Abschnitt von VERSUCH3

vor dem 'Begin'.

Der Clockteiler wird in die Schaltung eingebaut indem der Abschnitt UUT:

nach dem 'Begin' hinein kopiert wird und die Eingänge und Ausgänge verbunden werden:

CLK mit CLK, CLR mit btn(0), CE mit '1' und LOWBITS und HIGHBITS mit count24.

LOWBITS => count24( 15 downto 0),

HIGHBITS => count24(23 downto 16)

count24 deklarieren Sie vor dem 'Begin' der architecture als SIGNAL:

SIGNAL count24:STD_LOGIC_VECTOR(23 downto 0);

Damit Sie sehen, wie langsam das oberste Bit des Zählers zählt, verbinden Sie led(7 downto 4) mit

count24(23 downto 20).

led(7 downto 4) <= count24(23 downto 20) ;

und ändern die Zeilen

led(6 downto 1) <= sw (6 downto 1);

led(7) <= clk;

zu

led(3 downto 1) <= sw (3 downto 1);

--led(7) <= clk;

Damit es keine doppelte Ansteuerung (Kurzschluss) von led(7 downto 4) gibt.

|

| 11 |

Die btn Eingänge werden oben in der entity im Abschnitt port eingefügt:

btn: in STD_LOGIC_VECTOR ( 3 downto 0);

|

Bearbeitung von MainBasys2.ucf zum Einbau des Zählers.

|

| 12 | Außerdem werden die btn Eingänge in der UCF Datei durch löschen der Kommentarzeichen # aktiviert.

|

Bearbeitung von Versuch3.vhd zur Implementierung einer Zustandsmaschine für die

Taster (Buttons).

|

| 13 | Mit der Taste btn(1) soll nun dp ein und ausgeschaltet werden.

Die Signalanweisung kommt vor das begin der architecture:

SIGNAL dpi:STD_LOGIC;

Der process für die Zustandsmaschine wird nach dem begin eingefügt.

process(CLK,btn(0),btn(1))

begin

if ( btn(0) = '1') then -- asynchron reset with button 0

dpi <= '0';

elsif (rising_edge(clk) and (count24(21 downto 0)="1000000000000000000000")) then

if (btn(1) = '1') then

dpi <= not(dpi);

end if;

end if;

end process;

dp <= dpi;

Die letzte Zeile ersetzt dp <= sw(7);.

|

Bearbeitung von Test_V3.vhd zum Test der Schaltung.

|

| 14 | Da die entity geändert wurde, muss auch die Simulationsdatei angepasst werden:

Ansicht: Simulation, dann Auswahl der Testdatei Test_V3.vhd

Im Abschnitt component VERSUCH 3 wird die Zeile für die Buttons eingefügt:

btn: in STD_LOGIC_VECTOR ( 3 downto 0);

Entsprechend benötigt man ein Signal im --Inputs Bereich:

signal btn : std_logic_vector(3 downto 0):= (others => '0');

und die Unit under test UUT: muss ergänzt werden:

btn => btn,

Nun ergänzen Sie noch die Testvektoren am Anfang durch kurzzeitiges setzen des btn(0) auf '1',

um den Zähler zu initialisieren, und danach langes setzen des btn(1) auf '1' und btn(0) auf '0'.

Simulieren Sie genauso wie im letzten Versuch (Schritt 10) die Funktion.

Sie untersuchen, ob count24 richtig zählt, der Taster abgefragt wird und dp sich ändert.

count24 finden Sie, wenn sie die Testschaltung durch Klick auf das Dreieck aufklappen.

Remove

Verhält sich die Simulation wie erwartet? Gibt es Schwierigkeiten?

|

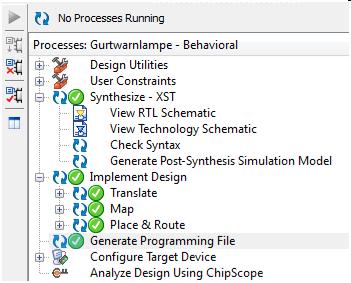

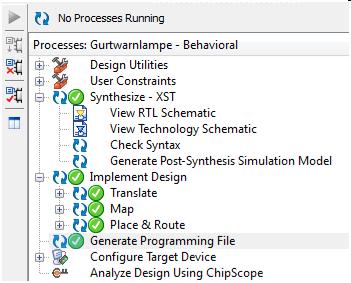

| 15 | Sie erzeugen nun durch Click auf die Funktion Generate Programming File das

Programmierfile für das FPGA-Board:

Sie finden nun im Projektverzeichnis eine Datei VERSUCH3.bit.

File, Open, All Files, sortieren nach Typ.

Kopieren Sie diese Datei auf das H: Laufwerk und übertragen

Sie diese im nächsten Schritt zu Ihrem Board.

|

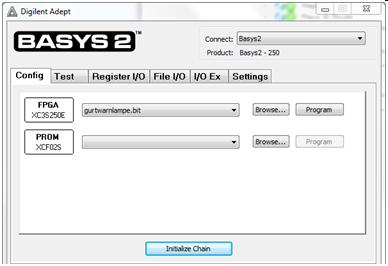

| 16 | Verbinden Sie-falls noch nicht geschehen-, das BASYS 2 Board per USB mit dem Rechner.

Starten Sie nun die Software Adept .

Wird Initialize Chain mit der Meldung Initialization complete abgeschlossen,

dann ist die Kommunikation zwischen BASYS 2 und dem Rechner o.k.

Per Browse (obere Zeile) wechseln Sie in ihr Projektverzeichis und laden das .bit File.

Eine Warnung wg. der Startup clock

bestätigen sie mit Ja.

Dann click auf Program und das FPGA ist konfiguriert.

|

| 17 | Testen Sie nun die Funktion.

Drücken Sie den Taster und beobachten Sie den Anzeigepunkt dp.

Passt alles? Gratuliere

!

Kommentieren Sie hier das Ergebnis.

|

Ihre Daten wurden gesendet.

von der Schaltung CB16CE und

erzeugen Sie Eingänge

von der Schaltung CB16CE und

erzeugen Sie Eingänge  für CE, CLK ud CLR.

für CE, CLK ud CLR.