| | Aktion |

| 1 | Starten Sie Xilinx Vivado.

Click auf "Vivado 2019.1".

|

| 2 | Bei Bedarf kopieren Sie ihr Projektverzeichnis vom USB Stick in ein lokales Verzeichnis.

Laden Sie Ihr Project des vorigen Versuches "File" -> "Open Project".

|

| 3 | Durch einen Doppelklick auf "FUN0 - HEX2LEDAX" öffnen Sie die VHDL Datei HEX2LEDAX.vhd.

Suchen Sie die Zeile für die LED(4).

|

| 4 | Öffnen Sie den Internetbrowser Firefox und suchen Sie nach Segmentanzeige, Wikipedia.

Suche Sie die logische Funktion für Segment E heraus und erstellen Sie den entsprechenden VHDL code.

Dokumentieren Sie hier ihr Ergebnis:

|

| 5 | Simulieren Sie genauso wie im letzten Versuch die Funktion.

Linke Spalte: Simulation -> Run Simulation

Stellen Sie sicher, dass alle Testvektoren sichtbar sind.

Dokumentieren Sie ihr Ergebnis und fügen Sie hier den Screenshot ein:

Remove

Verhalten sich die Eingangssignale sw und die Ausgangssignale led und seg wie erwartet?

Wie viele Zählschritte haben Sie simuliert?

|

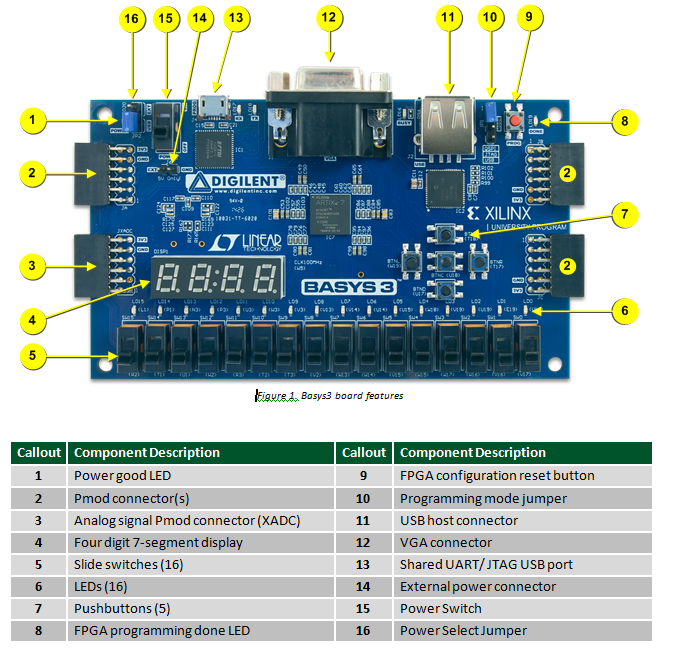

| 6 | Implementieren Sie die Funktion auf dem Basys 3 Board und

testen Sie die Schaltung.

Linke Spalte: Synthesis -> Run Synthesis

Linke Spalte: Implementation -> Run Implementation

Linke Spalte: Program and Debug -> Generate Bitstream

Verbinden Sie-falls noch nicht geschehen-, das BASYS 3 Board per USB mit dem Rechner.

Linke Spalte: Program and Debug -> Open Hardware Manager

Erstmalig: -> Open Target

Danach: -> Program Device

Dokumentieren Sie hier ihr Ergebnis:

|

Erstellung eines Zählers mit dem IP Catalog

Die 100 MHz Boardtakt werden mit einem Zähler auf eine niedrige Frequenz zur Tastenabfrage

herunter geteilt.

|

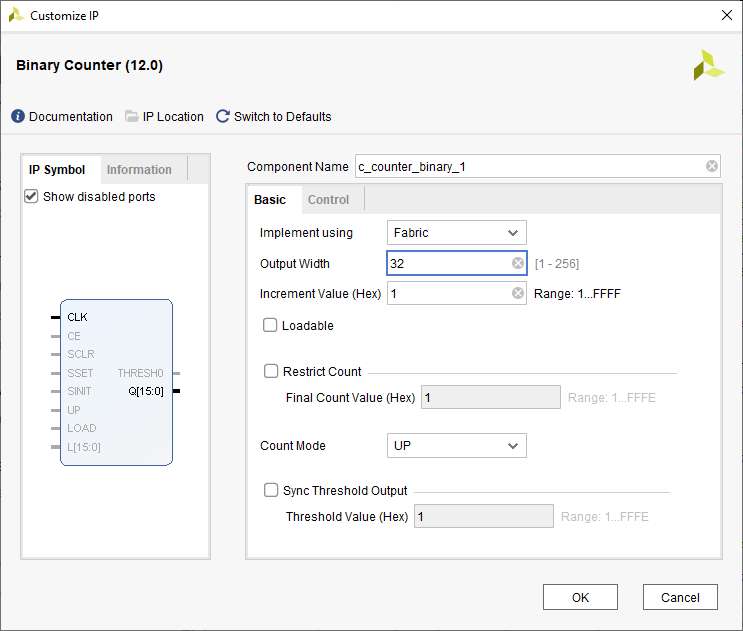

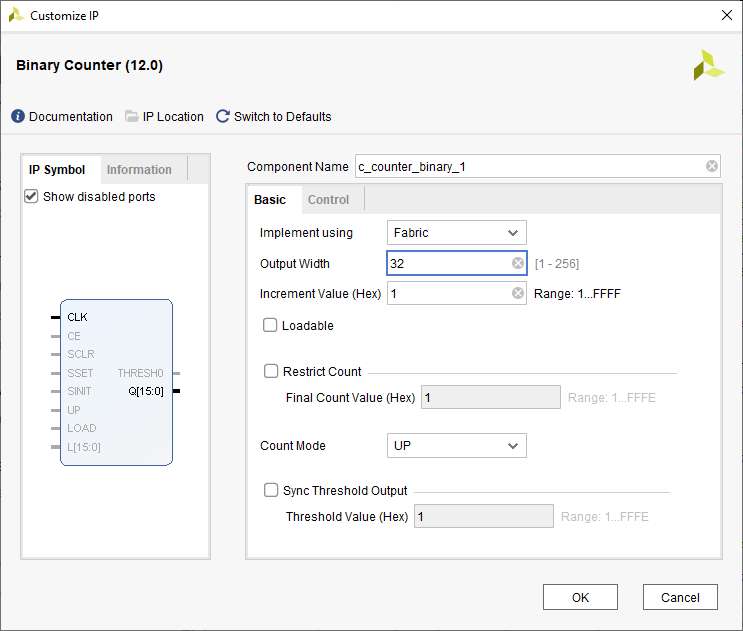

| 7 | Linke Spalte: Project Manager ->IP Catalog

Im Feld search geben sie "counter" ein, um nach einem Zähler zu suchen.

Durch Doppelcklick auf binary counter erscheint das Fenster "Customize IP"

Hier haben Sie die Möglichkeit den Zähler zu konfigurieren.

Wählen Sie Output Width 32

Click "ok". Click "generate".

|

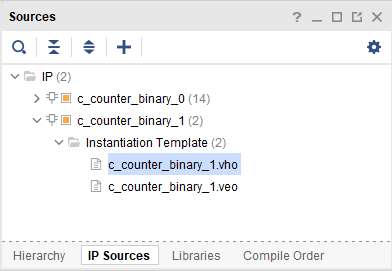

VHDL code zum Einbau des Zählers in die Schaltung wird ausgewählt.

|

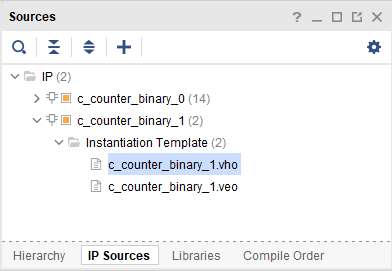

| 8 | Im Unterfenster Sources wähen Sie unten IP Sources und klappen dann den counter auf,

um die Instantiation Templates auswählen zu können.

|

Bearbeitung von Versuch3.vhd zum Einbau des Zählers.

|

| 9 |

Um c_counter_binary_0 zu benutzen kopieren Sie nun den Abschnitt COMPONENT in den architecture Abschnitt von VERSUCH3

vor dem 'Begin'.

Der Clockteiler wird in die Schaltung eingebaut in dem der Abschnitt UUT:

nach dem 'Begin' hinein kopiert wird und die Eingänge und Ausgänge verbunden werden:

CLK mit CLK, CE mit sw(7) und Q mit count.

Dazu muss das signal count noch vor dem begin definiert werden.

architecture Behavioral of VERSUCH3 is

COMPONENT HEX2LEDAX

PORT(

hex : in std_logic_vector (3 downto 0);

ledn: out std_logic_vector (6 downto 0)

);

END COMPONENT;

COMPONENT c_counter_binary_0

PORT (

CLK : IN STD_LOGIC;

CE : IN STD_LOGIC;

Q : OUT STD_LOGIC_VECTOR(31 DOWNTO 0)

);

END COMPONENT;

signal count: STD_LOGIC_VECTOR(31 DOWNTO 0);

begin

clk_div : c_counter_binary_0

PORT MAP (

CLK => CLK,

CE => sw(7),

Q => count

);

Damit Sie sehen, wie langsam das oberste Bit des Zählers zählt, verbinden Sie led(10 downto 6) mit

count(26 downto 22).

Erweitern Sie in der Datei Versuch3.vhd im Abschnitt entity den led-Bus (10 downto 0).

Die led pins 10..6 müssen in der constraints Datei Basys3_Master.xdc aktiviert werden

(Entfernen des '#' Kommentarzeichens).

led(4 downto 0) <= sw (4 downto 0);

led(5) <= clk;

led(10 downto 6) <= count(26 downto 22);

-- dp <= not sw(4);

an <= "1110";

|

| 11 |

Die btn Eingänge werden oben in der entity im Abschnitt port eingefügt:

btn: in STD_LOGIC_VECTOR ( 3 downto 0);

|

Bearbeitung von Basys3_Master.xdc zum Einbau des Zählers.

|

| 12 | Außerdem werden die btn Eingänge in der Basys3_Master.xdc Datei durch löschen der Kommentarzeichen # aktiviert.

|

Bearbeitung von Versuch3.vhd zur Implementierung einer Zustandsmaschine für die

Taster (Buttons).

|

| 13 | Mit der Taste btn(1) soll nun dp ein und ausgeschaltet werden.

Die Signalanweisung kommt vor das begin der architecture:

SIGNAL dpi:STD_LOGIC;

Der process für die Zustandsmaschine wird nach dem begin eingefügt.

process(CLK,btn(0),btn(1))

begin

if ( btn(0) = '1') then -- asynchron reset with button 0

dpi <= '0';

ce <= '0';

elsif (rising_edge(clk)) then

if (count(23 downto 0)="100000000000000000000000") then

ce <= '1';

if (btn(1) = '1') then

dpi <= not(dpi);

end if;

else

ce <= '0';

end if;

end if;

end process;

dp <= dpi;

Wir benötigen den process, um eine Zustandsmaschine zu bauen.

Zeile 4: Die erste if Anweisung initialisiert dpi und ce asynchron, wenn btn(0) gedrückt wird.

Zeile 7: "elsif" definiert die Aktionen bei einer steigenden clk Flanke.

Zeile 8: Nur wenn der Zähler einen bestimmten Wert hat wird ce gesetzt (Zeile 9) und dpi invertiert (Zeile 10).

Zeile 13-15: ce wird auf "0" zurück gesetzt und ist nur einen clk Zyklus aktiv.

Die letzte Zeile ersetzt die Zeile "dp <= sw(7);".

Zustandsmaschinen in VHDL sehen immer ähnlich aus. im nächsten Versuch wird ausgehend von diesem process ein

weiterer für btn(2) und btn(3) eingefügt.

|

Bearbeitung von Test_V3.vhd zum Test der Schaltung.

|

| 14 | Da die entity geändert wurde, muss auch die Simulationsdatei angepasst werden:

Ansicht: Simulation, dann Auswahl der Testdatei Test_V3.vhd

Im Abschnitt component VERSUCH 3 wird die Zeile für die Buttons eingefügt:

btn: in STD_LOGIC_VECTOR ( 3 downto 0);

Die led wird auf die Anzahl (10 downto 0) erweitert.

Entsprechend benötigt man ein Signal im --Inputs Bereich:

signal btn : std_logic_vector(3 downto 0):= (others => '0');

Auch drot wird der Bereich für led angepasst.

Die Unit under test UUT: muss ergänzt werden:

btn => btn,

Nun ergänzen Sie noch die Testvektoren am Anfang durch kurzzeitiges setzen des btn(0) auf '1',

um den Zähler zu initialisieren, und danach langes setzen des btn(1) auf '1' und btn(0) auf '0'.

Simulieren Sie genauso wie im letzten Versuch die Funktion.

Sie untersuchen, ob count richtig zählt, der Taster abgefragt wird und dp sich ändert.

count finden Sie, wenn sie die Testschaltung durch Klick auf das Dreieck aufklappen.

Remove

Verhält sich die Simulation wie erwartet? Gibt es Schwierigkeiten?

|

| 15 | Klicken Sie dafür auf Generate Bitstream und warten Sie bis die Datei erzeugt

wurde (drehendes grünes Rad oben rechts).

Sollte dort kein grüner Haken erscheinen, dann haben Sie einen Fehler im

Quellcode.

Falls kein Fehler erscheint können Sie weitermachen, ansonsten bessern Sie den

Fehler aus.

Falls das Basys3 Board nicht am PC angesteckt und angeschaltet sein sollte, so

machen Sie das.

Drücken Sie auf Open Hardware Manager -> Open Target -> Auto Connect. Warten Sie

bis sich das Fenster geschlossen hat.

Anschließenend drücken Sie auf Program Device -> xc7a35t_0.

Im neuen Fenster bestätigen Sie mit Program.

|

| 17 | Testen Sie nun die Funktion.

Drücken Sie den Taster und beobachten Sie den Anzeigepunkt dp.

Passt alles? Gratuliere

!

Kommentieren Sie hier das Ergebnis.

|

Ihre Daten wurden gesendet.