generic(

ADDR_WIDTH: integer := 16;

DATA_WIDTH: integer:= 16

);

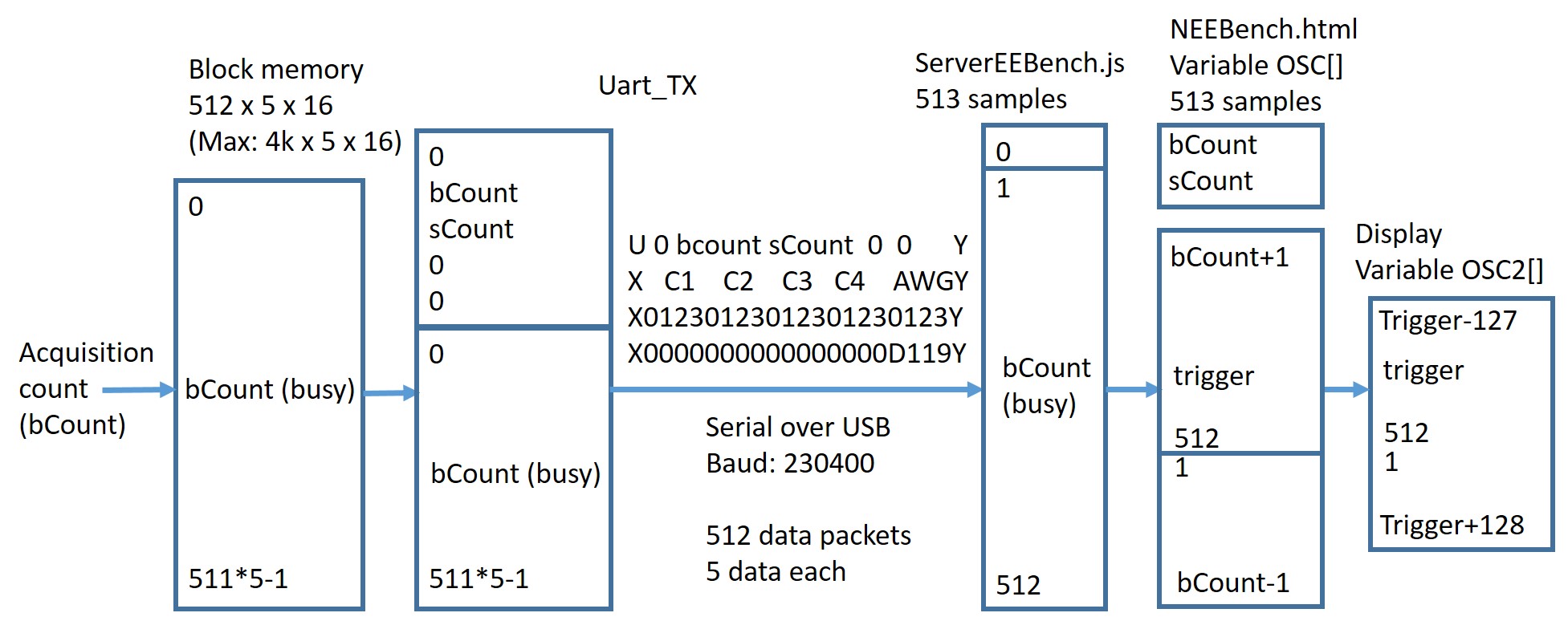

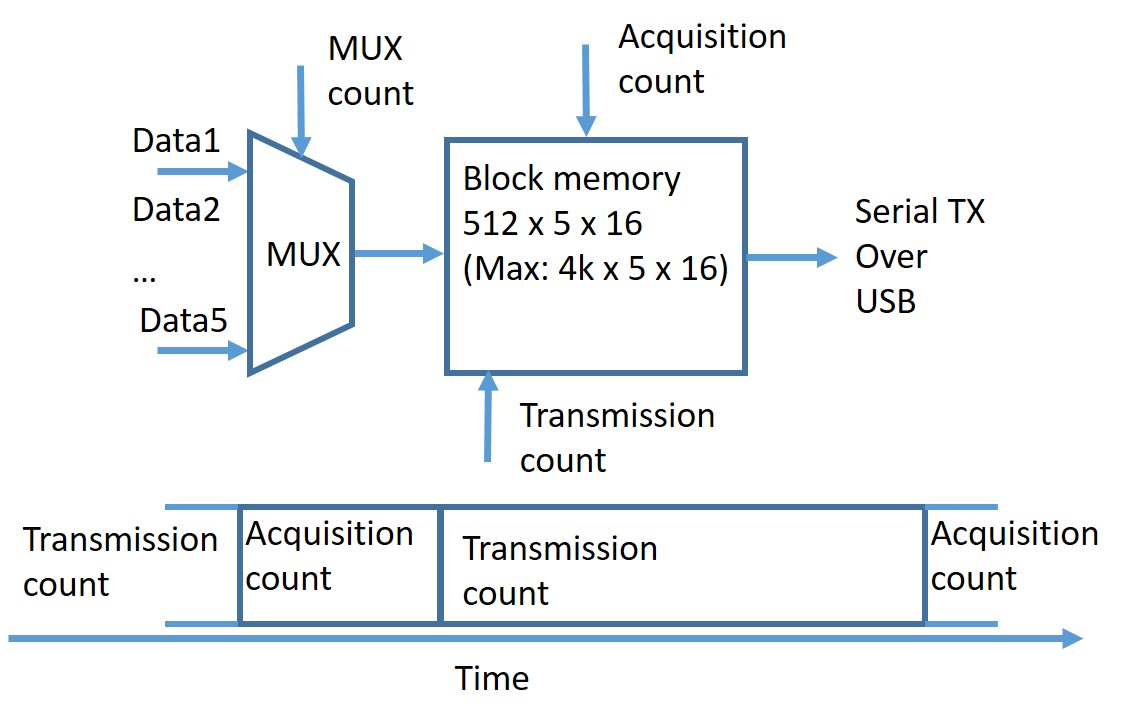

In EEBench the process storeMem controls data acquisition.

elsif (rising_edge(CLK) and (readyX = '1')

-- slow clock ??

and (upSample = '1')

) then -- continous cycling through ADC if no transmit

if (tx_busy = '1') then -- transfer started

sCnt := 0;

we <='0';

else -- data sampling

case source is

tx_busy prevents acquisition and memory write during ongoing serial transmission to the PC.