Begleitende Übungen Digitaltechnik

|

Übung 1: Schaltungen, Gleichungen und Wahrheitstabellen

Übung 1 Aufgabe 1:

|

Bestimmen Sie die logische Gleichung und die Wahrheitstabelle folgender Schaltung. |

Übung 1 Aufgabe 2:

|

Bestimmen Sie die logische Gleichung und die Wahrheitstabelle folgender Schaltung. |

Übung 1 Aufgabe 3 Digitaltechnik Logikfunktion und Wahrheitstafel

Geben Sie für die folgende Wahrheitstabelle mit den Eingängen X3, X2, X1 und X0 und den Ausgängen Y1 und Y0 die disjunktive Normalform an.

| X3 | X2 | X1 | X0 | Y1 | Y0 |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | D |

| 0 | 1 | 1 | 1 | 0 | D |

| 1 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | D | D |

| 1 | 1 | 0 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 0 | 1 |

Übung 1 Aufgabe 4

Erstellen Sie für folgenden VHDL Code die Wahrheitstabelle und einen Schaltplan

entity ThisCircuit is port (

vin1,vin2, vin3, vin4 : in STD_LOGIC;

vout : out STD_LOGIC);

end ThisCircuit;

architecture Behavioral of ThisCircuit is

begin

vout <= ((vin1 and vin2 ) or (not vin3)) and vin4

end Behavioral;

Übung 1 Aufgabe 5:

|

Bestimmen Sie die Wahrheitstabelle folgender Schaltung. |

Übung 1 Aufgabe 6:

|

Bestimmen Sie die Wahrheitstabelle folgender Schaltung. |

Übung 2: Zeitverhalten logischer Schaltungen

Übung 2 Aufgabe 1:

Zeichnen Sie das Zeitverhalten folgender Schaltung:

Übung 2 Aufgabe 2:

Zeichnen Sie das Zeitverhalten folgender Schaltung mit einer Verzögerungszeit pro Gatter von 5ns:

Übung 3: Zustandsmaschinen

Übung 3 Aufgabe 1: Fussgängerampel

Eine digitale Schaltung für eine Bedarfsfussgängerampel soll entworfen werden.

Drückt man auf einen Schalter gehen die Ampeln für Fussgänger und Autos an. Nach einiger Zeit wird die Fussgängerampel grün und dann nach einiger Zeit wieder Rot.

Bestimmen Sie die Eingänge und Ausgänge.

Erstellen Sie eine Zustandstabelle.

Übung 3 Aufgabe 2: Leuchtball

Ein Leuchtball hat einen Knopf und 3 farbige LEDs.

Durch Drücken des Knopfes soll der Ball den Zustand wechseln von "Aus" zu "Rot"

zu "Grün" zu "Blau" zu "Aus". Bestimmen Sie die Eingänge und Ausgänge.

Erstellen Sie eine Zustandstabelle.

Übung 4: VHDL Beschreibungen

Übung 4 Aufgabe 1:

Erstellen Sie für folgenden VHDL Code die Wahrheitstabelle und einen Schaltplan

entity ThisCircuit is port (

vin1,vin2, vin3, vin4 : in STD_LOGIC;

vout : out STD_LOGIC);

end ThisCircuit;

architecture Behavioral of ThisCircuit is

begin

vout <= ((vin1 and vin2 ) or (not vin3)) and vin4

end Behavioral;

Übung 4 Aufgabe 2:

Folgender VHDL code für eine Simulation ist gegeben.

y <="00"; wait for 100 ns;

x2 <='0'; wait for 50 ns;

x1 <='0'; wait for 100 ns;

x2 <='1'; wait for 50 ns;

x1 <='1'; wait for 10 ns;

x2 <='1'; wait for 50 ns;

x1 <='1'; wait for 10 ns;

x2 <='1'; wait for 50 ns;

x2 <='0'; wait for 20 ns;

x2 <='1'; wait for 50 ns;

x1 <='0'; wait for 10 ns;

x2 <='0'; wait for 20 ns;

Wie lange ist x1 gedrückt ('1')?

Wie oft wird x2 gedrückt ('1')?

Wann verwenden Sie einfache Hochkomma ' und wann Anführungszeichen "?

Übung 4 Aufgabe 3:

Erstellen Sie für folgenden VHDL-Code die Wahrheits-/Zustandstabelle:

entity ThisCircuit is port (

vec1, vec2 : in STD_LOGIC;

op: in STD_LOGIC_VECTOR (1 downto 0);

vout : out STD_LOGIC_VECTOR (1 downto 0);

end ThisCircuit;

architecture Behavioral of ThisCircuit is

signal acc:STD_LOGIC_VECTOR (1 downto 0);

begin

PROCESS (op)

BEGIN

CASE op IS

WHEN "00" => acc(1) <= vec1; acc(0) <= vec2;

WHEN "01" => acc(1) <= vec2; acc(0) <= vec1;

WHEN "10" => acc(1) <= vec1 and vec2;

acc(0) <= vec1 or vec2;

WHEN "11" => acc(1) <= vec1 xor vec2;

acc(0) <= '0';

WHEN OTHERS => acc<="00";

END CASE;

END PROCESS;

vout <= acc;

end Behavioral;

Übung 4 Aufgabe 4:

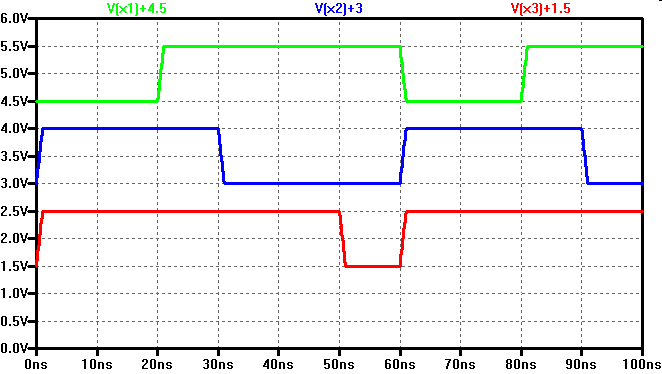

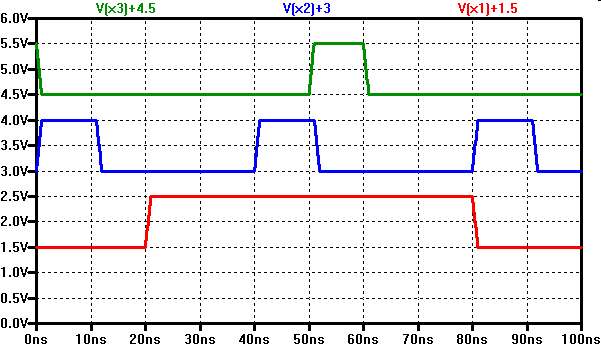

Stellen Sie das Zeitverhalten der Signale dar, die mit folgendem VHDL code erzeugt werden.

constant Tp : time := 40 ns;

stim_proc: process

begin

op <= "01"; vec1 <='0'; vec2 <='1'; wait for Tp;

op <= "11"; vec1 <='1'; vec2 <='0'; wait for 2*Tp;

op <= "00"; vec1 <='0'; vec2 <='0'; wait for Tp;

op <= "10"; vec1 <='1'; vec2 <='0'; wait for 2*Tp;

op <= "11"; vec1 <='1'; vec2 <='1'; wait for Tp;

end process;

entity ThisCircuit is port ( vin1,vin2, vin3, vin4 : in STD_LOGIC; vout : out STD_LOGIC); end ThisCircuit; architecture Behavioral of ThisCircuit is begin vout <= ((vin1 and vin2 ) or (not vin3)) and vin4 end Behavioral;

y <="00"; wait for 100 ns;

x2 <='0'; wait for 50 ns;

x1 <='0'; wait for 100 ns;

x2 <='1'; wait for 50 ns;

x1 <='1'; wait for 10 ns;

x2 <='1'; wait for 50 ns;

x1 <='1'; wait for 10 ns;

x2 <='1'; wait for 50 ns;

x2 <='0'; wait for 20 ns;

x2 <='1'; wait for 50 ns;

x1 <='0'; wait for 10 ns;

x2 <='0'; wait for 20 ns;

Wie lange ist x1 gedrückt ('1')?Wie oft wird x2 gedrückt ('1')?

Wann verwenden Sie einfache Hochkomma ' und wann Anführungszeichen "?

Übung 4 Aufgabe 3:

Erstellen Sie für folgenden VHDL-Code die Wahrheits-/Zustandstabelle:

entity ThisCircuit is port (

vec1, vec2 : in STD_LOGIC;

op: in STD_LOGIC_VECTOR (1 downto 0);

vout : out STD_LOGIC_VECTOR (1 downto 0);

end ThisCircuit;

architecture Behavioral of ThisCircuit is

signal acc:STD_LOGIC_VECTOR (1 downto 0);

begin

PROCESS (op)

BEGIN

CASE op IS

WHEN "00" => acc(1) <= vec1; acc(0) <= vec2;

WHEN "01" => acc(1) <= vec2; acc(0) <= vec1;

WHEN "10" => acc(1) <= vec1 and vec2;

acc(0) <= vec1 or vec2;

WHEN "11" => acc(1) <= vec1 xor vec2;

acc(0) <= '0';

WHEN OTHERS => acc<="00";

END CASE;

END PROCESS;

vout <= acc;

end Behavioral;

Übung 4 Aufgabe 4:

Stellen Sie das Zeitverhalten der Signale dar, die mit folgendem VHDL code erzeugt werden.

constant Tp : time := 40 ns;

stim_proc: process

begin

op <= "01"; vec1 <='0'; vec2 <='1'; wait for Tp;

op <= "11"; vec1 <='1'; vec2 <='0'; wait for 2*Tp;

op <= "00"; vec1 <='0'; vec2 <='0'; wait for Tp;

op <= "10"; vec1 <='1'; vec2 <='0'; wait for 2*Tp;

op <= "11"; vec1 <='1'; vec2 <='1'; wait for Tp;

end process;

entity ThisCircuit is port (

vec1, vec2 : in STD_LOGIC;

op: in STD_LOGIC_VECTOR (1 downto 0);

vout : out STD_LOGIC_VECTOR (1 downto 0);

end ThisCircuit;

architecture Behavioral of ThisCircuit is

signal acc:STD_LOGIC_VECTOR (1 downto 0);

begin

PROCESS (op)

BEGIN

CASE op IS

WHEN "00" => acc(1) <= vec1; acc(0) <= vec2;

WHEN "01" => acc(1) <= vec2; acc(0) <= vec1;

WHEN "10" => acc(1) <= vec1 and vec2;

acc(0) <= vec1 or vec2;

WHEN "11" => acc(1) <= vec1 xor vec2;

acc(0) <= '0';

WHEN OTHERS => acc<="00";

END CASE;

END PROCESS;

vout <= acc;

end Behavioral;

constant Tp : time := 40 ns;

stim_proc: process

begin

op <= "01"; vec1 <='0'; vec2 <='1'; wait for Tp;

op <= "11"; vec1 <='1'; vec2 <='0'; wait for 2*Tp;

op <= "00"; vec1 <='0'; vec2 <='0'; wait for Tp;

op <= "10"; vec1 <='1'; vec2 <='0'; wait for 2*Tp;

op <= "11"; vec1 <='1'; vec2 <='1'; wait for Tp;

end process;

Übung 5: Verständnisfragen

Was ist ein zeitdiskretes Signal?

Was ist ein wertdiskretes Signal?

Wie messen Sie eine Verzögerungszeit?

An welchen Grundschaltungen können Setup-Zeiten auftreten?

Wodurch wird die maximale Frequenz einer Digitalschaltung begrenzt?

Sie erhalten bei einer VHDL Simulation nur undefinierte Signale.

Was ist passiert?

Sie erhalten bei einer VHDL Simulation ein paar undefinierte Signale.

Was ist passiert?

Sie erhalten bei einer VHDL Simulation ein Signal mit dem Wert X.

Was ist passiert?

Welche Zustände kann der VHDL Typ STD_LOGIC annehmen?

Was ist der Unterschied zwischen einem Schaltnetz und einem Schaltwerk?

Was ist der Unterschied zwischen einem RAM, SRAM und Flashspeicher?

Was ist der Unterschied zwischen einer asynchronen und synchronen Digitalschaltung?

Was ist eine Setup Zeit? Welche Signale bestimmen die Setup Zeit? Bei welchen Pegeln wird die Setupzeit gemessen?

Was ist ein Dual-Port-RAM? Welche Eingänge und Ausgänge hat es und welche Funktion erfüllt es?

Was ist ein FIFO? Welche Eingänge und Ausgänge hat es und welche Funktion erfüllt es?

Was ist ein UART? Welche Eingänge und Ausgänge hat es und welche Funktion erfüllt es?

Klausur SS2013:

SS2013 Aufgabe 1:

1. Erstellen Sie für folgenden VHDL-Code die Wahrheits-/Zustandstabelle:

entity ThisCircuit1 is port (

a: in STD_LOGIC_VECTOR (1 downto 0);

b : in STD_LOGIC;

y: out STD_LOGIC;

clk: in STD_LOGIC);

end ThisCircuit1;

architecture Behavioral of ThisCircuit1 is

signal xy:STD_LOGIC;

begin

PROCESS (clk)

BEGIN

if (clk='1' and clk'event) then

CASE a IS

WHEN "00" => xy<=xy and b;

WHEN "01" => xy<=a(0) or b;

WHEN "10" => xy<=b and xy;

WHEN "11" => xy<=a(1) and b;

WHEN OTHERS => xy<='0';

END CASE;

end if;

END PROCESS;

y <= xy or b;

end Behavioral;

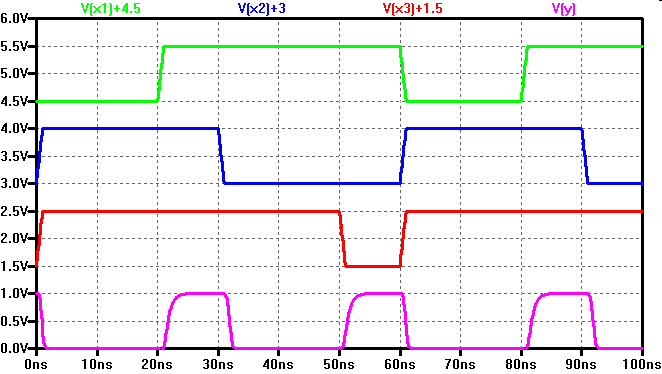

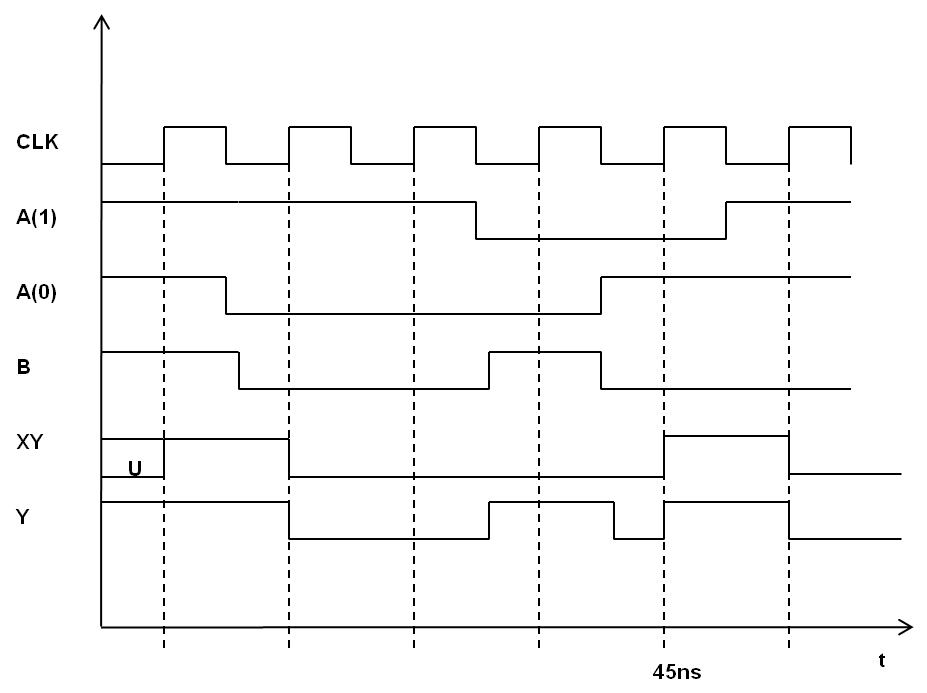

2. Geben Sie das Zeitverhalten der Signale clk, a, b, xy und y für folgenden

VHDL Stimulus für die Schaltung ThisCircuit1 an. (8 Punkte)

constant Tp : time := 10 ns;

clk_process :process

begin

clk <= '0'; wait for Tp/2;

clk <= '1'; wait for Tp/2;

end process;

stim_proc: process

begin

a <= "11"; b <='1'; wait for Tp;

a <= "10"; b <='0'; wait for 2*Tp;

a <= "00"; b <='1'; wait for Tp;

a <= "01"; b <='0'; wait for Tp;

a <= "11"; b <='0'; wait for Tp;

end process;

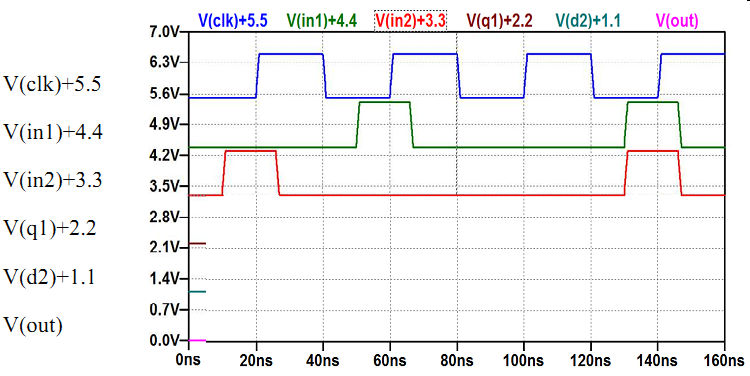

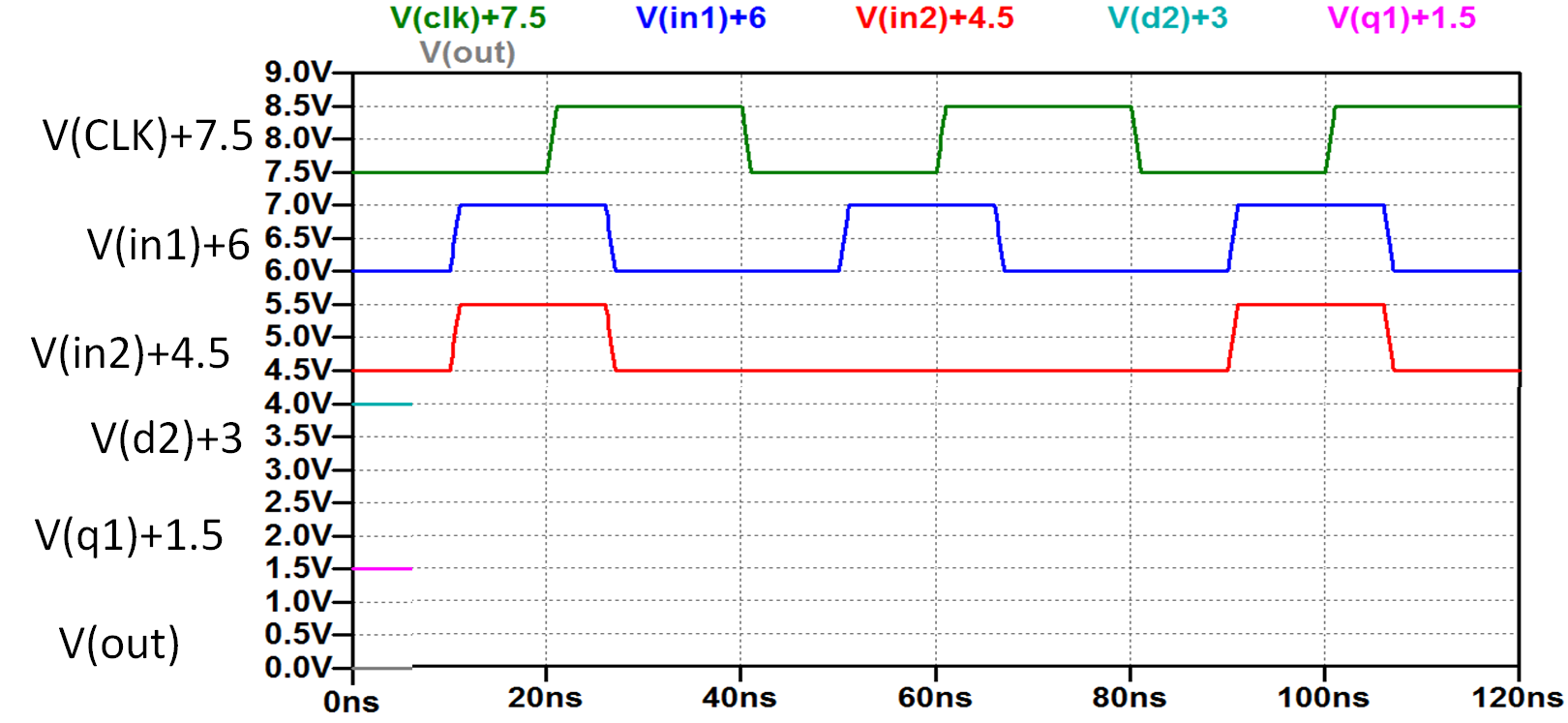

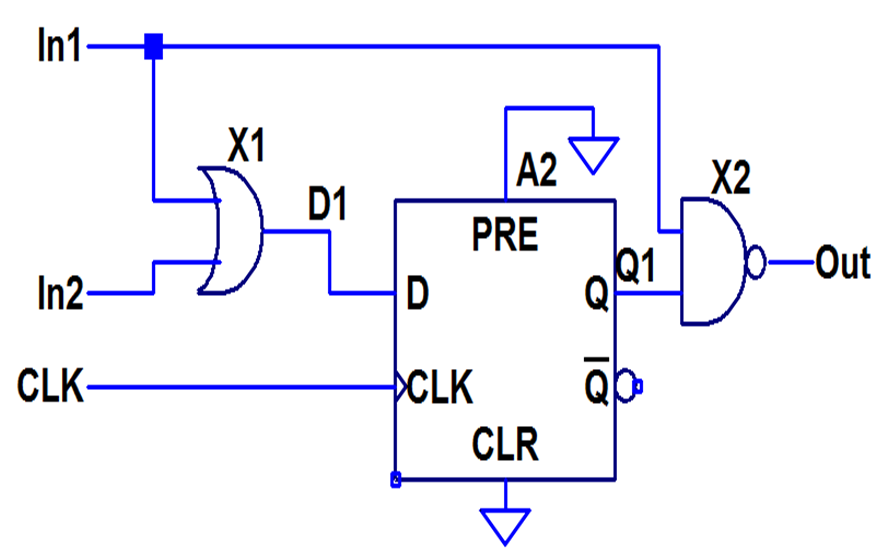

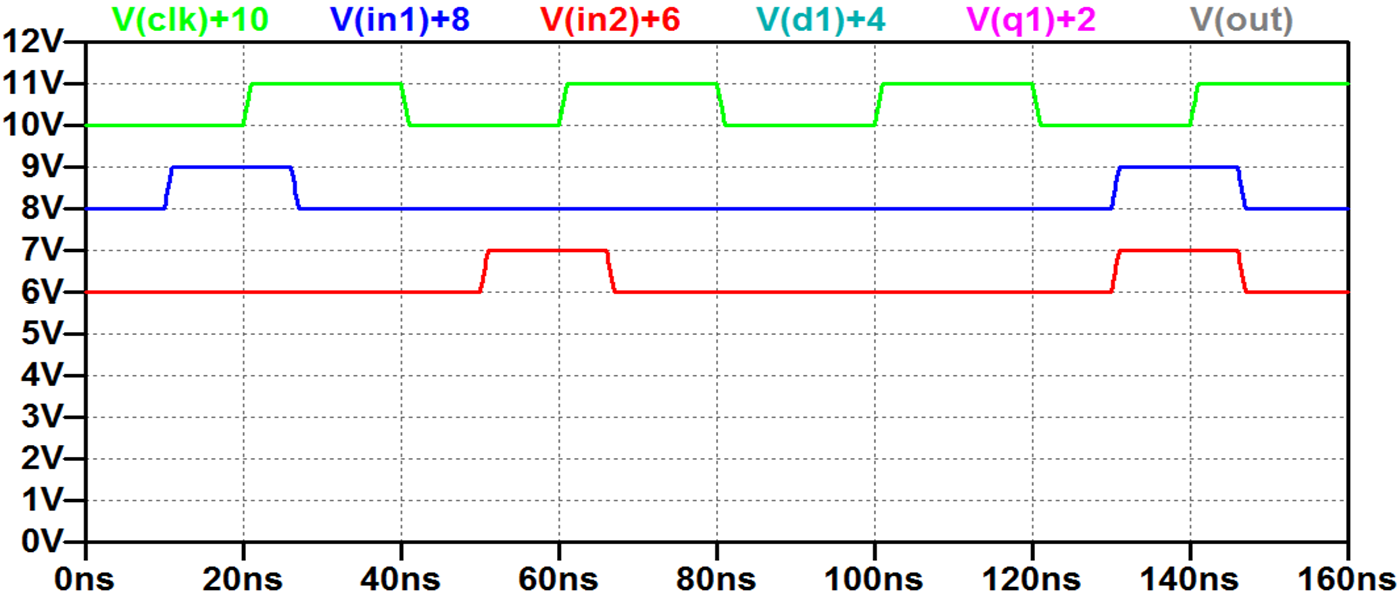

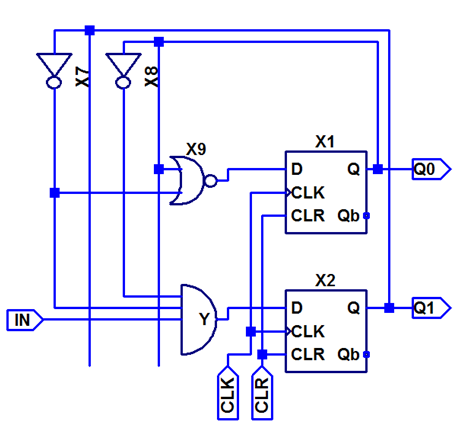

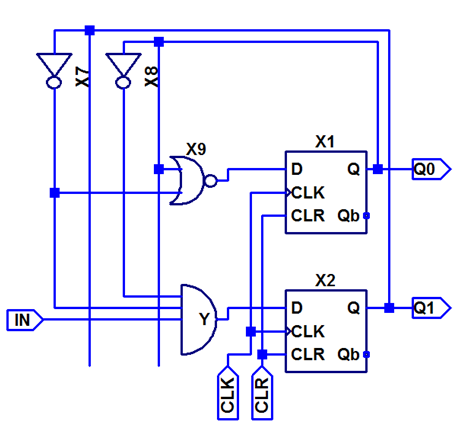

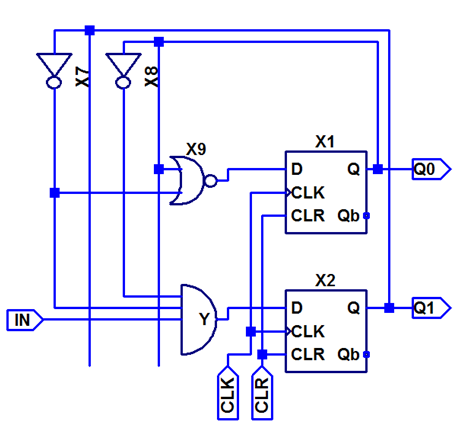

SS2013 Aufgabe 2: Schaltplananalyse

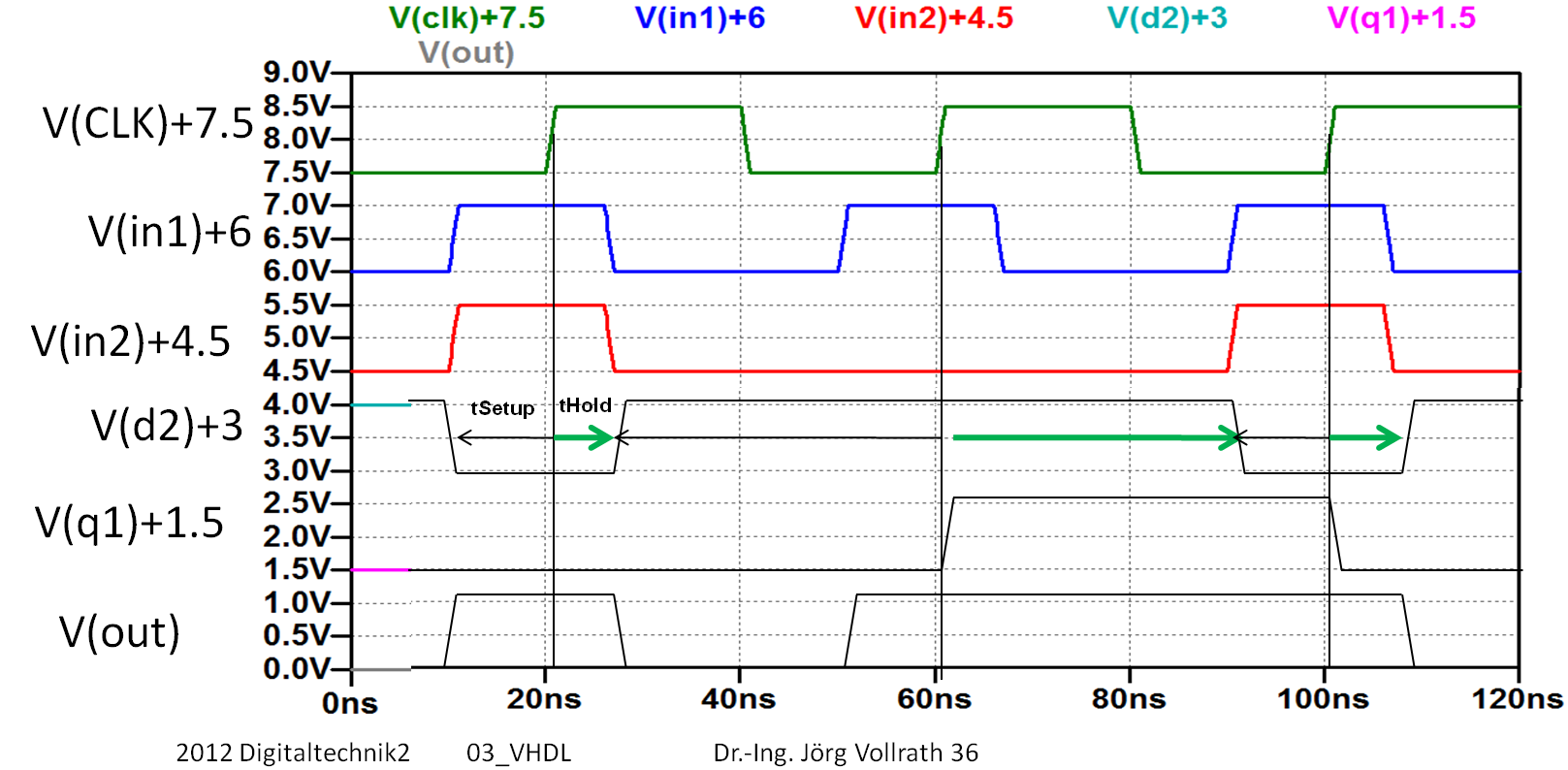

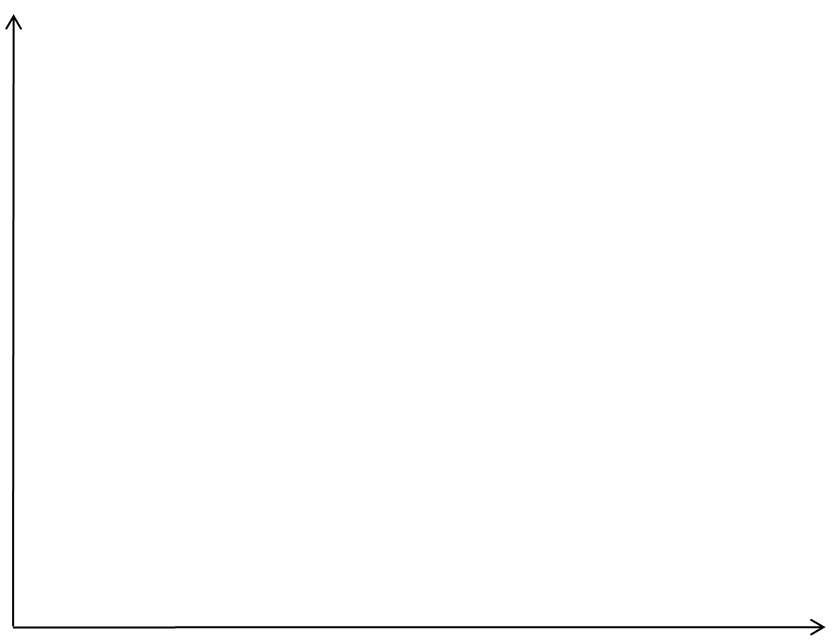

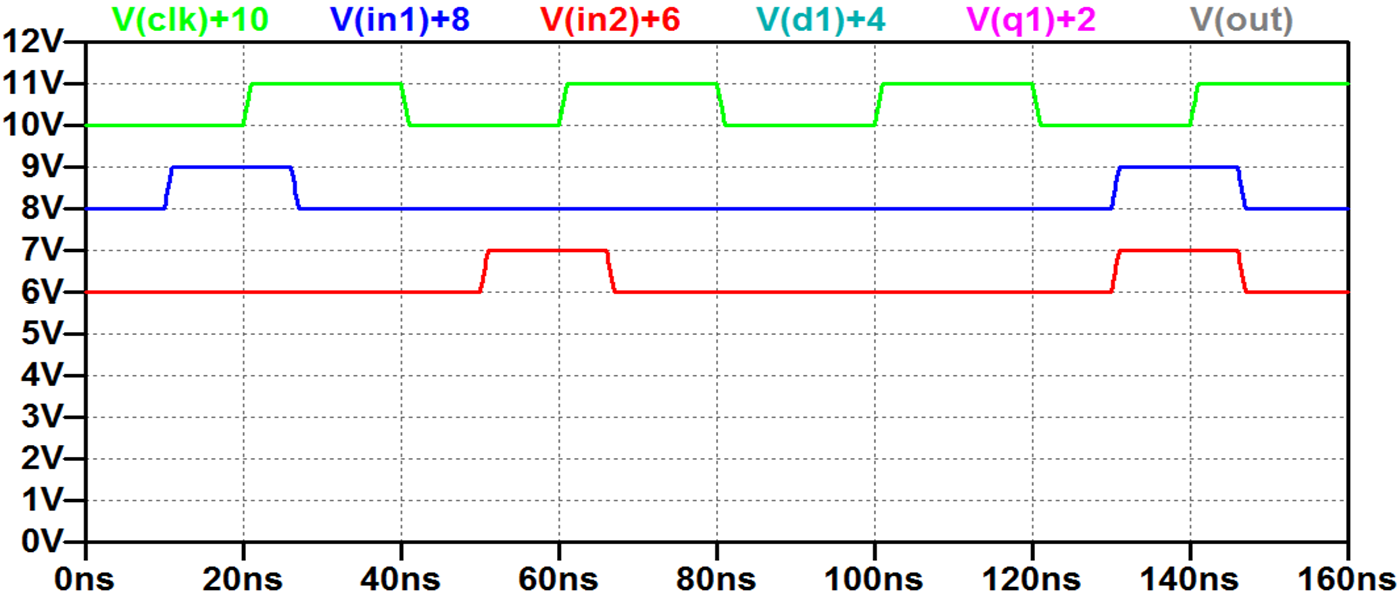

Zeichnen Sie das Zeitverhalten von Q1+2.2, D2+1.1 and Out in das obige

Diagramm. (6 Punkte)

Wie groß sind die Setup und Hold Zeiten? (3 Punkte)

Tragen Sie diese in das Diagramm ein. (3 Punkte)

SS2013 Aufgabe 3: Zustandsautomat

Es soll die Dauer des Drückens eines Tasters (T1) ausgegeben werden. Solange

der Taster noch gedrückt wird, zählt ein 2 Bit-Zähler (Z1,Z0) von 00 aus hoch bis

zum Maximalwert 11. Wird der Taster los gelassen, bleibt der Zählerstand erhalten.

1. Erstellen Sie eine Zustandstabelle (8 Punkte)

T1 Sn Z1n

Z0n Sn+1 Z1n+1

Z0n+1 Kommentar

2. Minimieren Sie die disjunktiven Normalform von Z1N+1 mit dem Karnaugh Veitch

Diagramm.(6 Punkte)

Z1n+1 Z0 /Z0 Z1

/T1 T1

/T1 /Z1

/S S /S

SS2013 Aufgabe 4: Zustandsdiagramm einer Schaltung

entity ThisCircuit1 is port (

a: in STD_LOGIC_VECTOR (1 downto 0);

b : in STD_LOGIC;

y: out STD_LOGIC;

clk: in STD_LOGIC);

end ThisCircuit1;

architecture Behavioral of ThisCircuit1 is

signal xy:STD_LOGIC;

begin

PROCESS (clk)

BEGIN

if (clk='1' and clk'event) then

CASE a IS

WHEN "00" => xy<=xy and b;

WHEN "01" => xy<=a(0) or b;

WHEN "10" => xy<=b and xy;

WHEN "11" => xy<=a(1) and b;

WHEN OTHERS => xy<='0';

END CASE;

end if;

END PROCESS;

y <= xy or b;

end Behavioral;

constant Tp : time := 10 ns;

clk_process :process

begin

clk <= '0'; wait for Tp/2;

clk <= '1'; wait for Tp/2;

end process;

stim_proc: process

begin

a <= "11"; b <='1'; wait for Tp;

a <= "10"; b <='0'; wait for 2*Tp;

a <= "00"; b <='1'; wait for Tp;

a <= "01"; b <='0'; wait for Tp;

a <= "11"; b <='0'; wait for Tp;

end process;

Zeichnen Sie das Zeitverhalten von Q1+2.2, D2+1.1 and Out in das obige Diagramm. (6 Punkte)

Wie groß sind die Setup und Hold Zeiten? (3 Punkte)

Tragen Sie diese in das Diagramm ein. (3 Punkte)

SS2013 Aufgabe 3: Zustandsautomat

Es soll die Dauer des Drückens eines Tasters (T1) ausgegeben werden. Solange

der Taster noch gedrückt wird, zählt ein 2 Bit-Zähler (Z1,Z0) von 00 aus hoch bis

zum Maximalwert 11. Wird der Taster los gelassen, bleibt der Zählerstand erhalten.

1. Erstellen Sie eine Zustandstabelle (8 Punkte)

T1 Sn Z1n

Z0n Sn+1 Z1n+1

Z0n+1 Kommentar

2. Minimieren Sie die disjunktiven Normalform von Z1N+1 mit dem Karnaugh Veitch

Diagramm.(6 Punkte)

Z1n+1 Z0 /Z0 Z1

/T1 T1

/T1 /Z1

/S S /S

SS2013 Aufgabe 4: Zustandsdiagramm einer Schaltung

| T1 | Sn | Z1n | Z0n | Sn+1 | Z1n+1 | Z0n+1 | Kommentar | |

| Z1n+1 | Z0 | /Z0 | |||||||||||||||||||

| Z1 |

|

/T1 | |||||||||||||||||||

| T1 | |||||||||||||||||||||

| /T1 | |||||||||||||||||||||

| /Z1 | |||||||||||||||||||||

| /S | S | /S | |||||||||||||||||||

|

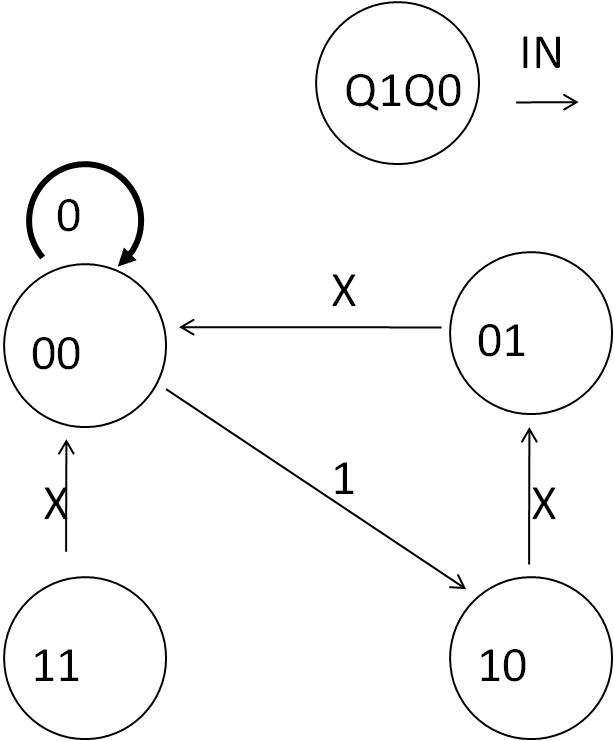

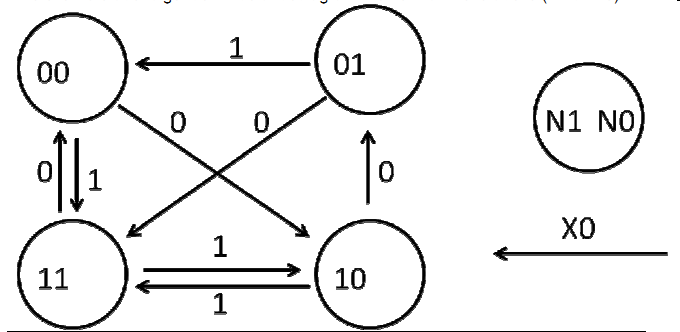

Bestimmen Sie die logischen

Gleichungen: (2 Punkte) Q0n+1= Q1n+1= Zeichnen Sie das Zustandsdiagramm. (4 Punkte) |

SS2013 Aufgabe 5: Begriffe

Was ist ein 4-Bit LFSR? Welche Eingangs- und Ausgangssignale hat es? Wie

funktioniert es? Wozu wird es verwendet? (4 Punkte)

Was ist ein FPGA? Wozu wird es verwendet? Was sind die Vorteile eines FPGAs im

Vergleich zu einem Mikroprozessor? (4 Punkte)

Welche Automaten gibt es? Welchen Automatentyp verwendet man nur und warum?

(4 Punkte)

Wofür steht die Abkürzung UART? Wofür wird diese Schaltung verwendet?

(2 Punkte)

Aufgabe 6: Schaltplan

Erstellen Sie aus folgendem Zustandsdiagramm eine Wahrheitstabelle (4 Punkte)

Klausur SS2014:

SS2014 Aufgabe 1:

1. Erstellen Sie für folgenden VHDL-Code die Wahrheits-/Zustandstabelle:

entity ThisCircuit_SS14 is

Port ( clk : in STD_LOGIC;

reset : in STD_LOGIC;

b : in STD_LOGIC;

y : out STD_LOGIC_VECTOR(1 downto 0));

end ThisCircuit_SS14;

architecture Behavioral of ThisCircuit_SS14 is

signal yint:STD_LOGIC_VECTOR(1 downto 0);

begin

PROCESS (clk,reset)

BEGIN

if reset='1' then

yint<="00";

elsif (clk='1' and clk'event) then

yint<=yint(1) & b;

end if;

END PROCESS;

y <= yint;

end Behavioral;

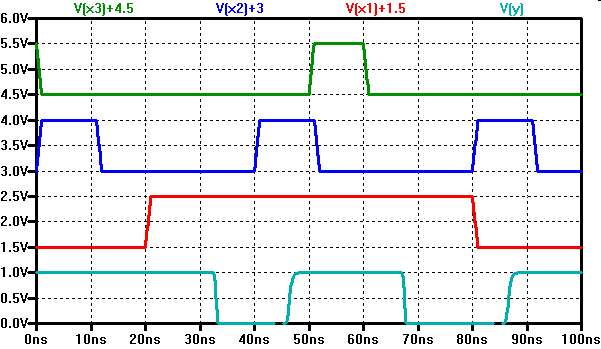

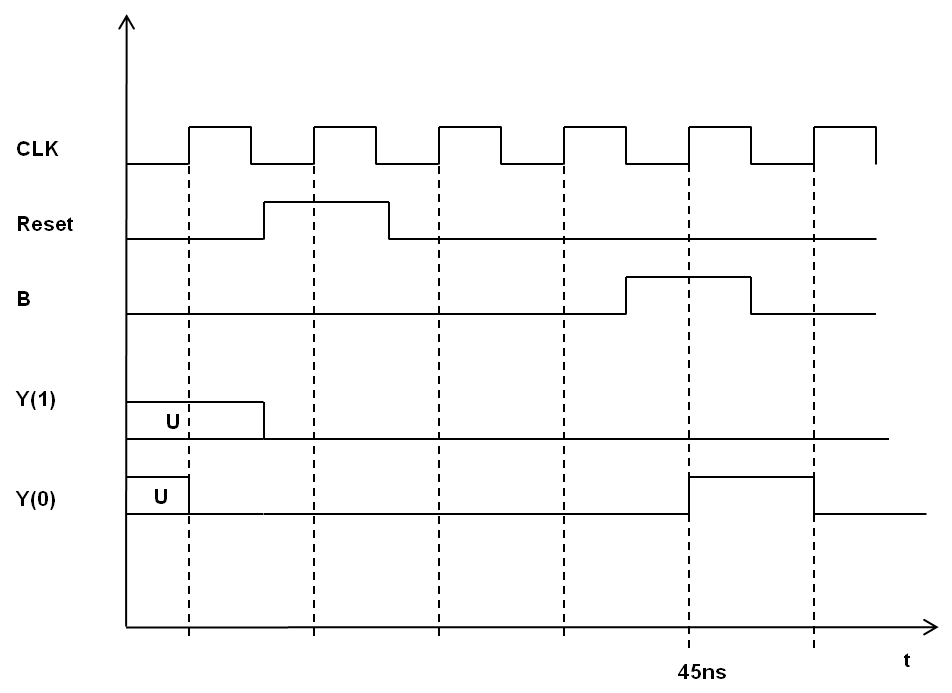

2. Geben Sie das Zeitverhalten der Signale clk, set, b und y für folgenden

VHDL Stimulus für die Schaltung ThisCircuit_SS14 an. (8 Punkte)

constant clk_period : time := 10 ns;

BEGIN

clk_process :process

begin

clk <= '0'; wait for clk_period/2;

clk <= '1'; wait for clk_period/2;

end process;

stim_proc: process

begin

reset <='0'; b<='0'; wait for 12 ns;

reset <='1'; b<='0'; wait for 10 ns;

reset <='0'; b<='0'; wait for 18 ns;

reset <='0'; b<='1'; wait for 10 ns;

reset <='0'; b<='0'; wait for 10 ns;

end process;

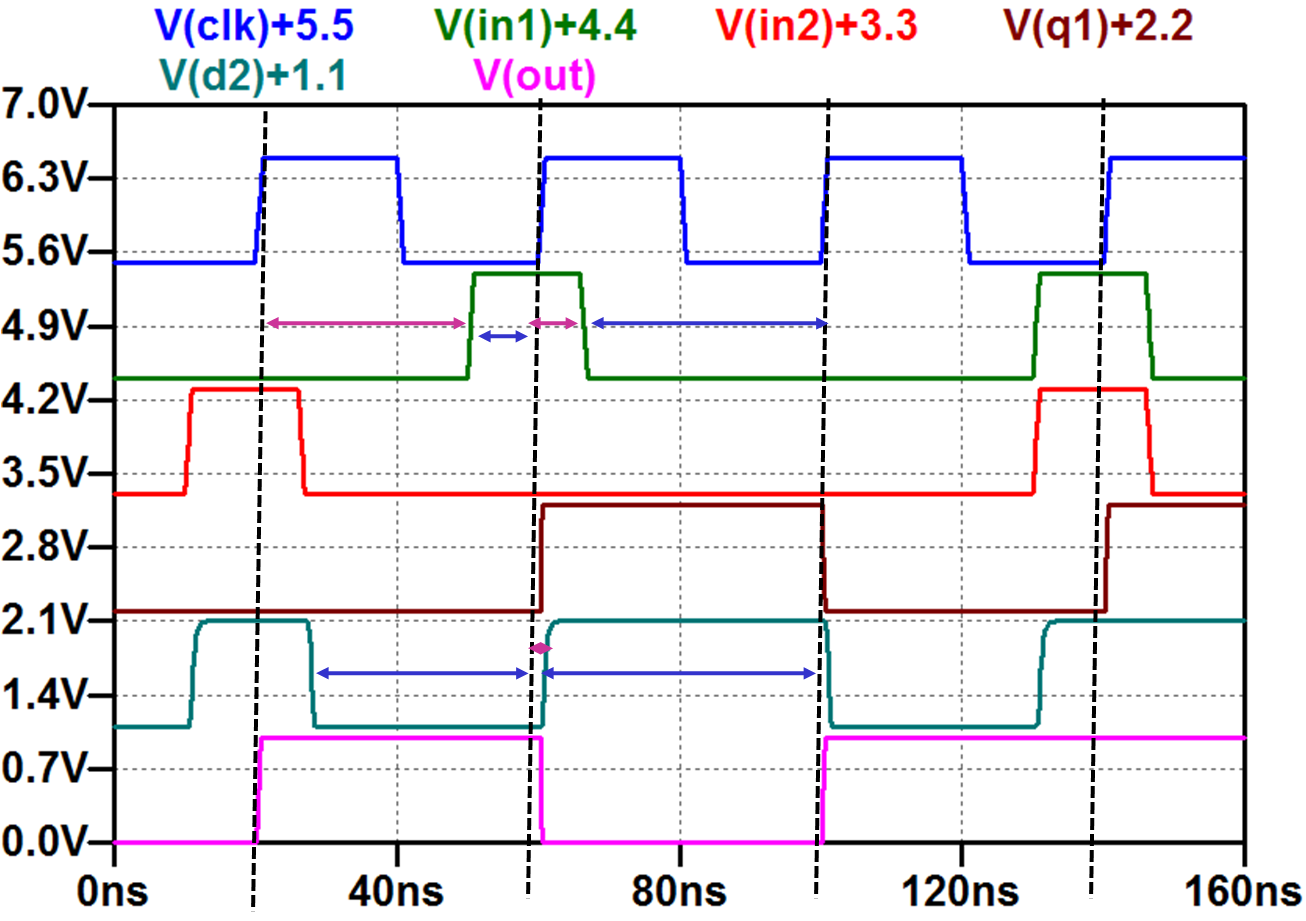

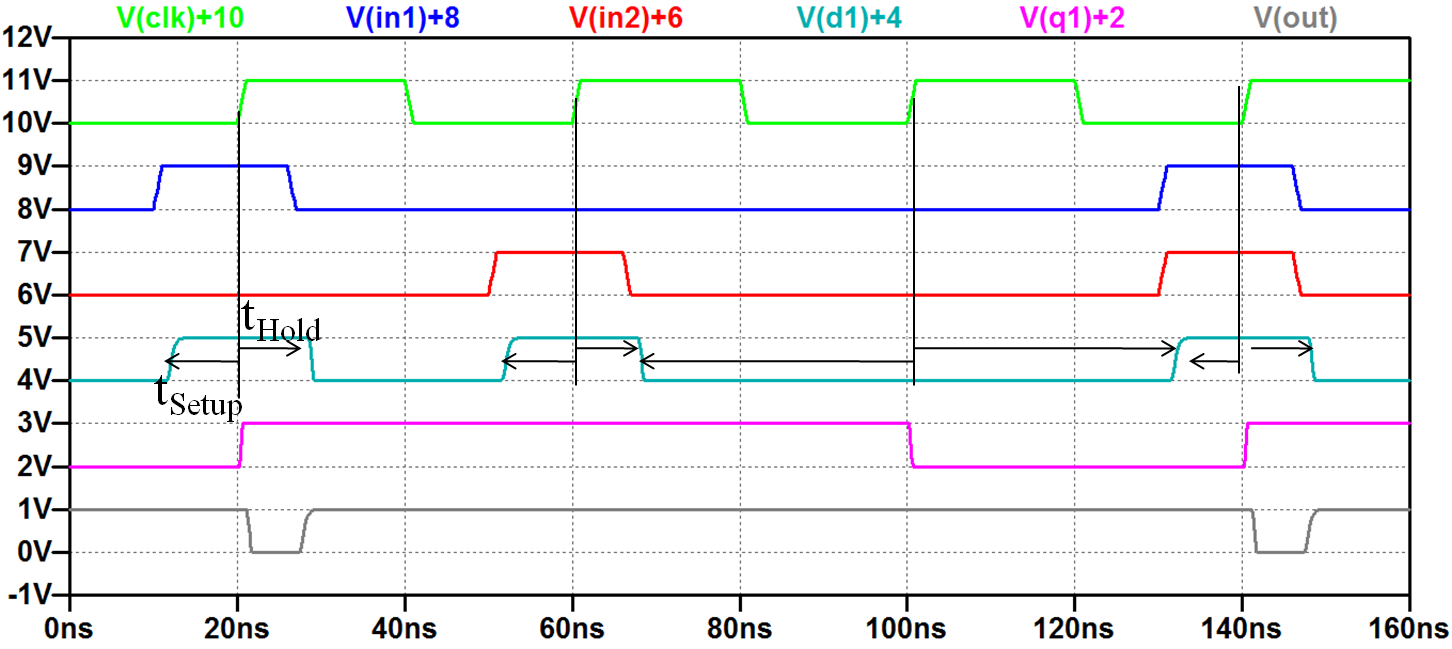

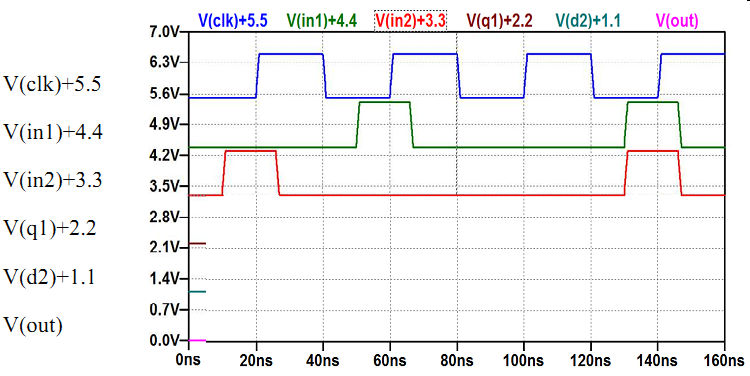

Aufgabe 2:

Zeichnen Sie das Zeitverhalten von

Q1+1.5, D2+3 and Out in das obige Diagramm. (6 Punkte)

Wie groß sind die Setup und Hold Zeiten? (2 Punkte)

Tragen Sie diese in das Diagramm ein. (2 Punkte)

SS2014 Aufgabe 3:

Eine Fußgängerampel soll durch einen Taster (T1) aktiviert werden. Dabei wird erst die

Ampel für die Fahrzeuge mit grün aktiviert (Z=001), dann wird die Ampel gelb(Z=010) und

rot (Z=100), bevor die Fußgängerampel dann grün (Z=011) wird. Nach einiger Zeit wird die

Fußgängerampel rot (Z=101), und dann die Ampel für die Fahrzeuge grün(Z=111). Zum

Schluss wird die Ampel wieder ausgeschaltet (Z=000).

1. Erstellen Sie eine Zustandstabelle (8 Punkte)

T1 Z2 Z1n

Z0n Z2n+1 Z1n+1

Z0n+1 Kommentar

2. Minimieren Sie die disjunktiven Normalform von Z1N+1 mit dem Karnaugh Veitch

Diagramm.(6 Punkte)

Z1n+1 Z0 /Z0 Z1

/T1 T1

/T1 /Z1

/Z2 Z2 /Z2

SS2014 Aufgabe 4: Zustandsdiagramm einer Schaltung

entity ThisCircuit_SS14 is

Port ( clk : in STD_LOGIC;

reset : in STD_LOGIC;

b : in STD_LOGIC;

y : out STD_LOGIC_VECTOR(1 downto 0));

end ThisCircuit_SS14;

architecture Behavioral of ThisCircuit_SS14 is

signal yint:STD_LOGIC_VECTOR(1 downto 0);

begin

PROCESS (clk,reset)

BEGIN

if reset='1' then

yint<="00";

elsif (clk='1' and clk'event) then

yint<=yint(1) & b;

end if;

END PROCESS;

y <= yint;

end Behavioral;

constant clk_period : time := 10 ns;

BEGIN

clk_process :process

begin

clk <= '0'; wait for clk_period/2;

clk <= '1'; wait for clk_period/2;

end process;

stim_proc: process

begin

reset <='0'; b<='0'; wait for 12 ns;

reset <='1'; b<='0'; wait for 10 ns;

reset <='0'; b<='0'; wait for 18 ns;

reset <='0'; b<='1'; wait for 10 ns;

reset <='0'; b<='0'; wait for 10 ns;

end process;

Zeichnen Sie das Zeitverhalten von Q1+1.5, D2+3 and Out in das obige Diagramm. (6 Punkte)

Wie groß sind die Setup und Hold Zeiten? (2 Punkte)

Tragen Sie diese in das Diagramm ein. (2 Punkte)

SS2014 Aufgabe 3:

Eine Fußgängerampel soll durch einen Taster (T1) aktiviert werden. Dabei wird erst die

Ampel für die Fahrzeuge mit grün aktiviert (Z=001), dann wird die Ampel gelb(Z=010) und

rot (Z=100), bevor die Fußgängerampel dann grün (Z=011) wird. Nach einiger Zeit wird die

Fußgängerampel rot (Z=101), und dann die Ampel für die Fahrzeuge grün(Z=111). Zum

Schluss wird die Ampel wieder ausgeschaltet (Z=000).

1. Erstellen Sie eine Zustandstabelle (8 Punkte)

T1 Z2 Z1n

Z0n Z2n+1 Z1n+1

Z0n+1 Kommentar

2. Minimieren Sie die disjunktiven Normalform von Z1N+1 mit dem Karnaugh Veitch

Diagramm.(6 Punkte)

Z1n+1 Z0 /Z0 Z1

/T1 T1

/T1 /Z1

/Z2 Z2 /Z2

SS2014 Aufgabe 4: Zustandsdiagramm einer Schaltung

| T1 | Z2 | Z1n | Z0n | Z2n+1 | Z1n+1 | Z0n+1 | Kommentar | |

| Z1n+1 | Z0 | /Z0 | |||||||||||||||||||

| Z1 |

|

/T1 | |||||||||||||||||||

| T1 | |||||||||||||||||||||

| /T1 | |||||||||||||||||||||

| /Z1 | |||||||||||||||||||||

| /Z2 | Z2 | /Z2 | |||||||||||||||||||

|

Bestimmen Sie die logischen

Gleichungen: (2 Punkte) Q0n+1= Q1n+1= Zeichnen Sie das Zustandsdiagramm. (4 Punkte) |

SS2014 Aufgabe 5: Begriffe

Was ist eine Pipeline und wozu wird Sie verwendet? (5 Punkte)

Aus welchen Schaltungsblöcken besteht ein Mikroprozessor? (3 Punkte)

Was ist ein Bus? (1 Punkte)

Was ist eine 7-Segment-Anzeige?

(1 Punkte)

SS2014 Aufgabe 6: Schaltplan

Erstellen Sie aus folgendem Zustandsdiagramm eine Wahrheitstabelle (4 Punkte)

Klausur SS2015:

SS2015 Aufgabe 1:

1. Erstellen Sie für folgenden VHDL-Code die Wahrheits-/Zustandstabelle:

entity ThisCircuit_SS15 is

Port ( clk : in STD_LOGIC;

set : in STD_LOGIC;

b : in STD_LOGIC;

y:out STD_LOGIC_VECTOR(1 downto 0));

end ThisCircuit_SS15;

architecture Behavioral of ThisCircuit_SS15 is

signal yint:STD_LOGIC_VECTOR(1 downto 0);

begin

PROCESS (clk,set)

BEGIN

if set='0' then

yint<="10";

elsif (clk='1' and clk'event) then

if b='0' then

yint<= '0' & yint(1);

else

yint<= yint(0) & '1';

end if;

end if;

END PROCESS;

y <= yint;

end Behavioral;

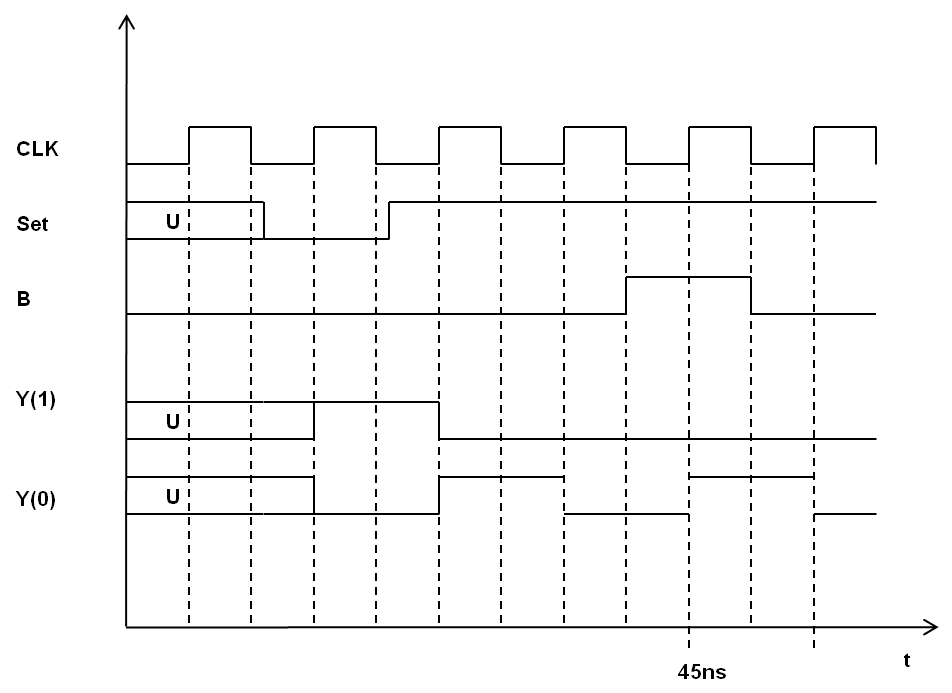

2. Geben Sie das Zeitverhalten der Signale clk, set, b und y für folgenden

VHDL Stimulus für die Schaltung ThisCircuit_SS15 an. (10 Punkte)

constant clk_period : time := 10 ns;

BEGIN

clk_process :process

begin

clk <= '0'; wait for clk_period/2;

clk <= '1'; wait for clk_period/2;

end process;

stim_proc: process

begin

b<='0'; wait for 12 ns;

set <='0'; wait for 10 ns;

set <='1'; wait for 18 ns;

b<='1'; wait for 10 ns;

b<='0'; wait for 10 ns;

end process;

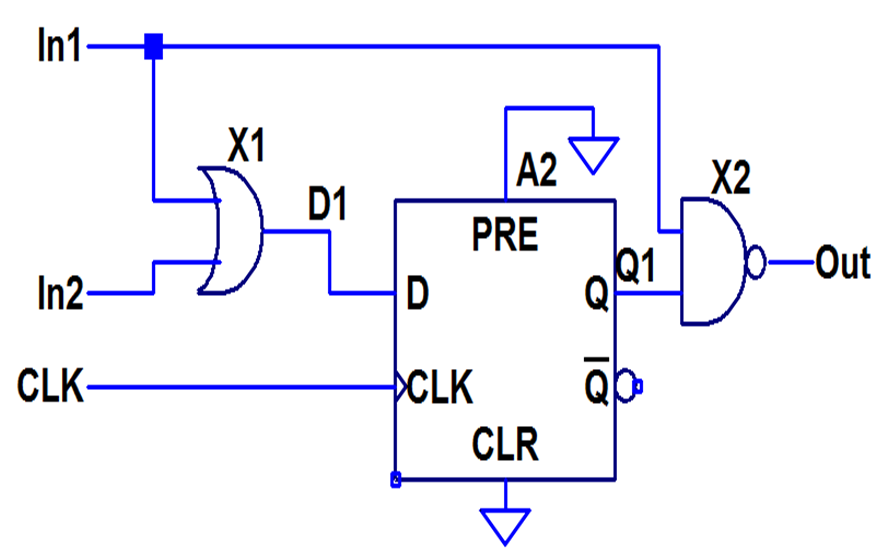

SS2015 Aufgabe 2: Schaltplananalyse

Zeichnen Sie das Zeitverhalten von d1+4, q1+2 und out in das obige

Diagramm. (6 Punkte)

Zeichnen Sie das Zeitverhalten von d1+4, q1+2 und out in das obige

Diagramm. (6 Punkte)

Wie groß sind die Setup und Hold Zeiten? (2 Punkte)

Tragen Sie diese in das Diagramm ein. (2 Punkte)

SS2015 Aufgabe 3: Zustandsautomat

An einem Automaten kann man für 30 Cent Süßigkeiten kaufen. Man kann 10 Cent

(C1=1) oder 20 Cent (C2=1) Münzen einwerfen. Eine Zustandsvariable S wird für

die Summe des eingeworfenen Betrages verwendet. Ist der Betrag von 30 Cent

erreicht soll ein Signal (V=1) die Warenausgabe starten. Wird der Betrag von 30

Cent überschritten soll die Münze durchfallen (D=1). Der Automat kann kein

Rückgeld geben.

1. Erstellen Sie eine Zustandstabelle (10 Punkte)

C2 C1 S1n

S0n S1n+1 S0n+1

V D Kommentar

2. Minimieren Sie die disjunktiven Normalformen von mit dem Karnaugh Veitch

Diagramm.(6 Punkte)

S0n+1 S0 /S0 S1

/C2 C2

/S1 /C2

/C1 C1 /C1

SS2015 Aufgabe 4: Zustandstabelle/Zustandsdiagramm einer Schaltung

Bestimmen Sie die logischen Gleichungen: (2 Punkte)

Q0n+1=

Q1n+1=

Zeichnen Sie das Zustandsdiagramm.

(6 Punkte)

entity ThisCircuit_SS15 is

Port ( clk : in STD_LOGIC;

set : in STD_LOGIC;

b : in STD_LOGIC;

y:out STD_LOGIC_VECTOR(1 downto 0));

end ThisCircuit_SS15;

architecture Behavioral of ThisCircuit_SS15 is

signal yint:STD_LOGIC_VECTOR(1 downto 0);

begin

PROCESS (clk,set)

BEGIN

if set='0' then

yint<="10";

elsif (clk='1' and clk'event) then

if b='0' then

yint<= '0' & yint(1);

else

yint<= yint(0) & '1';

end if;

end if;

END PROCESS;

y <= yint;

end Behavioral;

constant clk_period : time := 10 ns;

BEGIN

clk_process :process

begin

clk <= '0'; wait for clk_period/2;

clk <= '1'; wait for clk_period/2;

end process;

stim_proc: process

begin

b<='0'; wait for 12 ns;

set <='0'; wait for 10 ns;

set <='1'; wait for 18 ns;

b<='1'; wait for 10 ns;

b<='0'; wait for 10 ns;

end process;

Wie groß sind die Setup und Hold Zeiten? (2 Punkte)

Tragen Sie diese in das Diagramm ein. (2 Punkte)

SS2015 Aufgabe 3: Zustandsautomat

An einem Automaten kann man für 30 Cent Süßigkeiten kaufen. Man kann 10 Cent

(C1=1) oder 20 Cent (C2=1) Münzen einwerfen. Eine Zustandsvariable S wird für

die Summe des eingeworfenen Betrages verwendet. Ist der Betrag von 30 Cent

erreicht soll ein Signal (V=1) die Warenausgabe starten. Wird der Betrag von 30

Cent überschritten soll die Münze durchfallen (D=1). Der Automat kann kein

Rückgeld geben.

1. Erstellen Sie eine Zustandstabelle (10 Punkte)

C2 C1 S1n

S0n S1n+1 S0n+1

V D Kommentar

2. Minimieren Sie die disjunktiven Normalformen von mit dem Karnaugh Veitch

Diagramm.(6 Punkte)

S0n+1 S0 /S0 S1

/C2 C2

/S1 /C2

/C1 C1 /C1

SS2015 Aufgabe 4: Zustandstabelle/Zustandsdiagramm einer Schaltung

Bestimmen Sie die logischen Gleichungen: (2 Punkte)

Q0n+1=

Q1n+1=

Zeichnen Sie das Zustandsdiagramm.

(6 Punkte)

| C2 | C1 | S1n | S0n | S1n+1 | S0n+1 | V | D | Kommentar |

| S0n+1 | S0 | /S0 | |||||||||||||||||||

| S1 |

|

/C2 | |||||||||||||||||||

| C2 | |||||||||||||||||||||

| /S1 | |||||||||||||||||||||

| /C2 | |||||||||||||||||||||

| /C1 | C1 | /C1 | |||||||||||||||||||

Q0n+1=

Q1n+1=