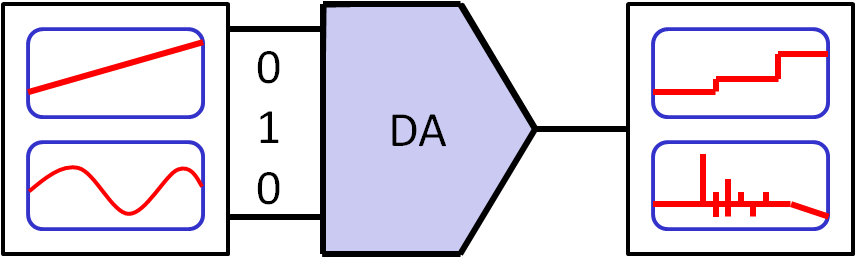

Interface Electronics07 DAC practical considerationsProf. Dr. Jörg Vollrath06 DAC errors |

Video Lecture: DAC practical considerations

|

Länge: 01:06:27 |

0:0:0 Interface Electronics 0:0:10 Ideal INL, DNL 0:0:42 DAC calibration example 0:3:3 Resistors and capacitances 0:5:35 Errors and resistance 0:6:53 DAC settling time Full scale, mid scale 0:11:29 DAC timing glitch 0:13:23 Sampling sine signal 0:15:8 DAC spectral measurement 0:18:20 DAC FFT with to many samples 0:24:17 One value per output code 0:25:3 DAC tool chain 0:26:4 DAC Evolution comparison 0:32:55 WS2012 Problem 4 0:38:11 Settling time 0:42:27 t > R C (B+1) ln(2) = 30 ns 0:46:0 Output voltage 0:48:51 Vout = (VD2/R3+VD1/R2+VD0/R1)Rout 0:54:34 Code = 001 |

Review and Overview

- Settling time

- Spurios signal coupling

- Timing error

- Reconstruction filter

- Spectral measurement

- Implementation examples

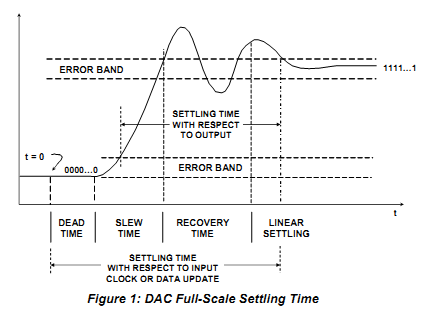

DAC settling time

|

|

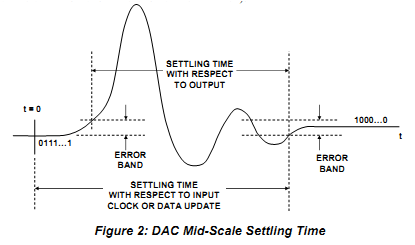

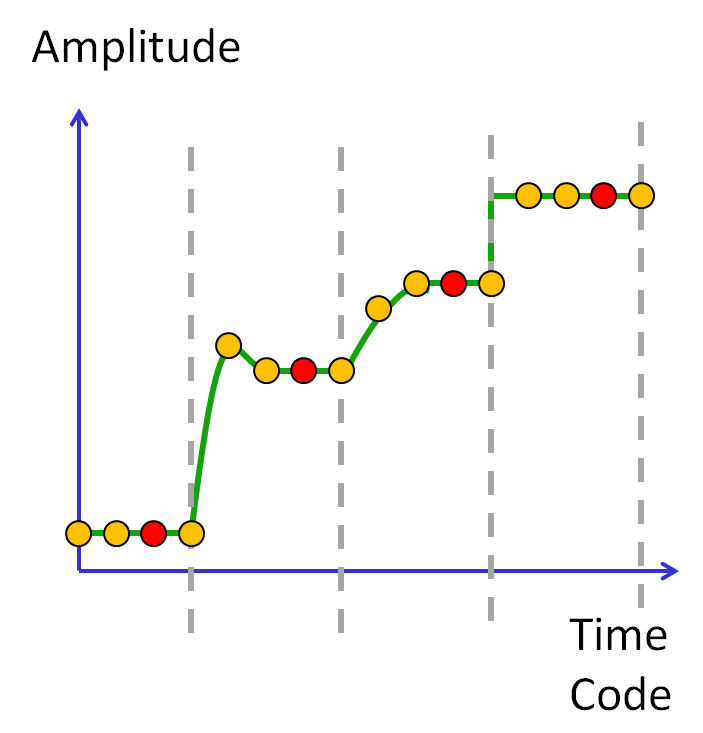

DAC timing glitch

|

|

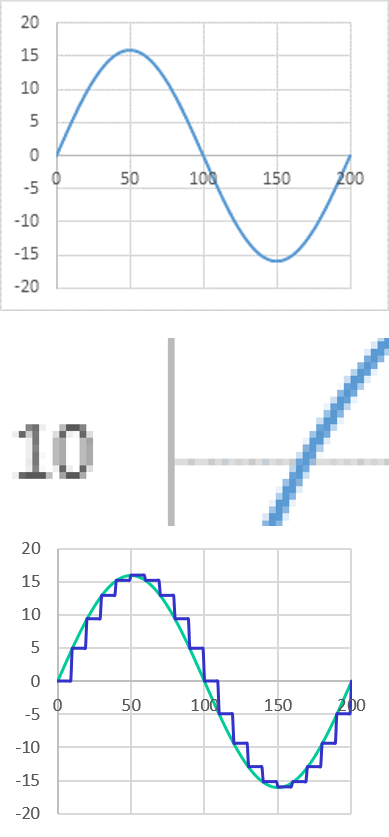

Sampling a sine signal

|

|

A sine function is generated with a x step size of 5.

The output looks like a low bit quantization despite using a very precise floating point number.

The y step size is very big for each step, but can vary a lot.

The output looks like a low bit quantization despite using a very precise floating point number.

The y step size is very big for each step, but can vary a lot.

DAC spectral measurement

Just sampling in Excel gives a kind of quantization.

DAC spectral measurement

|

|

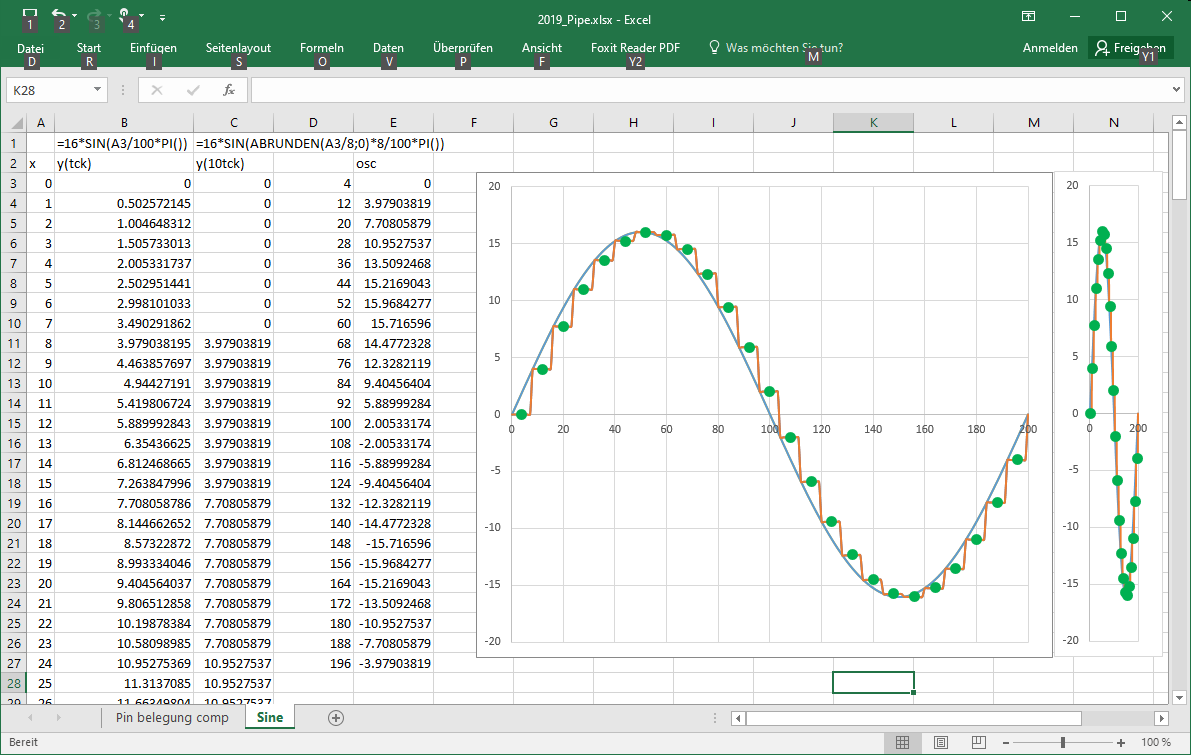

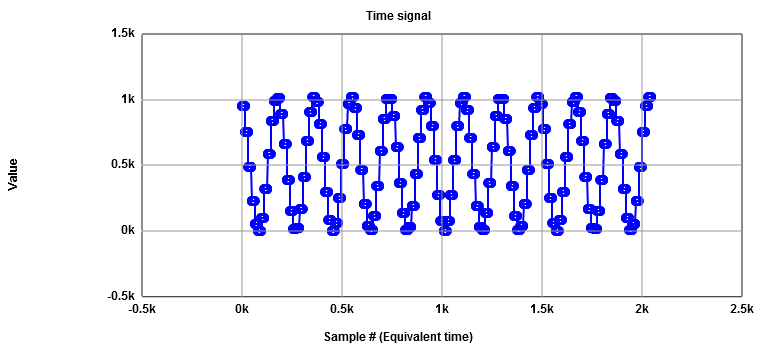

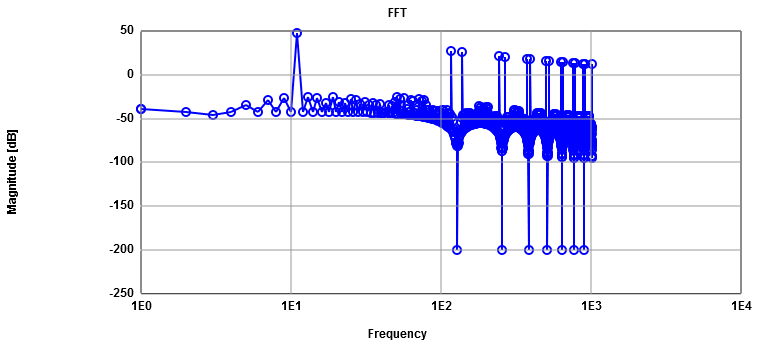

DAC distortion measurement

Sine signal and FFT10 bit, 11 periods, 2048 points, 16 samples per point

Signal (11) 48 dB, total noise 31 dB (ideal simulation -10 dB)

Harmonics () 27 dB..12 dB

Noise floor peaks -26 dB, total noise -14 dB

You can not estimate levels looking at the graph with reasonable accuracy.

Numerical calculation is required.

10 log (N/2) = 30 dB

Excel:

x, column A: 0..2047 points

y, column B: = RUNDEN(511.5 + 511.5 * SIN(RUNDEN(A2 / 16;0) * 16/2048*11*2*PI());0)

Javascript:

Javascript FFT

x, column A: 0..2047 points

y, column B: = RUNDEN(511.5 + 511.5 * SIN(RUNDEN(A2 / 16;0) * 16/2048*11*2*PI());0)

Javascript:

Math.round(offset + amplitude * Math.sin( Math.round(i/nStep) * nStep / nPoints * nPeriods * 2 *Math.PI()))

| Number of points: | |

| Number of periods: | |

| Range: | |

| Repetition of sample: |

DAC full system

Reconstruction filters:

|