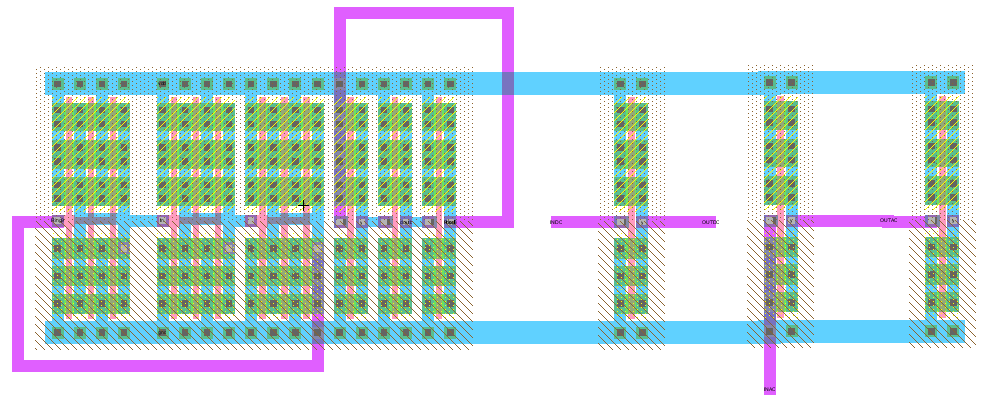

*** SUBCIRCUIT inv_1x1 FROM CELL inv_1x1{lay}

.SUBCKT inv_1x1 a gnd vdd y

Mnmos@0 y a gnd gnd N L=0.05U W=0.175U AS=0.042P AD=0.027P PS=1.4U PD=0.675U

Mnmos@1 y a gnd gnd N L=0.05U W=0.175U AS=0.042P AD=0.027P PS=1.4U PD=0.675U

Mpmos@0 y a vdd vdd P L=0.05U W=0.25U AS=0.051P AD=0.027P PS=1.55U PD=0.675U

.ENDS inv_1x1

.SUBCKT inv_1x1a a gnd vdd y

Mnmos@0 y a gnd gnd N L=0.05U W=0.175U AS=0.042P AD=0.027P PS=1.4U PD=0.675U

Mnmos@1 y a gnd gnd N L=0.05U W=0.175U AS=0.042P AD=0.027P PS=1.4U PD=0.675U

Mpmos@0 y a vdd vdd P L=0.05U W=0.25U AS=0.051P AD=0.027P PS=1.55U PD=0.675U

Mpmos@1 y a vdd vdd P L=0.05U W=0.25U AS=0.051P AD=0.027P PS=1.55U PD=0.675U

.ENDS inv_1x1

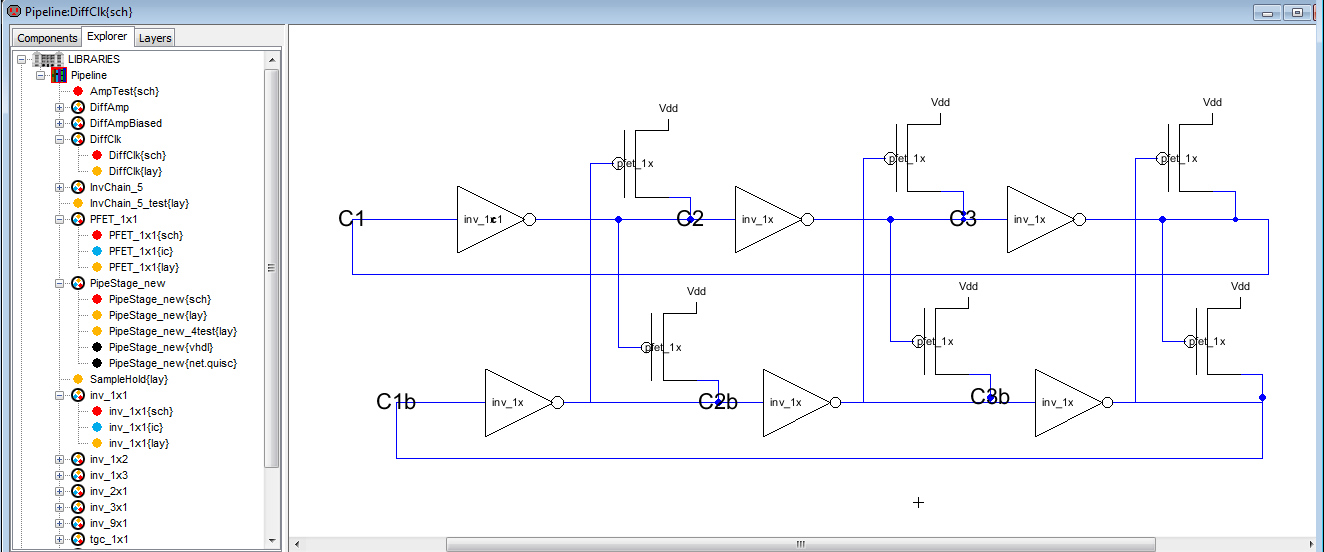

*** TOP LEVEL CELL: DiffClk{lay}

XPFET_1x1@0 C2 gnd vdd C2b PFET_1x1

* XPFET_1x1@1 C3 gnd vdd C3b PFET_1x1

* XPFET_1x1@2 C1 gnd vdd C1b PFET_1x1

XPFET_1x1@3 C2b gnd vdd C2 PFET_1x1

*XPFET_1x1@4 C3b gnd vdd C3 PFET_1x1

*XPFET_1x1@5 C1b gnd vdd C1 PFET_1x1

Xinv_1x1@0 C1b gnd vdd C2b inv_1x1

Xinv_1x1@1 C2b gnd vdd C3b inv_1x1a

Xinv_1x1@2 C3b gnd vdd C1b inv_1x1a

Xinv_1x1@3 C1 gnd vdd C2 inv_1x1

Xinv_1x1@4 C2 gnd vdd C3 inv_1x1a

Xinv_1x1@5 C3 gnd vdd C1 inv_1x1a