| VDD | 2 V | 3 V | 4 V | 5 V |

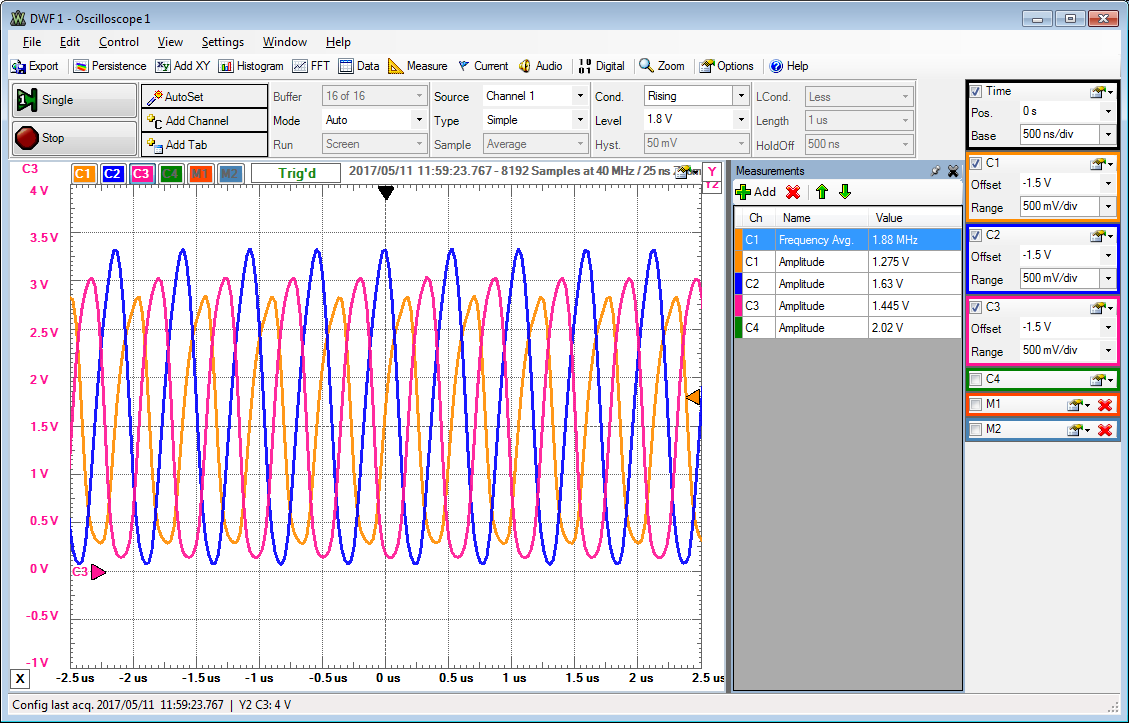

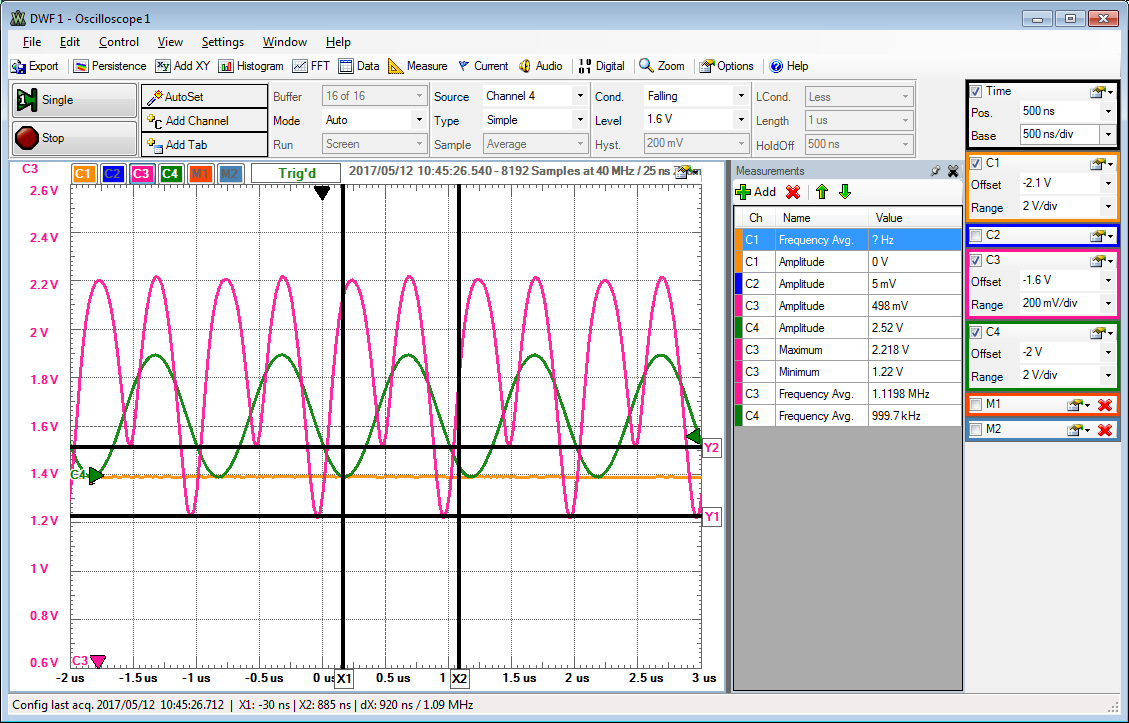

| fring3 | 605 kHz | 1.88 MHz | 2.4 MHz | 2.9 MHz |

| Tring3 | 1.65 ns | 0.53 ns | 0.42 ns | 0.34 ns |

Inverter as amplifier (VDD = 5 V, T = 22 C):

| f | 100 kHz | 200 kHz | 500 kHz | 1 MHz |

| Vin | 50 mV | 50 mV | 100 mV | 100 mV |

| Vout | 1 V | 700 mV | 600 mV | 300 mV |

Capacitive load: 471 (470 pF) 100ns delay increases to 800ns delay.

NFET source circuit with PFET diode load

| f | 100 kHz | 200 kHz | 500 kHz | 1 MHz |

| Vin | 310mV | 310 mV | 310 mV | 305 mV |

| Vout | 545 mV | 540 mV | 490 mV | 400 mV |

NFET source circuit with double length PFET diode load

| f | 100 kHz | 200 kHz | 500 kHz | 1 MHz | 1 MHz |

| Vin | 110mV | 100 mV | 100 mV | 100 mV | 400 mV |

| Vout | 270 mV | 270 mV | 230 mV | 170 mV | 600 mV |

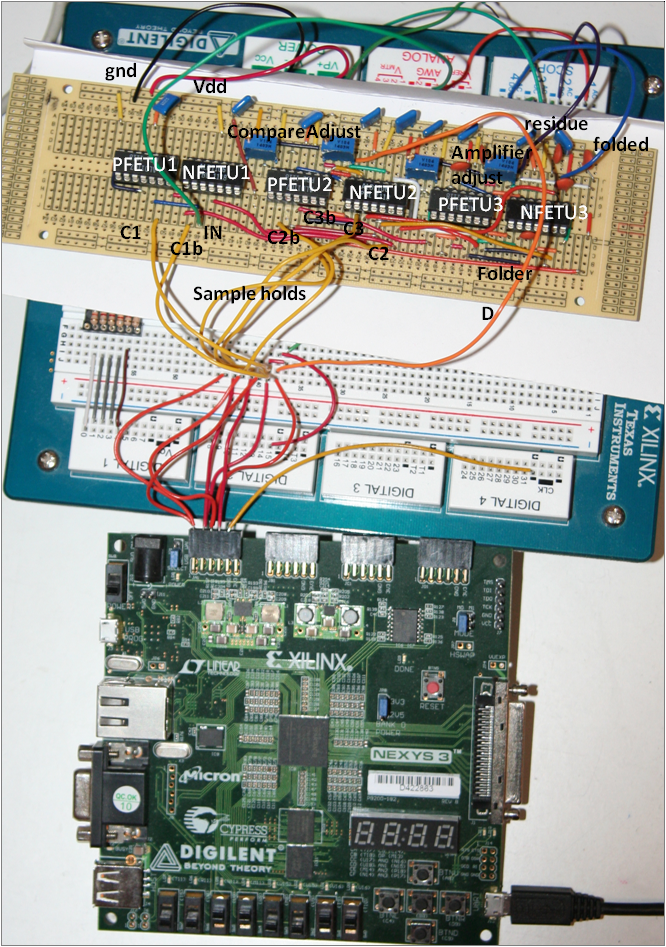

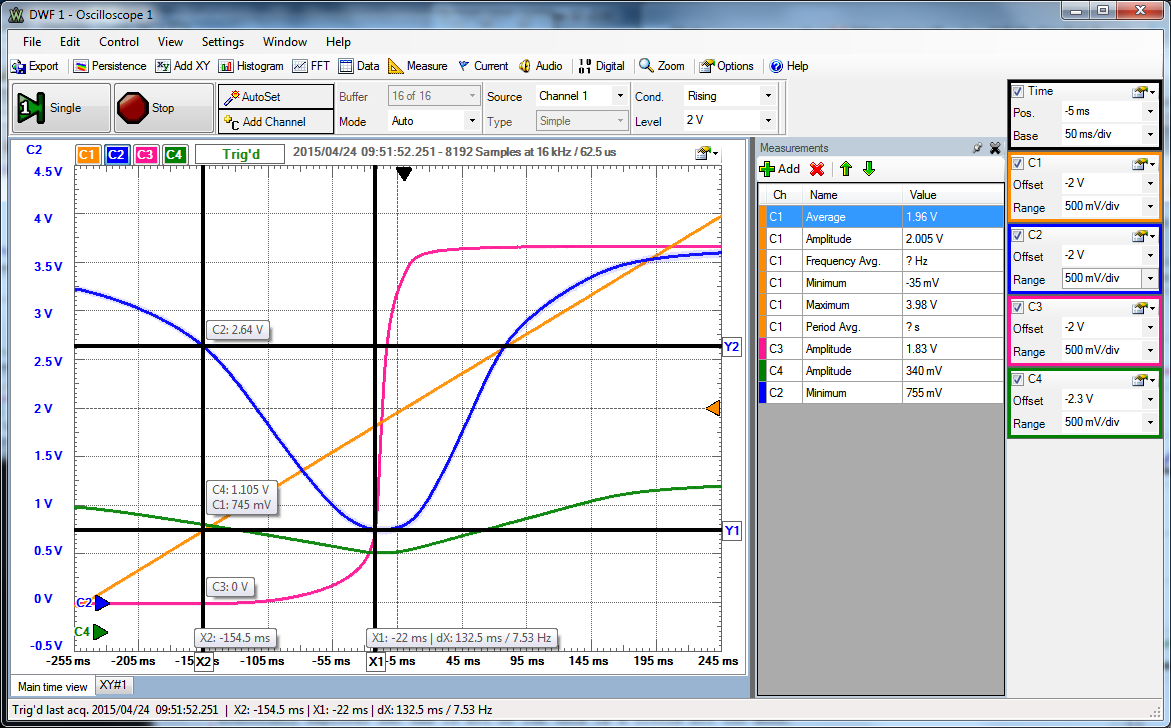

Folder 4 transistors:

| fin | 100 kHz | 200 kHz | 500 kHz | 1 MHz | 1 MHz |

| Vin | 1.5 V | ||||

| Vout | 0.25 V |

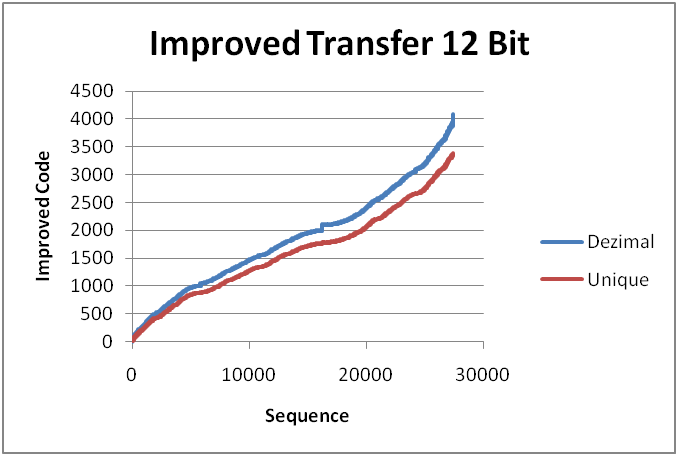

Vin 1.5 V amplitude gives at output 250 mV. At higher frequencies the midpoint low voltage at the output is different between rising and falling.

Difference of minimum: 500 kHz 230 mV, 100kHz 70mV, 10kHz 0 V.

Gain: 0.17

(simulation gain: 325 mV /1.5 V = 0.22)

Folder 3 transistors:

Vin 2.5V amplitude, 2.5 V offset, Vout 500 mV amplitude, 1.7 V offset, 10 kHz. No difference between rising and falling input signal for minimum voltage at the output.

Gain: 0.2

100 kHz Minimum difference for output with rising and falling input signal is 40 mV.

1 MHz gives 285 mV difference at the minimum.

( simulation gain: 0.6 V / 2.5 V = 0.24)