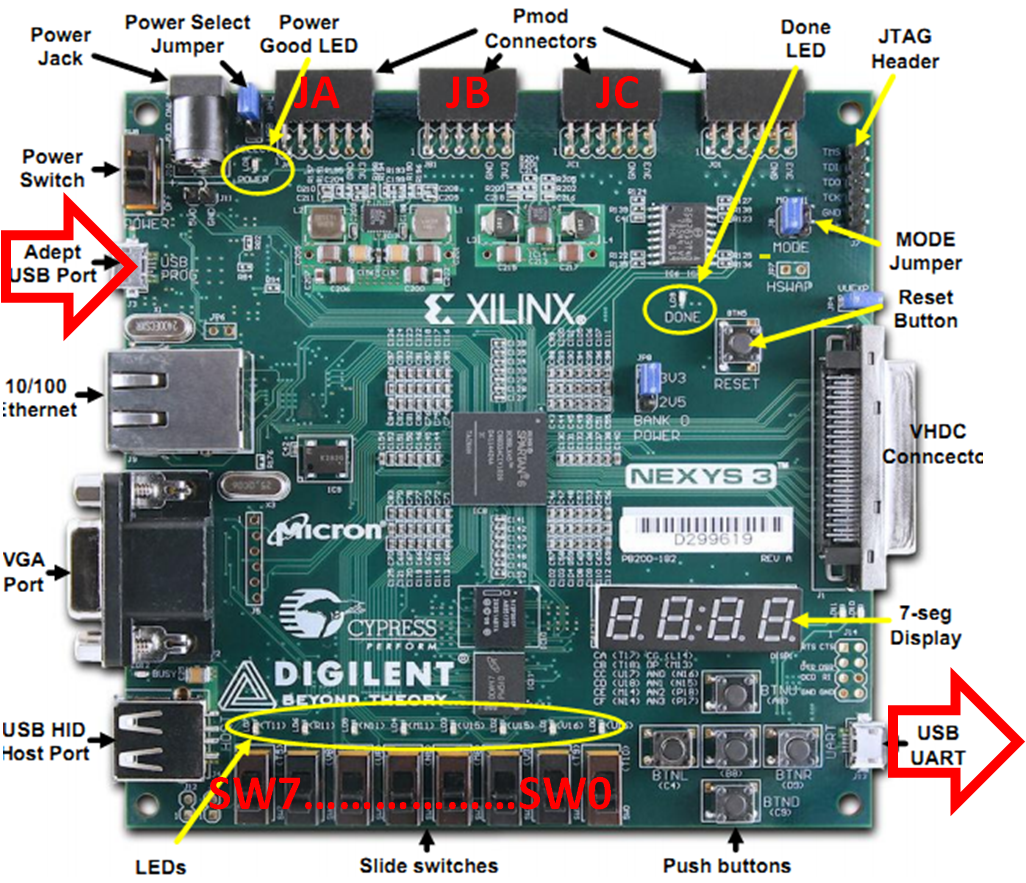

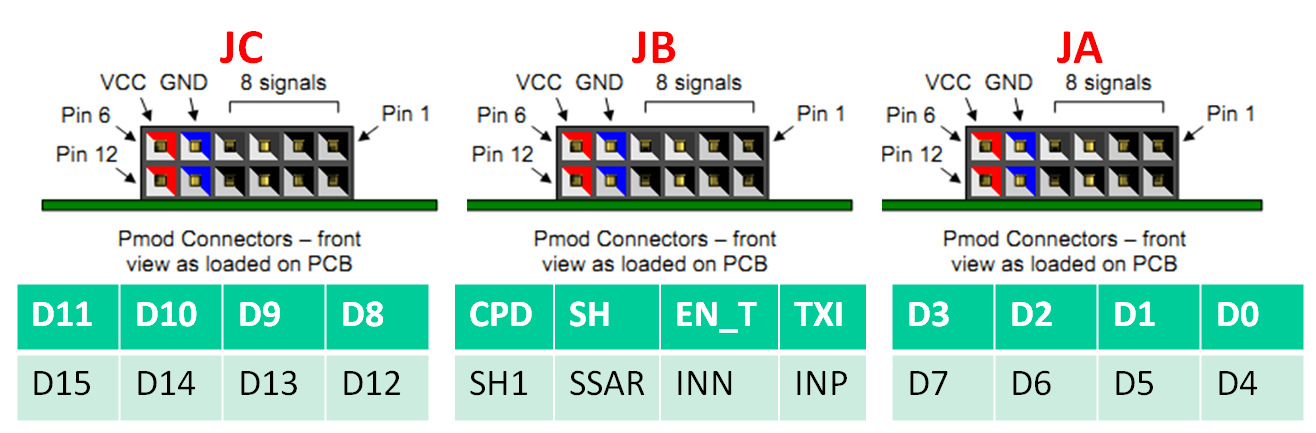

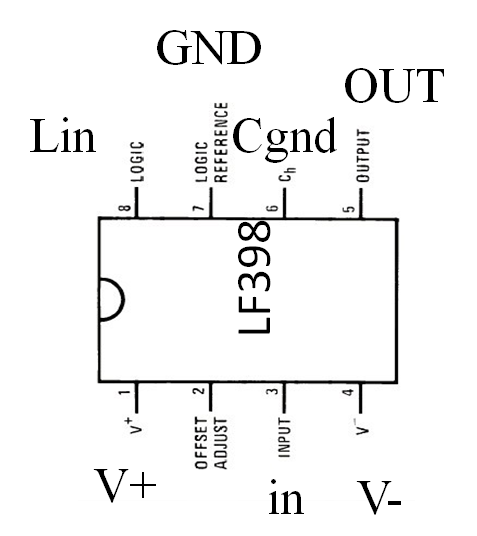

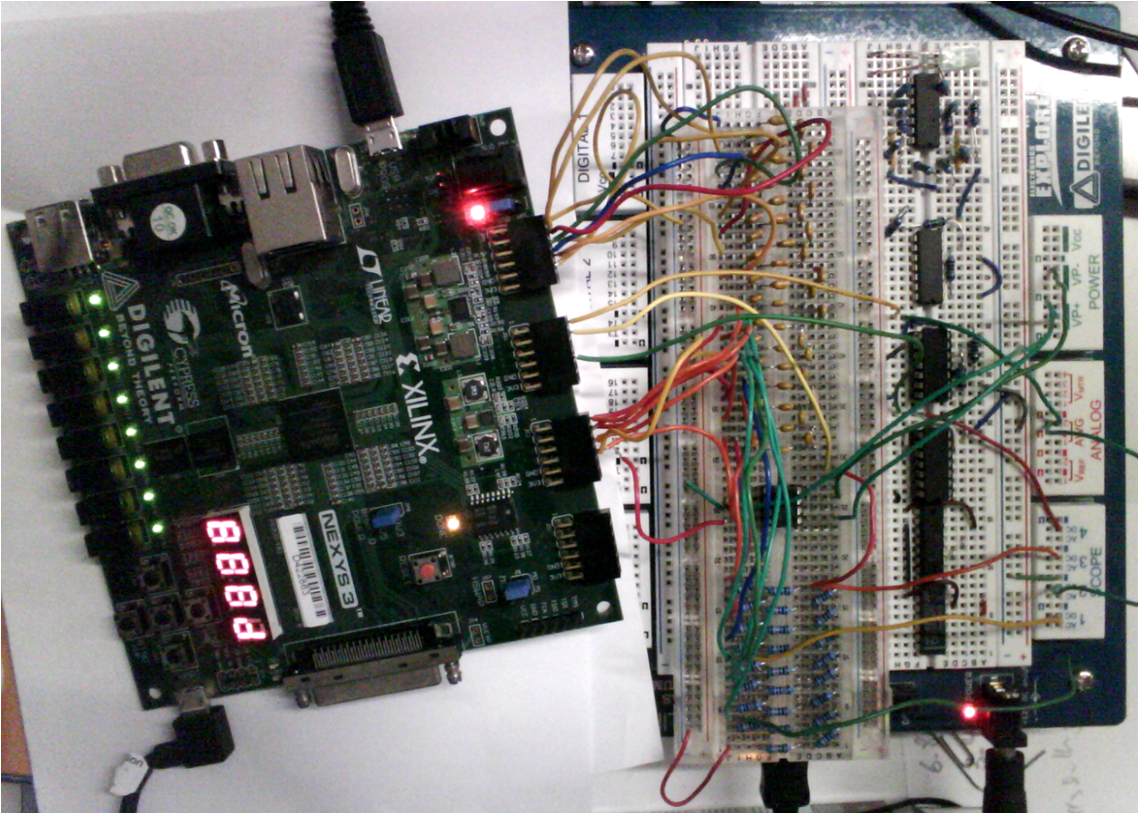

List of partsElectronic Explorer Board ($ 330 / $660) Nexys 3 Board ($ 190 / $270) 1 LF398 (Sample and Hold) 54 Capacitors (C2C DAC) Breadboard PCB like Electronic Explorer (EBay) VHDL Files for Nexys 3 Board for Spartan 6, XC6SLX45, Package CSG324 Programming Bit File for Nexys 3 Board for Spartan 6, XC6SLX45, Package CSG324 Duration6 Laboratories |