|

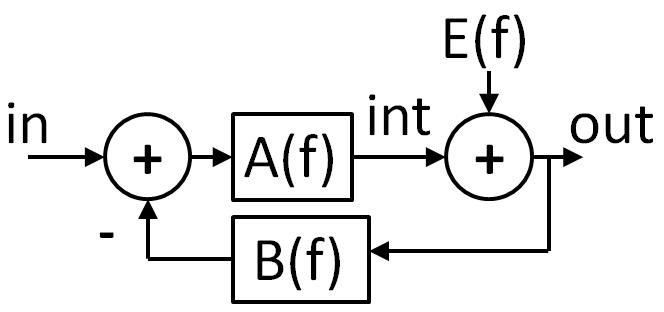

A \( \Sigma \Delta \) analog to digital converter (ADC) integrates (sigma) the difference (delta)

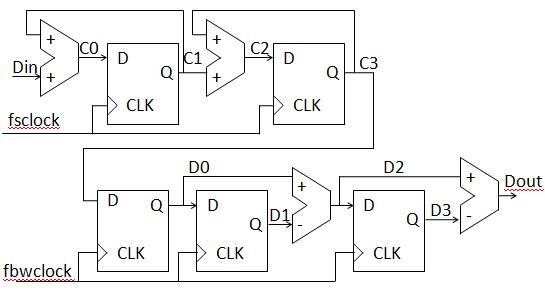

between the input signal and an analog value generated by the current digital output code. It is an oversampling ADC where the sample frequency \( f_{sampleIn} \)(clock frequency) is much higher than the bandwidth \( f_{bw} \) of interest. The oversampling ratio OSR is defined as: \( OSR = \frac{f_{sampleIn}}{f_{sampleOut}} \) \( f_{bw} = \frac{f_{sampleOut}}{2} \) A digital filter is used to downsample the digital output stream, increasing the number of bits and filtering out noise. \( \Sigma \Delta \) ADCs can be of different order, active using operational amplifiers or switched capacitor circuits and passive. There are also cascaded (MASH) \( \Sigma \Delta \) ADCs to prevent instability. Objectives: 1. Provide high level no cost JavaScript models in this web page. 2. Provide working LTSPICE transistor level models for simulation. 3. Provide simple low cost analog circuits with FPGA data processing for real experiments and measurement. |

|

To prevent gain error from the signal transfer function \( \frac{1}{| j \omega + 1 |} \gt (1 - 0.5 \frac{LSB}{V_{ref}} ) \) \( \frac{1}{| j \omega + 1 |} \gt (1 - \frac{1}{2^{N+1}} ) \) \( \frac{1}{\sqrt{ \omega^{2} + 1 }} \gt (1 - \frac{1}{2^{N+1}} ) \) \( \frac{1}{(1 - \frac{1}{2^{N+1}} )^2} \gt \omega^{2} + 1 \) \( \omega^{2} \lt \frac{1}{(1 - \frac{1}{2^{N+1}} )^2} - 1 \) \( \omega^{2} \lt \frac{1 - 1 + \frac{1}{2^N}- \frac{1}{2^{2N+2}}}{(1 - \frac{1}{2^{N+1}} )^2} \) \( \omega^{2} \lt \frac{\frac{1}{2^N} \left( 1 - \frac{1}{2^{N+2}} \right) }{(1 - \frac{1}{2^{N+1}} )^2} \approx \frac{1}{2^N} \) \( \omega \lt \frac{1}{2^\frac{N}{2}} \) |

\( \frac{\delta t}{C \cdot R} = \frac{2 \pi f_{gRC}}{ f_{sample}} \gt \pi \frac{2^{\frac{N}{2}} }{OSR} \) |

| Time | 0 |

| V(INT) | 0.5 |

| V(OUT) | 0 |

| V(D) | 0 |

| Code | Vt(0.2) [V] | Vt(0.3) [V] | Vt(0.1) [V] |

| 00000000... | 0 | 0 | 0 |

| 00010001... | 0.097 | 0.04 | 0.17 |

| 001001001.. | 0.183 | 0.11 | 0.27 |

| 01010101... | 0.375 | 0.29 | 0.45 |

| 011011011.. | 0.7 | 0.75 | 0.68 |

| 01110111... | 0.84 | 0.91 | 0.79 |

| 11111111... | 1 | 1 | 1 |

| K values | up to Fs/16 | up to Fs/8 | up to Fs/4 |

| sinc1 | 25.6573 | 24.65659 | 21.04096 |

| sinc1 error +/- dB | 0.00017 | 0.0027 | 0.045 |

| sinc2 | 13.79721 | 13.20875 | 11.12903 |

| sinc2 error +/- dB | 0.0004 | 0.0064 | 0.104 |

| sinc3 | 9.843906 | 9.393567 | 7.835116 |

| sinc3 error +/- dB | 0.0007 | 0.011 | 0.177 |

| OSR | 30 log(OSR) dB | SINC1 | SINC2 | SINC3 | Number of points FFT, register width W |

| 4 | 18 | 11 | 17 | 18 | Valid, FFT 1024, 16 Bit |

| 8 | 27 | 17 | 25 | 27 | Valid, FFT 1024, 16 Bit |

| 32 | 45 | 29 | 40 | 42 | Valid, FFT 1024, 16 Bit |

| 256 | 72 | 47 | 63 | 64 | Valid, FFT 1024, 30 Bit |

| 512 | 81 | 53 | 71 | 72 | Valid, FFT 1024, 30 Bit |

| 2048 | 99 | 65 | 86 | 87 | Valid, FFT 1024, 40 Bit |

| OSR | SINC1 | SINC2 | SINC3 |

| 4 | 3 | 5 | 7 |

| 8 | 4 | 7 | 10 |

| 32 | 6 | 11 | 16 |

| 256 | 9 | 17 | 25 |

| 512 | 10 | 19 | 28 |

| 2048 | 12 | 23 | 34 |

| 16k | 15 | 29 | 43 |