Digitaltechnik12 SpeicherzellenfelderProf. Dr.J÷rg Vollrath11 Zustandsdiagramm und Zõhler |

|

Ein kurze Videozusammenfassung der Vorlesung

Lõnge: 10:29 min

Zeitverhalten einer Schaltung mit Speicherglied

Lõnge: 6:03 min

R³ckblick und Heute

R³ckblick:

- Zustandsdiagramme

- Modulo 5 Zõhler

- Spezifikation: Symbol, Zeitverhalten

- Zustandsdiagramm, Zustandstabelle, Minimalform

- VHDL Beschreibung und Test

- Schaltplan, LTSPICE und Test

Heute:

- Bildverarbeitung, PC und Speicher

- Speichertypen und Klassifizierung

RAM, SRAM, Flash - Aufbau

- Kenngr÷▀en

- Speicherstrukturen

- VHDL Realisierung

Lesen: Reichardt: Kap 15

Praktikum

Versuch 4: Tasterabfrage- Problembeschreibung: Taster

- Zustandsmaschine f³r dp

- Dateien: xdc, VHDL, VHDL test

- Abschnitte: COMPONENT, SIGNAL, UUT, Zuweisung

Versuch 5: Zustandsmaschine

Schieben der angezeigten Zahl

- Transfer:

Zustandsmaschine dp wird kopiert und erweitert f³r an

Selbststõndig: SIGNAL, Zustandstabelle mit case - Weniger detailliert Anweisungen:

Erstellung des Zeitablaufs in der VHDL Testdatei.

Durchf³hrung der Simulation

Implementierung - Fragen zum Nachdenken und zur L÷sung

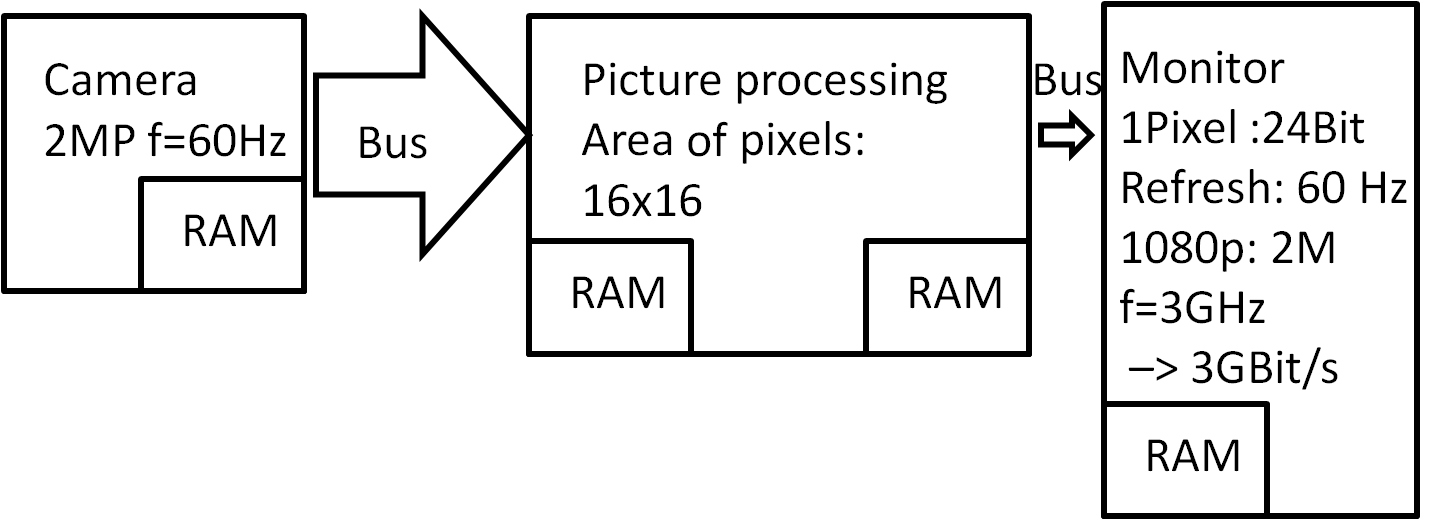

Bildverarbeitung

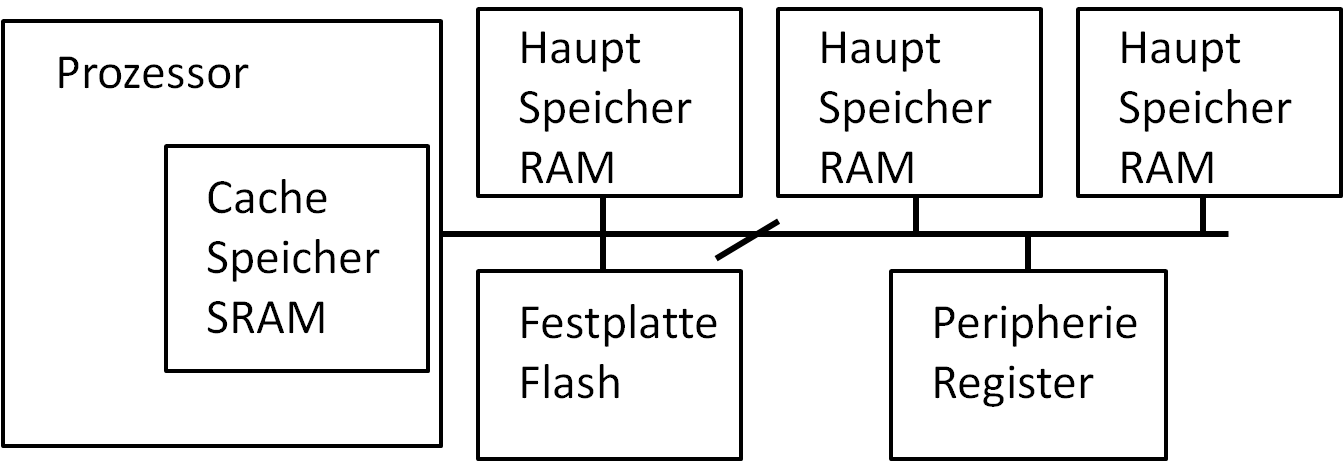

Digitale Halbleiterspeicher

- Bussystem

- Adressen

- Daten

- Kontrollleitungen

- Aktivieren, Schreiben, Lesen

Speicherglieder, Speicherfelder, Memory Array

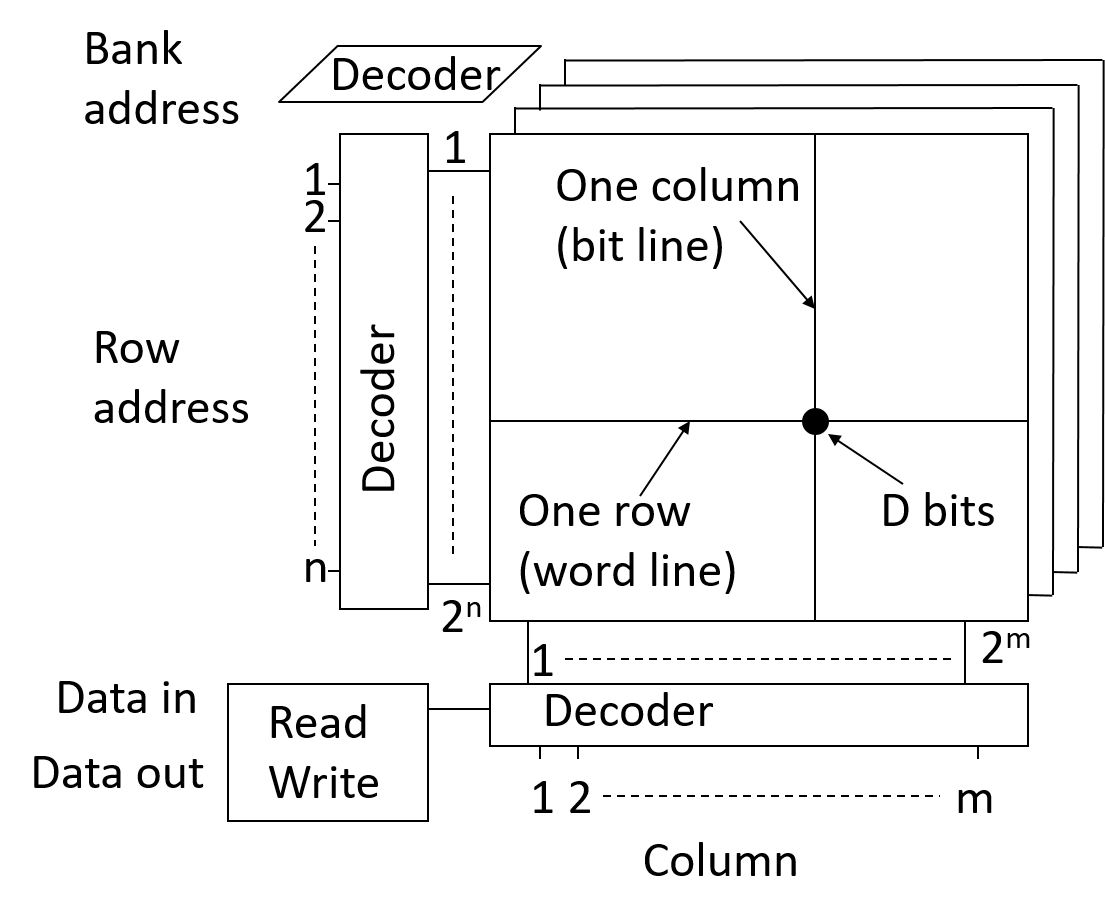

Zellenfelder: grosse Speicher

|

|

Memory Array

Size = B · D · 2n · 2m

Kenngr÷▀en von Speichern

- Wortbreite in Bit

- Speicherkapazitõt in Bit (Abk. b) oder Byte (Abk. B):

k(ilo) =210 =1024, M(ega) = 220 =1048576, G(iga) = 230 , T(era)=240, P(eta)=250 - Elektrische Verlustleistung

- Speicherzugriffszeit

- Speicherzykluszeit

- Data Retention

- Endurance

Storage device

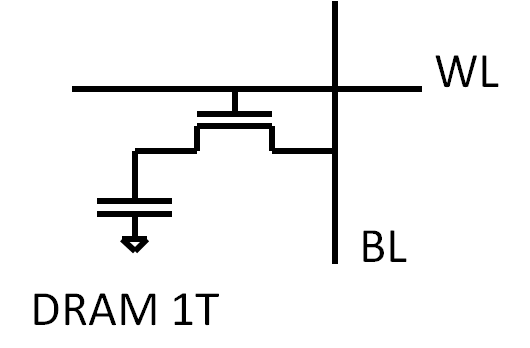

DRAM (capacitor)

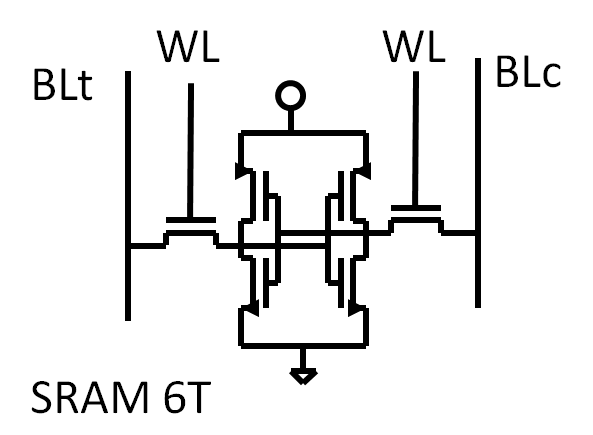

SRAM (latch of transistors)

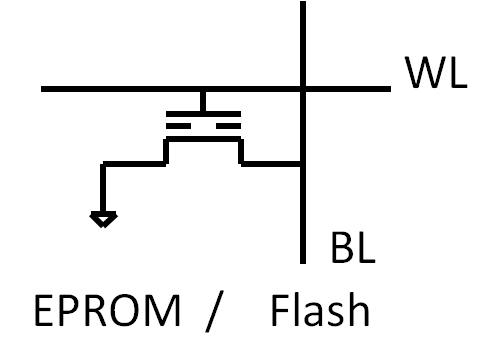

Flash (transistor with floating gate)

FRAM (Ferro Electric hysteresis)

MRAM (Resistance change due to magnetization)

PCRAM (resistance change due to solid/solid transition)

Needed Area

DRAM: 6F2 one capacitor + 1 select device: 1T + capacitor

SRAM: 256F2 4 transistors + 2 select devices: 6 T

Flash: 4F2 (16 level: 1F2) 1 Transistor with floating gate: 1T

Volatile versus nonvolatile memories

Information loss: Volatile versus nonvolatile memories

SRAM, DRAM lose information without power, Flash, EPROM and FRAM donÆt.

DRAM loses information without constant refresh of memory cells.

Speicher: Anwendungen (Application)

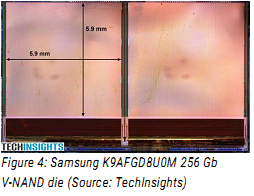

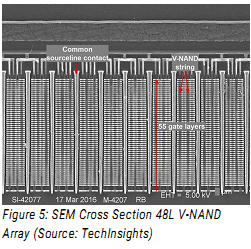

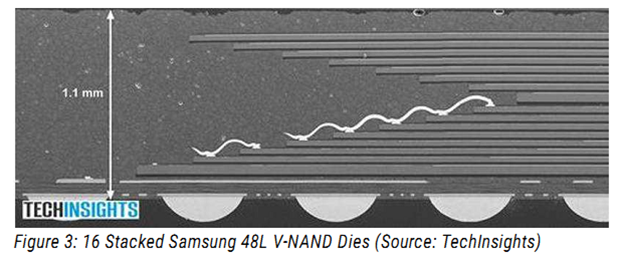

Samsung 21nm 48L V- 256Gb NAND Flash memory in 2TB SSD

Update 2020:

512 Gb .. 1 Tb Chip 120/128 Layer 4 Level pro Zelle 1 GB Micro SD Card: 360 € 12/2/2020 Intel N28A die, 29F04T2ANCQJ1 package, 2nd 3D QLC NAND die from Intel and 1024 Gb (1 Tb) with 96L NAND array. http://www.techinsights.com/techservices/TechInsights-Samsung-48L-3D-V-NAND.pdf

In diesem Beispiel wird die Integrationsdichte nicht nur durch die kleinste Strukturgrõ▀e F lateral bestimmt.

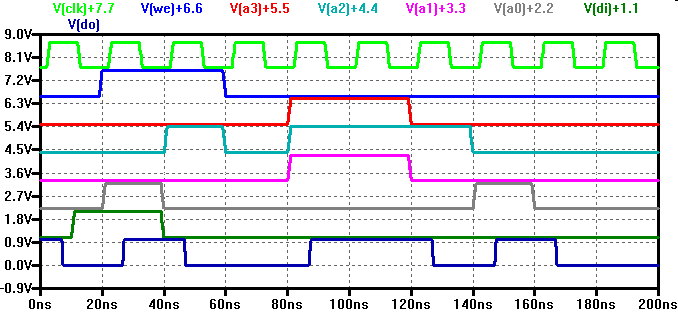

Mehrere Bits werden in einer Speicherzelle gespeichert. Mehrere Speicherzellen sind vertikal ³bereinander angeordnet. Mehrere Chips werden in ein Gehõuse montiert. Dadurch ist es m÷glich auch ohne Strukturverkleinerung mehr Funktionalitõt pro Volumen zu realisieren. Speicherzellenfeld SRAMSimulationCLK high activates switches to select a memory cell and read and writeSequence Op,Addr,Data: R,0,0; W,1,1; W, 4,0; R,0,0; R,E,1; R,E,1; R,4,0; R,1,1; R,0,0;R,0,0 Verz÷gerungszeit 4ns von der steigenden CLK Flanke bis zum Datum.

Da es 10 CLK high Zeiten gibt werden 10 Operationen durchgef³hrt.

Diese sind oben aufgelistet: R,1,0 Lesen einer "0" an der Addresse 0. Jede Operation dauert 20ns. Bei den Leseoperationen kann man die Zugriffszeit zwischen CLK rising und do-─nderung sehen. Durch die Schreib- (W), Leseoperation (R) ³berpr³ft man die Speicherung der Information in der Zelle. VHDL-Code: ROM

VHDL-Code: RAM 01

VHDL-Code: RAM 02

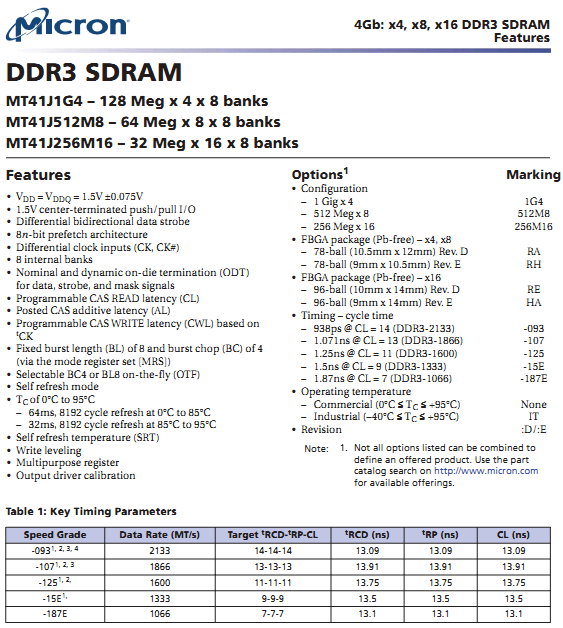

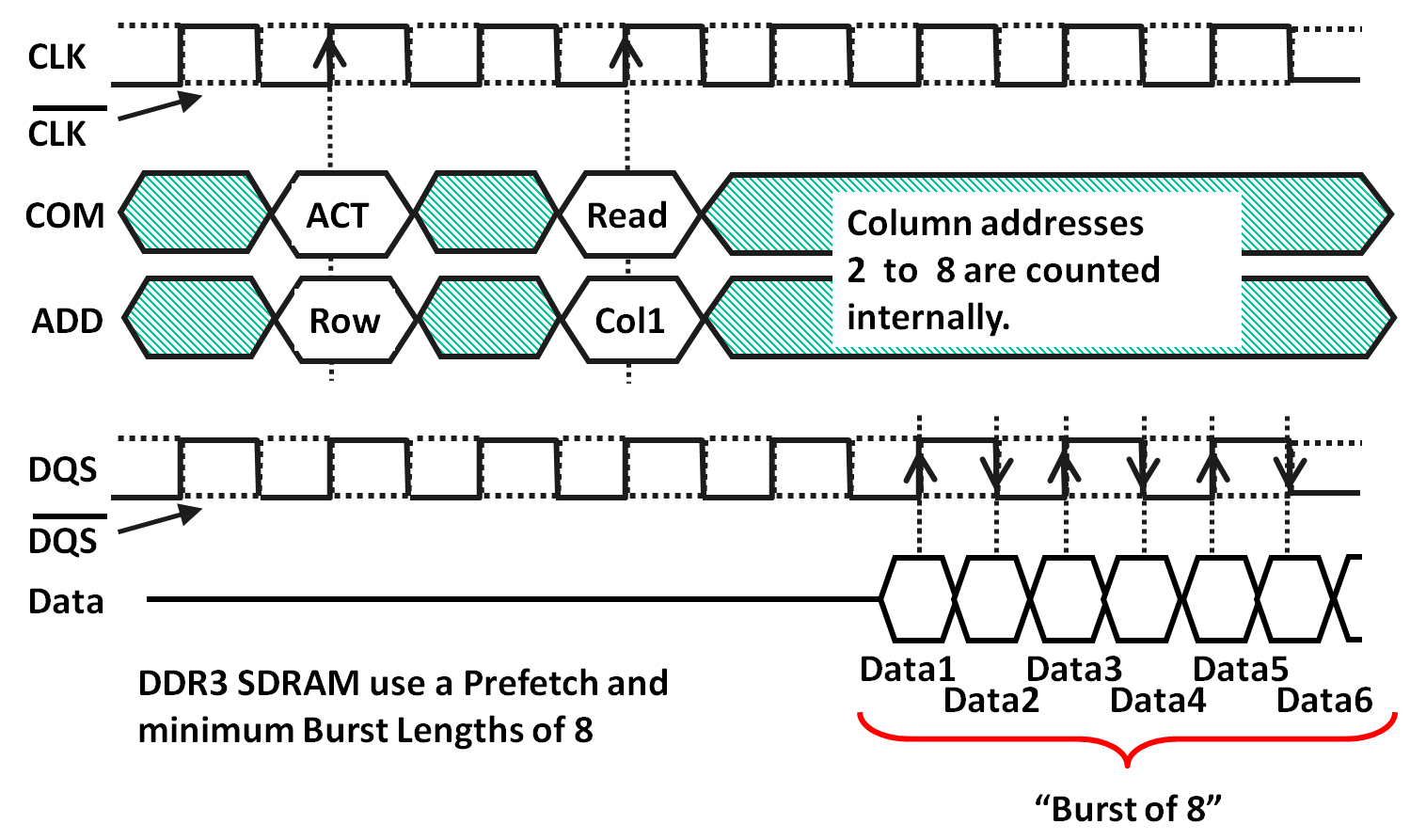

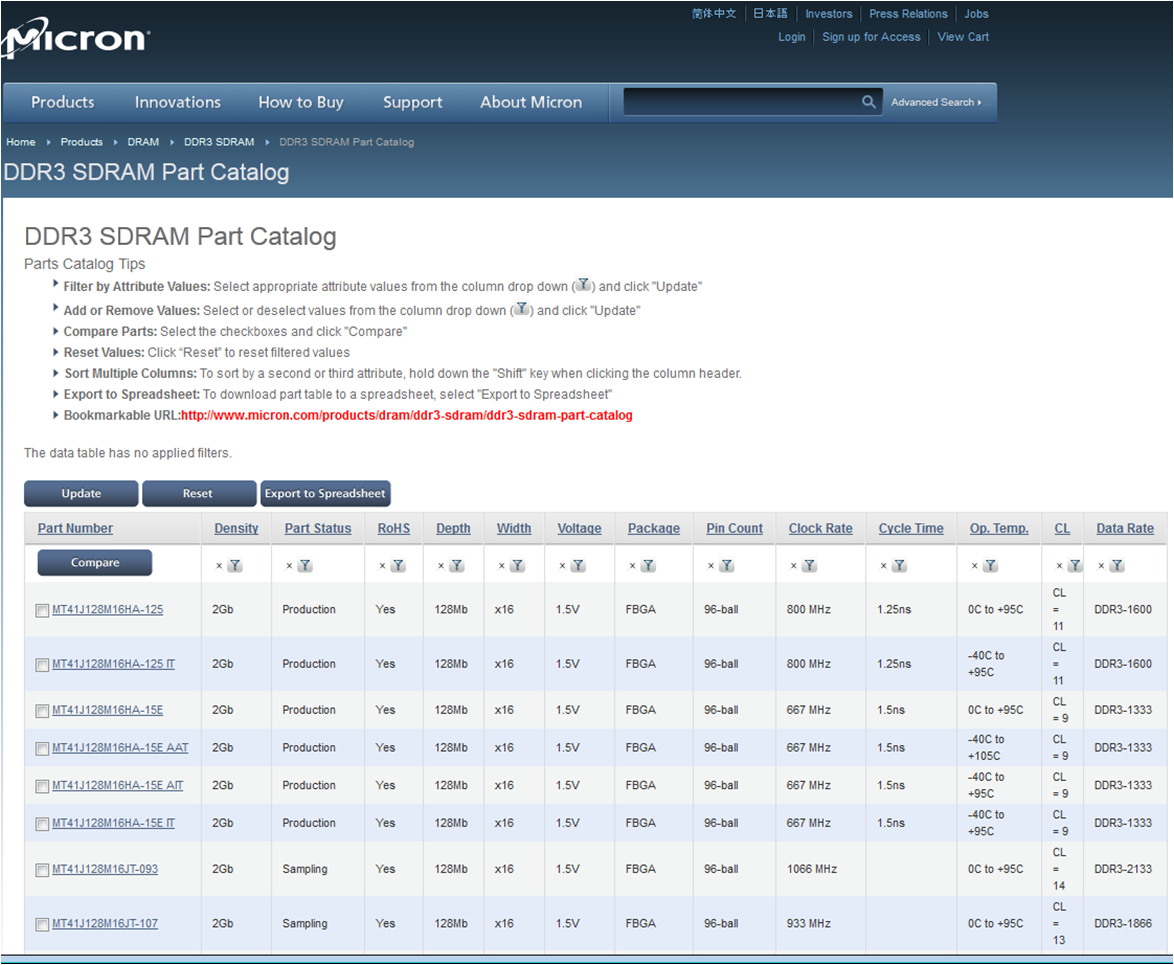

DDR3 SDRAM Access

Cycle time:

Latency: DDR3 Datasheet DRAM memory manufacturer: Samsung, Hynix, Micron DDR3 Datasheet Details

Aufgaben 01Es soll ein 64MBit Speicher mit 8 Datenleitungen realisiert werden. Wie viele Adressleitungen werden ben÷tigt?Ein Digitalbaustein hat 4 Eingõnge, ein Register mit 4 Bit Speicherzellen und 5 Ausgõnge. Wie viele Tests oder Zeilen der Zustandstabelle (Vektoren) brauchen Sie, um die logische Funktion des Bausteins vollstõndig zu testen? Aufgabe 02a) Erstellen Sie die Zustandstabelle f³r folgenden VHDL Code.b) Wie viele Eingõnge, Ausgõnge und Speicherzellen werden damit realisiert?

Aufgabe 02 aErstellen Sie die Wahrheits-/Zustandstabelle.

Aufgabe 02 bZeichnen Sie das Zeitverhalten.

Fragen und Diskussion

13 MP3 Player LFS

DRAM, SRAM, Flash, Memory Array, Volatile Memory, Cache, Hard Disk Memory, SDRAM,

Latency, Burst, Samsung, Micron, VHDL 'generic' Deklaration, VHDL Zahlenzuweisung

Hochschule für angewandte Wissenschaften Kempten, Jörg Vollrath, Bahnhofstraße 61 · 87435 Kempten

Tel. 0831/25 23-0 · Fax 0831/25 23-104 · E-Mail: joerg.vollrath(at)fh-kempten.de Impressum

|