Digitaltechnik11 Modulo 5 Z‰hlerProf. Dr.Jˆrg Vollrath10 Zustandsmaschinen |

|

Ein kurze Videozusammenfassung der Vorlesung

L‰nge: 6:23 min

Ein kurze Videozusammenfassung der Vorlesung

L‰nge: 7:41 min

Zeitverhalten einer VHDL-Beschreibung

L‰nge: 6:03 min

R¸ckblick und Heute

R¸ckblick:

- VHDL Beschreibung eines Schaltwerkes

- Abfrage eines Tasters

- Hierarchie in VHDL

- Zustandsmaschinen

Heute:

- Zustandsdiagramme

- Modulo 5 Z‰hler

- Spezifikation: Symbol, Zeitverhalten

- Zustandsdiagramm, Zustandstabelle, Minimalform

- VHDL Beschreibung und Test

- Schaltplan, LTSPICE und Test

- Ampelsteuerung, MP3 player

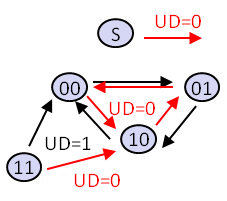

Zustandsdiagramm, Zustandsgraph

|

|

Ein Zustandsdiagramm benˆtigt immer eine Legende, damit man weiss was dargestellt wird.

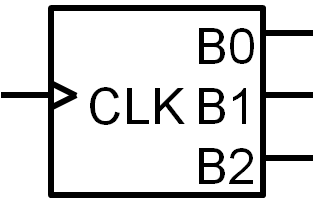

Modulo 5 Z‰hler: Aufgabenstellung

Bauen Sie einen Modulo 5 Z‰hler.|

Modulo 5 Z‰hler: 0,1,2,3,4,0,1,2,3,4,0.. CLK Mit jeder steigenden Flanke wird Eins hochgez‰hlt Taktteiler: Drei FF werden benˆtigt. |

|

Dies ist eine offen Aufgabenstellung. Die Spezifikation ist unvollst‰ndig.

Impliziert wird eine Taktsteuerung.

Steuert das Taktsignal das Z‰hlen oder ein enable Eingang (CE)?

Impliziert wird eine Taktsteuerung.

Steuert das Taktsignal das Z‰hlen oder ein enable Eingang (CE)?

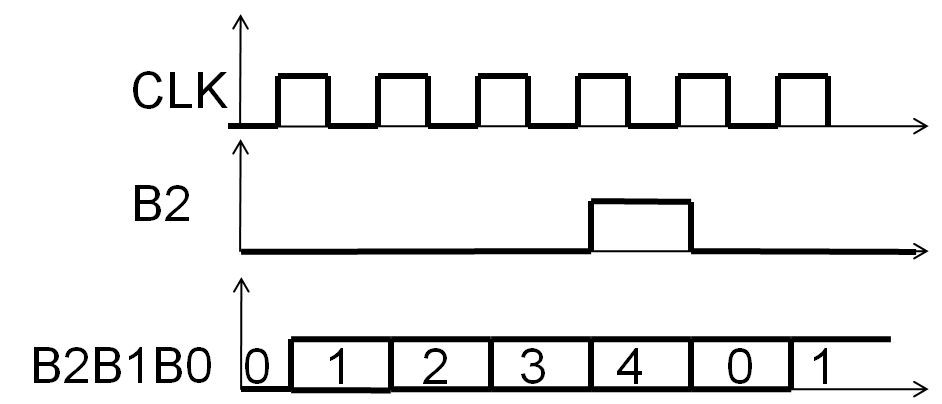

Modulo 5 Z‰hler: Zustandsdiagramm

|

3 Speicherzellen 8 Zust‰nde 5 Zust‰nde werden benutzt. Kein Signal an den Pfeilen, da die Zustands‰nderung auf jeden Fall durchgef¸hrt wird. |

|

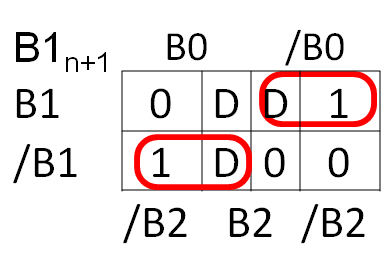

Modulo 5 Z‰hler: Zustandstabelle

Eine Zustandstabelle wird erzeugt und mit Karnaugh Veitch minimiert.

|

B0n+1=/B0n·/B2n  B1n+1=(B0n·/B1n) + (/B0n·B1n)  B2n+1= B0n·B1n |

Modulo 5 Z‰hler: Schaltungsrealisierung

LTSPICE code

Man sieht eine typische Medwedew-Zustandsmaschine.

Die Ausg‰nge werden f¸r die Erzeugung des n‰chsten Zustands invertiert und nichtinvertiert

links bereitgestellt.

Die disjunktive Normalform wird durch NAND Gatter in der Mitte dargestellt.

Je nach logischer Verkn¸pfung werden mehrere NAND Gatter zusammengeschaltet und mit den entsprechenden Signalen verbunden.

Die disjunktive Normalform wird durch NAND Gatter in der Mitte dargestellt.

Je nach logischer Verkn¸pfung werden mehrere NAND Gatter zusammengeschaltet und mit den entsprechenden Signalen verbunden.

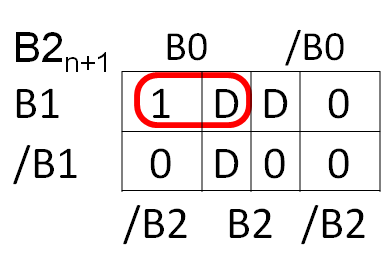

Modulo 5 Z‰hler: Schaltungssimulation

LTSPICE code

In der Simulation sieht man das CLK-Signal, clr, und die Z‰hlerausg‰nge b0, b1, b2.

Am Anfang kann man sehen wie b2 durch das clr-Signal "1" auf "0" gesetzt wird.

Dann sieht man das Hochz‰hlen von b2,b1,b0 bei steigender CLK-Flanke.

000, 001, 010, 011, 100, 000,...

Das clr-Signal bei 0.8us setzt b0 und b1 auf "0" zur¸ck.

Am Anfang kann man sehen wie b2 durch das clr-Signal "1" auf "0" gesetzt wird.

Dann sieht man das Hochz‰hlen von b2,b1,b0 bei steigender CLK-Flanke.

000, 001, 010, 011, 100, 000,...

Das clr-Signal bei 0.8us setzt b0 und b1 auf "0" zur¸ck.

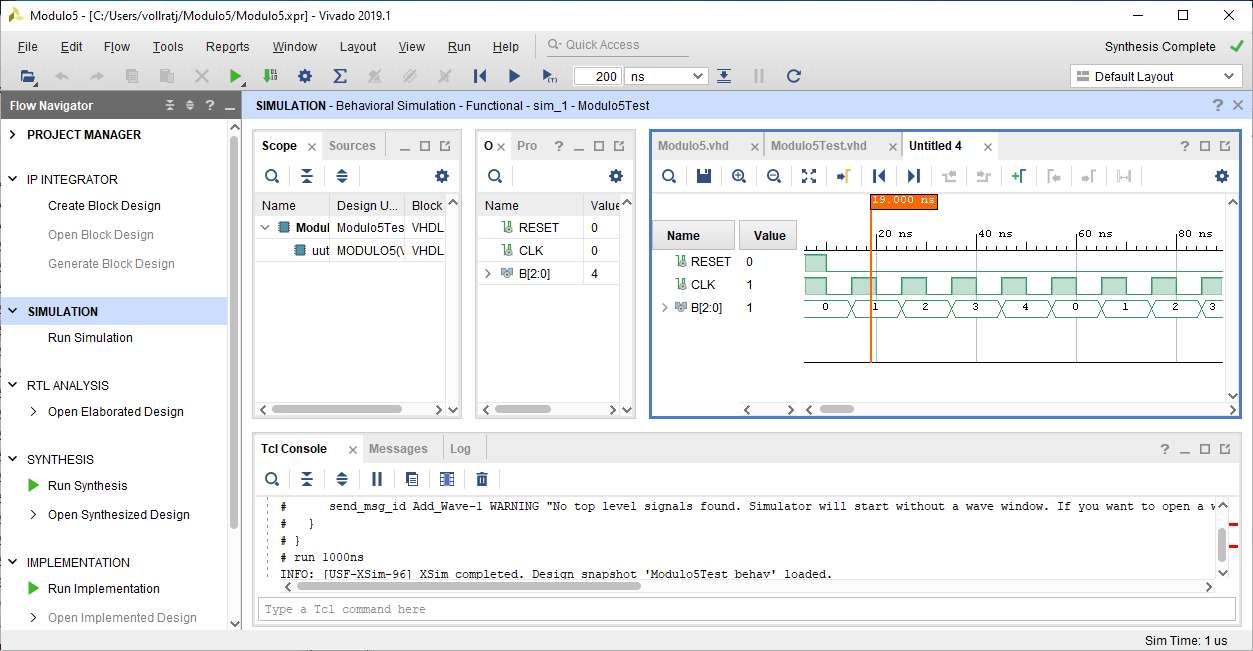

Modulo5: VHDL code

Als Basis dient der Code des D-Flip-Flops und der Code f¸r eine Wahrheitstabelle.

entity MODULO5 is

port (

RESET,CLK : in STD_LOGIC;

B: out STD_LOGIC_VECTOR(2 downto 0));

end MODULO5;

architecture VERHALTEN of MODULO5 is

signal BINT: STD_LOGIC_VECTOR(2 downto 0);

Modulo 5 VHDL code (2)

begin

SYN_COUNT:process (CLK, RESET)

begin

if RESET = '1' then

BINT <= "000";

elsif CLK='1' and CLK'event then

case BINT is

when "000" => BINT <= "001";

when "001" => BINT <= "010";

when "010" => BINT <= "011";

when "011" => BINT <= "100";

when "100" => BINT <= "000";

when others => BINT <= "000";

end case;

end if;

end process SYN_COUNT;

B <= BINT;

end VERHALTEN;

RESET Signal wurde eingef¸hrt.

Sicherer Zustand "000" f¸r den Fall others.

Ein Test benˆtigt nur die CLK. Diese wird meist automatisch erzeugt.

Sicherer Zustand "000" f¸r den Fall others.

Ein Test benˆtigt nur die CLK. Diese wird meist automatisch erzeugt.

Kommentare zum VHDL Code

- Synchron versus Asynchron

- Busse: BINT: std_logic_vector(2 downto 0)

- Busse und einzelne Leitungen:

A <= BINT(3);

Q (1 downto 0) <= BINT(2 downto 1);

Ziel Quelle - Signalfluss: Quelle zum Ziel

- Process

- Sequentielle Abarbeitung

- Vorteil: Lesbarkeit

- Nachteil: Implizite Register, Speicherzellen

- If, case Anweisung

Test Modulo5: VHDL code

entity Modulo5Test is

-- Port ( );

end Modulo5Test;

architecture Behavioral of Modulo5Test is

COMPONENT MODULO5

port (

RESET,CLK : in STD_LOGIC;

B: out STD_LOGIC_VECTOR(2 downto 0)

);

end COMPONENT;

-- Inputs

signal RESET,CLK : STD_LOGIC;

-- Ouputs

signal B: STD_LOGIC_VECTOR(2 downto 0);

Test Modulo5: VHDL code (2)

begin

uut: MODULO5 PORT MAP( RESET => RESET, CLK => CLK,

B => B );

clk_proc: process -- Clock process

begin

CLK <= '0'; wait for 5 ns;

CLK <= '1'; wait for 5 ns;

end process;

stim_proc: process -- Stimulus process

begin

reset <= '1'; wait for 10 ns;

reset <= '0'; wait for 10 ns;

wait;

end process;

end Behavioral;

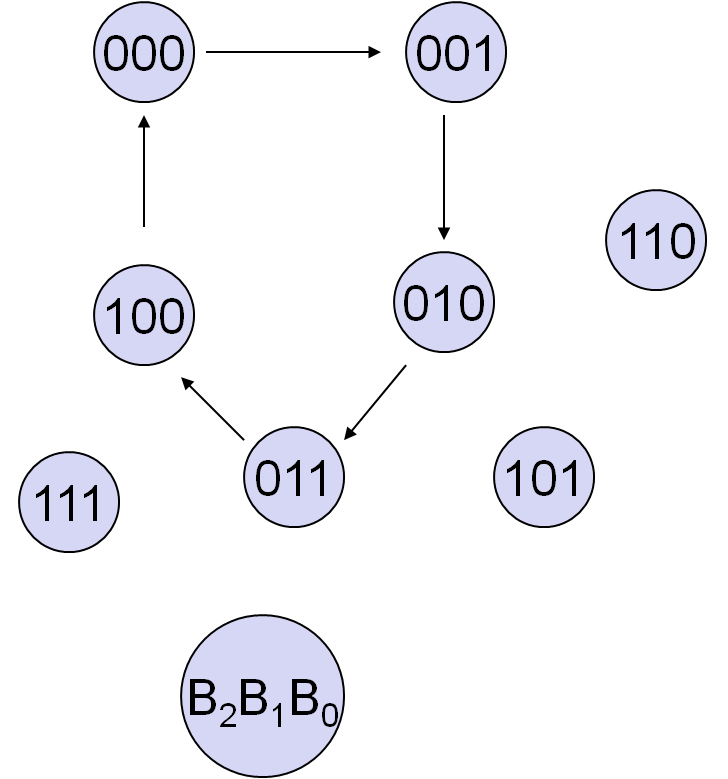

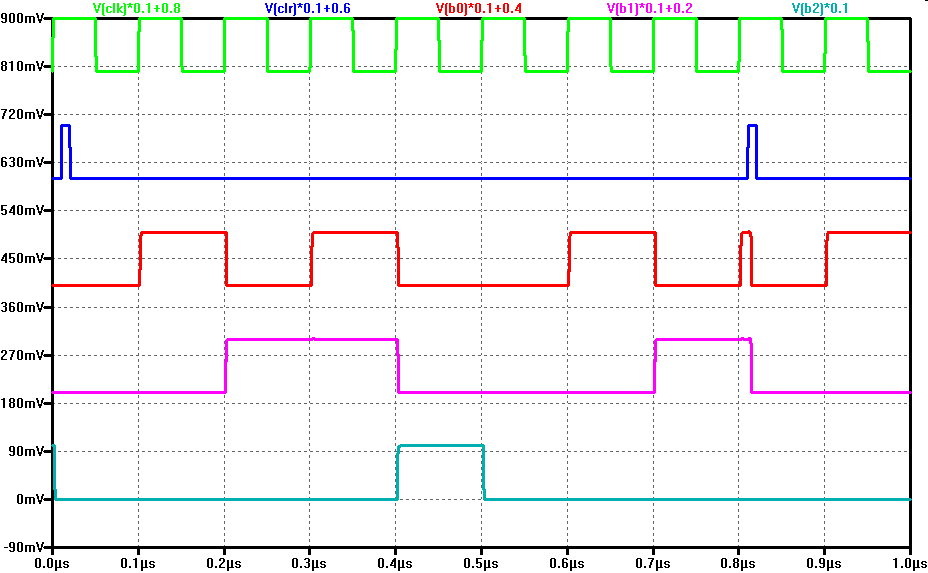

Modulo 5 simulation output

Rezept f¸r Digitaltechnik

- Lege eine Dokumentation an und erfasse jeden Schritt

- Identifiziere Eing‰nge, Zust‰nde und Ausg‰nge im Text

- Identifiziere unvollst‰ndige oder fehlende Informationen

- Vergebe Namen und Zuordnungen: Button B, '1' An, '0' Aus

- Evtl: Zerlege das Problem in Teilprobleme und starte zur Bearbeitung von Teilproblemen neu

- Erstelle eine Zustandstabelle:

Zustandsgleichungen, Zustandsdiagramm - Erstelle einen Schaltplan und Eingangssignale und simuliere.

Alle Zustandskombinationen und Eingangskombinationen m¸ssen getestet werden. - Erstelle VHDL code f¸r die Zustandstabelle und Eingangssignale und simuliere

- Ðberpr¸fe die korrekte Funktion

- Reflektiere 'lessons learned' in einer Zusammenfassung

- Gratulation zum Ergebnis

Fragen und Diskussion

|

12 Speicherfelder

Zustandsdiagramm, Modulo 5 Z‰hler, Karnaugh Veitch, process,

Hochschule für angewandte Wissenschaften Kempten, Jörg Vollrath, Bahnhofstraße 61 · 87435 Kempten

Tel. 0831/25 23-0 · Fax 0831/25 23-104 · E-Mail: joerg.vollrath(at)fh-kempten.de

Tel. 0831/25 23-0 · Fax 0831/25 23-104 · E-Mail: joerg.vollrath(at)fh-kempten.de

Impressum