Digitaltechnik14 Busse VGAProf. Dr.Jörg Vollrath13 MP3 Player und LFSR |

|

Ein kurze Videozusammenfassung der Vorlesung

Länge: 7:25 min

Ein kurze Videozusammenfassung der Vorlesung

Länge: 8:59 min

Eine Zustandsdiagramm einer Schaltung

Länge: 6:03 min

Rückblick und Heute

Rückblick:

- Praktikum

- MP3 Player

- Shift register, LFSR

Heute:

- VGA Ansteuerung

- Busse

- Schieberegister: Parallel-Serien-Umsetzer

- OSI Schichtenmodell

- Datenprotokoll

Lesen: Reichardt: Kap 15

VGA Controller

- A VGA display should show 60 frames of 640 by 400 pixels per second.

Missing information:

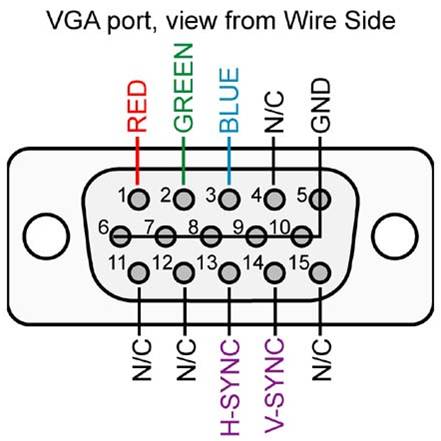

VGA display standard with input names:

R,G,B, HSYNC,VSYNC

FPGA system clock: 50MHz

Das folgende Bild zeigt die Steckerbelegung mit den HSYNC und VSYNC Signalen, Red, green, blue und Masse (GND).

VGA display standard with input names:

R,G,B, HSYNC,VSYNC

FPGA system clock: 50MHz

Das folgende Bild zeigt die Steckerbelegung mit den HSYNC und VSYNC Signalen, Red, green, blue und Masse (GND).

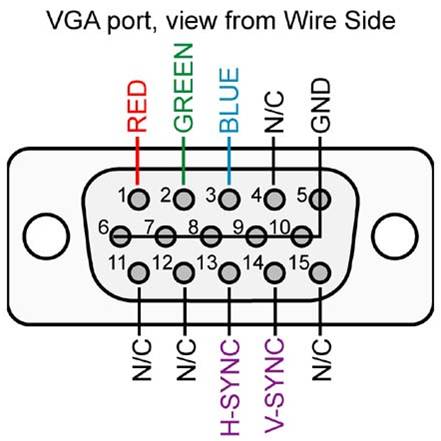

Signale für ein Bild mit 2 Zeilen und 6 Pixeln

Das Bild zeigt die serielle Übertragung eines Videosignals. Die Pixel werden seriell, nacheinander Übertragen.

Es wird ein Zähler verwendet. Der Bereich des Zählers kann sehr gross werden: 1920 x 1080 ≈ 4MBit = 2 22

Der Zähler wird aufgeteilt in einen Pixelzähler (px) und einen Zeilenzähler (py).

Je nach Zählerstand wird HSYNC, VSYNC und die Pixelposition px, py ausgegeben.

Es wird ein Zähler verwendet. Der Bereich des Zählers kann sehr gross werden: 1920 x 1080 ≈ 4MBit = 2 22

Der Zähler wird aufgeteilt in einen Pixelzähler (px) und einen Zeilenzähler (py).

Je nach Zählerstand wird HSYNC, VSYNC und die Pixelposition px, py ausgegeben.

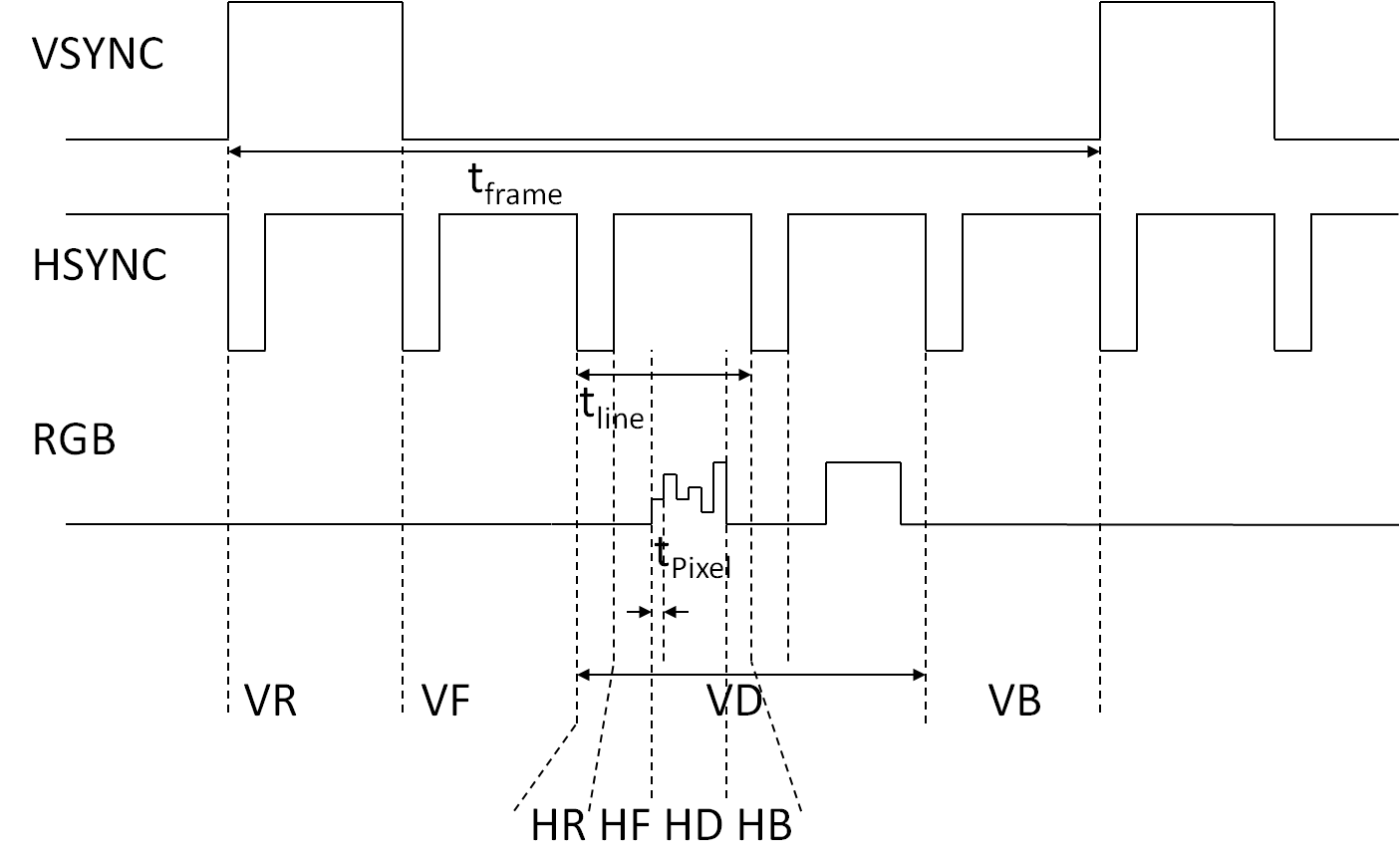

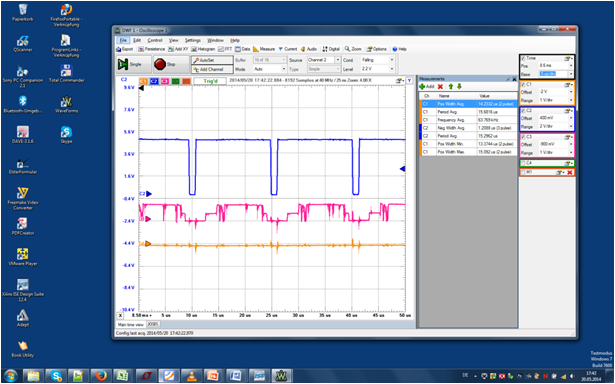

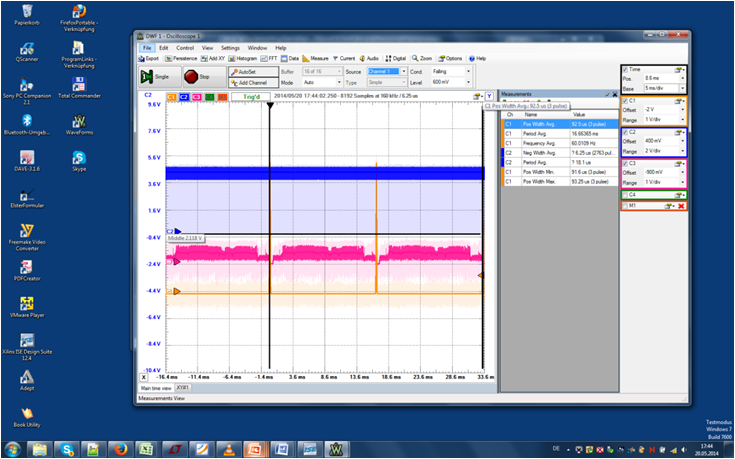

Demo Videosignal mit Y VGA Weiche und Electronic Explorer

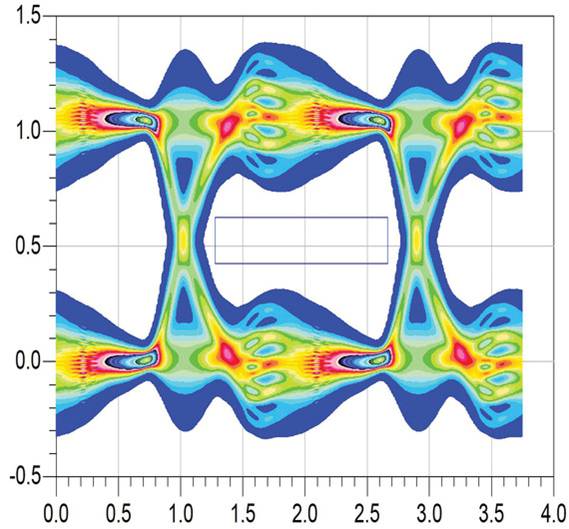

Signalmessung

|

|

Im linken Bild wird das HSYNC Signal (Blau) und das Rot Signal mehrerer Zeilen gezeigt.

Im rechten Bild kann man das gelbe VSYNC Signal erkennen. Durch die hohe Frequenz des HSYNC Signals wird es als blauer Bereich aufgelöst. Das Rotsignal bildet in einem Paket ein vollständiges Bild ab.

Wird das angezeigte Fenster verschoben, kann man das im Videosignal sehen.

Im rechten Bild kann man das gelbe VSYNC Signal erkennen. Durch die hohe Frequenz des HSYNC Signals wird es als blauer Bereich aufgelöst. Das Rotsignal bildet in einem Paket ein vollständiges Bild ab.

Wird das angezeigte Fenster verschoben, kann man das im Videosignal sehen.

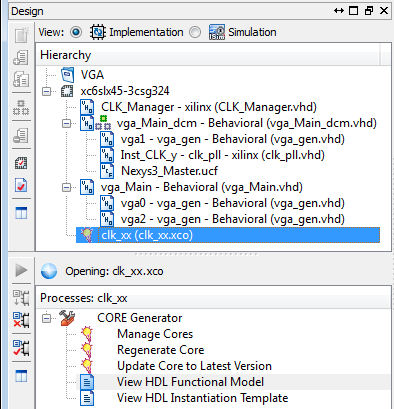

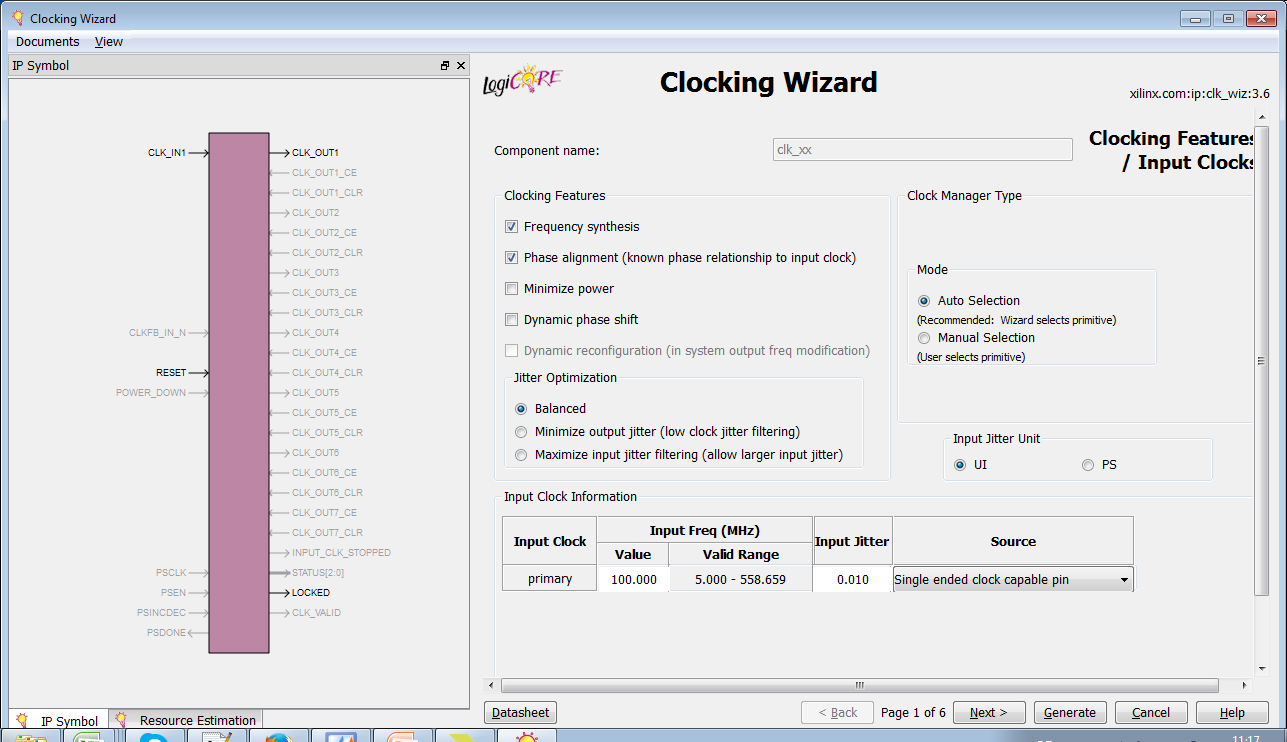

Core Generator Wizard

FPGAs bieten vorbereitete Digitalschaltungen. Um eine beliebige Pixelfrequenz zu erzeugen kann man eine vorhandene Taktschaltung im FPGA benutzen.

|

|

VGA Controller

entity vga_gen is

generic(

-- VGA 1920x1080 sync parameters 50MHz Clock 3.5 pixels at once -> 548 x 1080 bad ok

HD: integer := 548; -- horizontal display area 640; 800

HF: integer := 34; -- h. front porch (8) 16; 40

HB: integer := 93; -- h. back porch (56) 48; 88

HR: integer := 59; -- h. retrace 96; 128

-- VD+VF+VB+VR-1 -> 1087

VD: integer := 1080; -- vertical display area 480; 600

VF: integer := 1; -- v. front porch (2) 11; 4

VB: integer := 32; -- v. back porch (41) 31; 23

VR: integer := 3 -- v. retrace (2) 2; 1

);

port(

clk, not_reset: in std_logic;

hsync, vsync: out std_logic;

video_on, p_tick: out std_logic;

pixel_x, pixel_y: out std_logic_vector (11 downto 0)

);

end vga_gen;

Die Eingänge sind die externen clk und reset.

Mit generic wird die Auflösung des Bildes eingestellt.

Die richtige Pixelfrequenz p_tick wird erzeugt. Mit Hilfe der Zähler wird hsync und vsync generiert und im sichtbaren Bereich die Pixelposition pixe_x und pixel_y ausgegeben.

Zur Erzeugung eines Bildes wird pixel_x und pixel_y verwendet, um die Farbinformation zu bestimmen und an der Schnittstelle auszugeben.

Es kann ein Object mapping oder character ROM verwendet werden.

Beipiel code für ein NEXYS3 Board findet man unter: VGA Controller für NEXYS3 Board

Eine ausführliche Beschreibung kann man in folgendem Buch finden:

Mit generic wird die Auflösung des Bildes eingestellt.

Die richtige Pixelfrequenz p_tick wird erzeugt. Mit Hilfe der Zähler wird hsync und vsync generiert und im sichtbaren Bereich die Pixelposition pixe_x und pixel_y ausgegeben.

Zur Erzeugung eines Bildes wird pixel_x und pixel_y verwendet, um die Farbinformation zu bestimmen und an der Schnittstelle auszugeben.

Es kann ein Object mapping oder character ROM verwendet werden.

Beipiel code für ein NEXYS3 Board findet man unter: VGA Controller für NEXYS3 Board

Eine ausführliche Beschreibung kann man in folgendem Buch finden:

FPGA Prototyping by VHDL Examples:

|

|

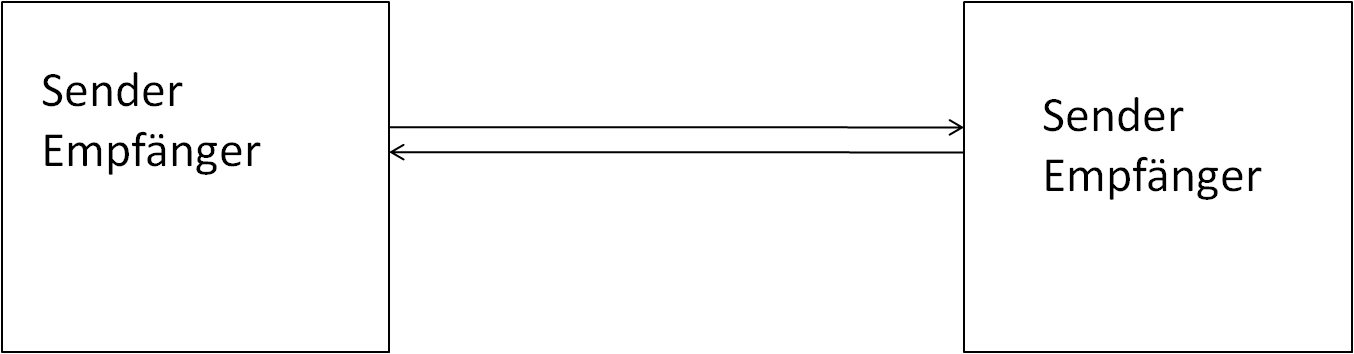

Bus Definition

|

|

Serielle Übertragungsprotokolle

- Der RS232C- bzw. COM-Standard des PCs dient der Kommunikation mit Peripheriegeräten.

- I˛C-Bus: Konfiguration von ICs

- CAN-Bus, Flex-Ray-Bus: Kommunikation von ICs in Kraftfahrzeugen

- SATA-Bus: schnelle Festplatten in PCs

- SPI-Bus: Kommunikation zwischen verschiedenen ICs.

- USB-Bus: Peripheriegeräte am PC

- Ethernet-Bus: Netzwerkkommunikation

- HDMI, DVI, Display Port Bus: Digitale serielle Grafikschnittstellen

Diskussion serielle Schnittstelle

|

|

OSI Schichtenmodell

Open Systems Interconnection Reference Model| OSI Schicht | Einordnung | Protokollbeispiel | Einheit | Kopplung | |

| 7 | Anwendung (Application) | Anwendungsorientiert | HTTP FTP SMTP |

Daten | Gateway, Content-switch |

| 6 | Darstellung (Präsentation) | ||||

| 5 | Sitzung (Session) | ||||

| 4 | Transport (Transport) | Transportorientiert | TCP, UDP | Router | |

| 3 | Vermittlung (Network) | IP | |||

| 2 | Sicherung (Data Link) | Ethernet, Token Ring | Rahmen, Frames | Bridge, Switch | |

| 1 | Bitübertragung (Physical) | Bits | Repeater, Hub | ||

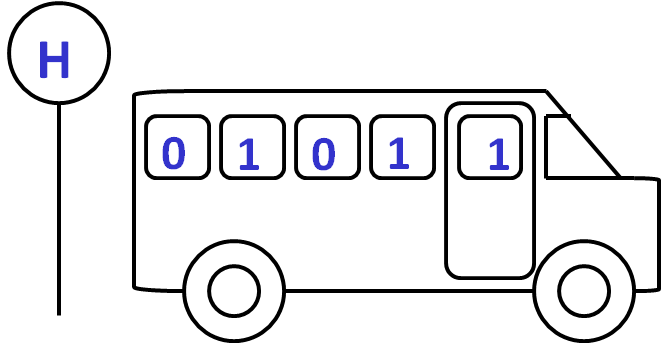

Asynchrone serielle Übertragung

- Punkt zu Punkt

- Möglichst wenige Leitungen -> Hohe Datenrate, Taktfrequenz

- Parallel Seriell Wandler

- Seriell Parallel Wandler

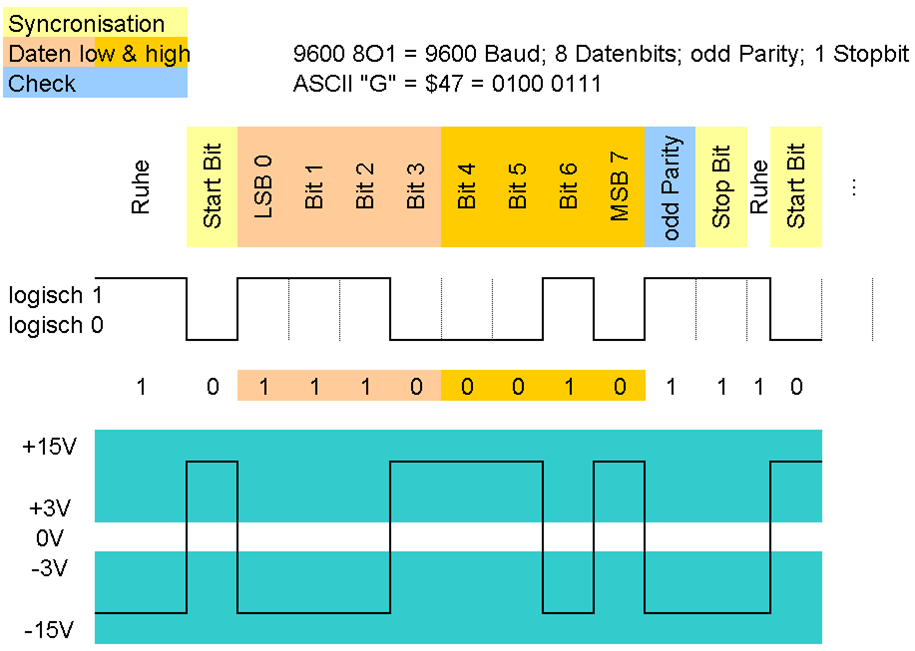

Schicht 1: UART

Universal, asynchronous receiver and transmitterBeispiel Übertragung des Zeichens "G"

Zustand, logische Information, Bit,Pegel

Baud Raten und Parity

Baud RatenSymbolrate Bitrate (bit/s); Bitdauer |

ParityFehlererkennung Anzahl der '1'er Even Parity (XOR) and odd NOT(XOR) parity |

Eigenschaften

|

|

Messung einer Datenübertragung

Fragen und Diskussion

|

15 Mikroprozessor

VGA, HSYNC, VSYNC, Bus, RS232, I2C, CAN, SATA, SPI, USB, Ethernet, HDMI, DVI,

Datenauge, OSI Schichtenmodell, UART, Parity, Baud Rate