Digitaltechnik15 MikroprozessorProf. Dr.J÷rg Vollrath14 Busse und VGA controller |

|

Ein kurze Videozusammenfassung der Vorlesung

Lõnge: 9:07 min

R³ckblick und Heute

R³ckblick:

- VGA Ansteuerung

- Busse

- Schieberegister: Parallel-Serien-Umsetzer

- OSI Schichtenmodell

- Datenprotokoll

Heute:

- Programmierbare Zustandsmaschine

- Mikroprozessor

Lesen: Reichardt: Kap 15

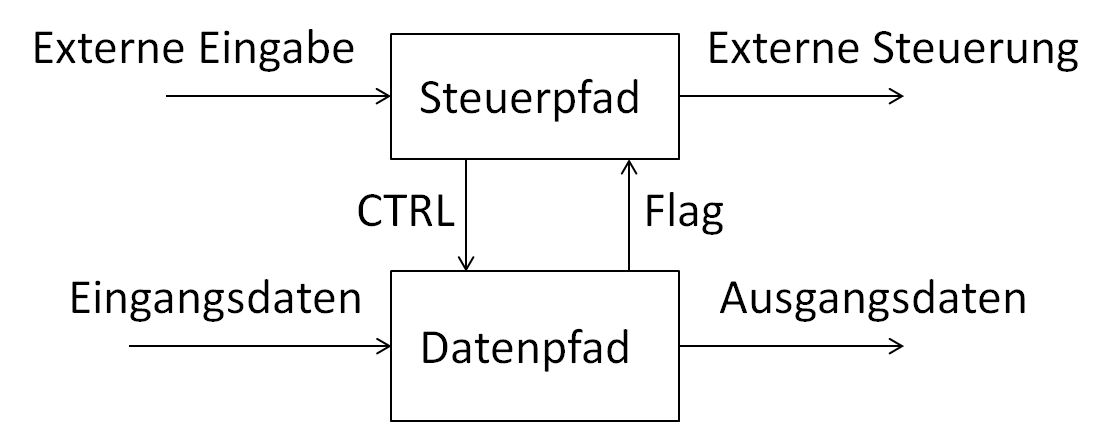

Programmierbare Zustandsmaschine: Daten und Steuerpfad

|

|

| |

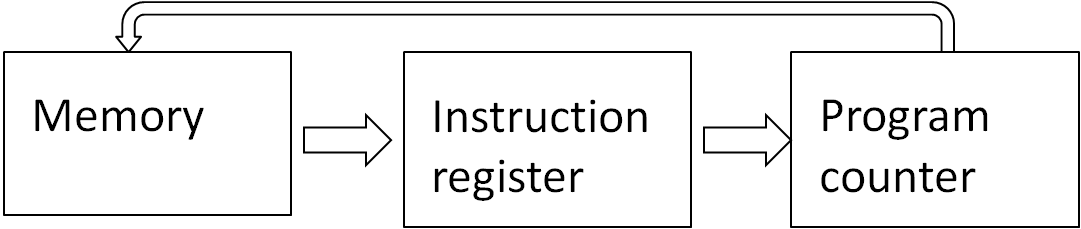

Mikroprozessor (Microprocessor)

State machine

Blocks:

|

Minimum Instruction Set

Extended Instruction Set

|

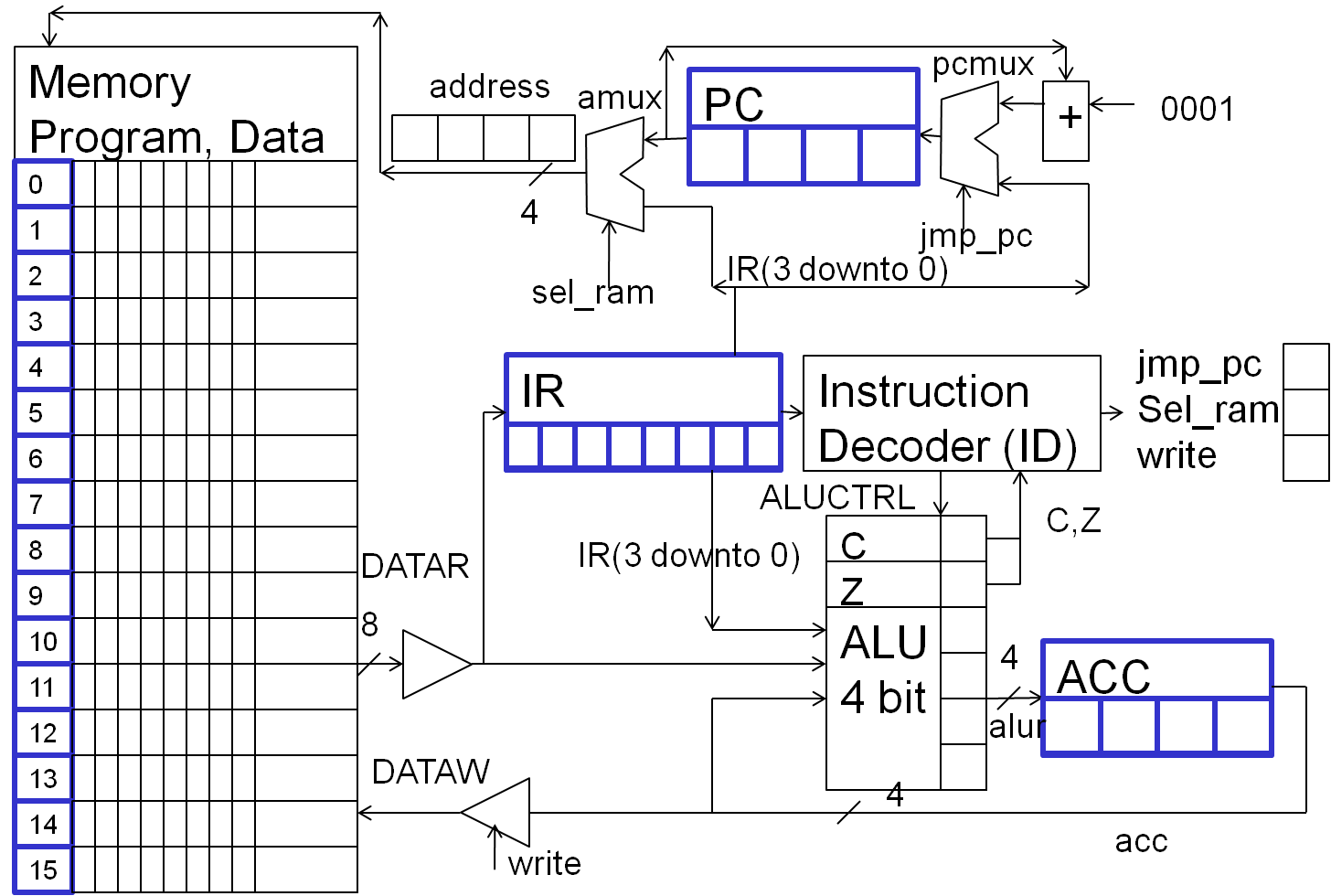

Mikroprozessor: Blockdiagramm

Fetch:

Das IR wird geladen.

Wenn Daten aus dem Speicher ben÷tigt werden, wird die Adresse entsprechend gesetzt.

Decode:

Entsprechend der Instruction (IR) werden die ALU und Steuersignale gesetzt.Execute:

Der PC und der ACC wird gesetzt.Small CPU Analysis

- System mit 2 Speicherzugriffen (Instructions, Data)

- Memory output: Fetch (Instruction)

- Instruction register: Decode (Data address)

- PC: Program counter Execute (Data, Instruction address)

- 1st simple solution

- 3 cycles per execution

- 2nd solution

- Pipeline with variable instruction length

Mikroprozessor: Minimum Instruction set

4 Bit ALU, 8 Bit Instructions| Kurzform | Aktion | Kommentar | |

| NOP | 0000 xxxx | NOP second cycle for RAM access | |

| Load Rd | 0001 d3d2d1d0 | ACC = ram[d3..d0] | Lade Daten aus dem Speicher in den Akkumulator |

| Load #d | 0010 d3d2d1d0 | ACC = d3d2d2d0] | Lade das Datum d3d2d1d0 in den Akkumulator |

| Store Rd | 0011 d3d2d1d0 | ram[d3..d0] = ACC | Speichere das Datum des Akkumulator im RAM Speicher |

| Add Rd | 0100 d3d2d1d0 | ACC = Acc + ram[d3..d0] | Addiere zum Akkumulator die Daten aus dem RAM an der Adresse d3d2d1d0. |

| Add #d | 0101 d3d2d1d0 | ACC = Acc + d3..d0 | Addiere zum Akkumulator die Daten d3d2d1d0 |

| Xor Rd | 0110 d3d2d1d0 | ACC = Acc xor ram[d3..d0] | Exclusiv ODER von Akkumulator und RAM Daten von der Adresse d3d2d1d0 |

| Cmp #d | 0111 d3d2d1d0 | Z = Acc - d3..d0, C = Acc - d3..d0 | Der Akkumulator wird mit d3d2d1d0 verglichen. Gleich Z =1, Acc < d3..d0 C=1; |

| Jmp #a | 1000 a3a2a1a0 | PC = a3 a2 a1 a0 | Der Programmzõhler wird auf d3d2d1d0 gesetzt. |

| JmpZ #a | 1001 a3a2a1a0 | PC = d3 d2 d1 d0 | Der Programmzõhler wird auf d3d2d1d0 gesetzt, wenn Z = 1. |

| JmpC #a | 1010 a3a2a1a0 | PC = a3 a2 a1 a0 | Der Programmzõhler wird auf d3d2d1d0 gesetzt, wenn C = 1. |

| JmpNC #a | 1011 a3a2a1a0 | PC = a3 a2 a1 a0 | Der Programmzõhler wird auf d3d2d1d0 gesetzt, wenn C = 0. |

| Clear C # | 1100 0000 | C = 0 | Carry wird auf Null gesetzt. |

| Set C # | 1100 0001 | C = 1 | Carry wird auf Eins gesetzt. |

| Not AC # | 1100 0010 | AC = Not(AC) | Der Akkumulator wird invertiert. |

| SHL AC # | 1100 0011 | ac3ac2ac1ac0 = ac2ac1ac0ac3 | Der Akkumulator wird nach links geschoben. |

| SHL AC C # | 1100 0100 | ac3ac2ac1ac0 = ac2ac1ac0C, C = ac3 | Der Akkumulator wird mit Carry nach links geschoben. |

Von der Programmiersprache zum 4-Bit Mikroprozessorcode

Javascript:

const A = 44;

const B = 102;

var Y = A + B;

Da die Zahlen gr÷▀er sind als 4-Bit, werden Sie in niederwertige 4-Bit und

h÷herwertige 4-Bit aufgeteilt.A = 44 = 2 * 16 + 12

B = 102 = 6 * 16 + 6

Das Beispiel zeigt. wie man auch mit einem 4-Bit Prozessor und Carry gr÷▀ere Zahlen verarbeiten kann.

Die Konstanten A und B werden direkt in die Assemblerbefehle codiert.

load #d 12 -- lower Nibble A add #d 6 -- lower Nibble B store Rd 12 -- Store in lower Nibble Y load #d 2 -- upper Nibble A add #d 6 -- upper Nibble B store Rd 13 -- Store in upper Nibble Y

Javascript Schleifen:

var S = 0;

for (var i = 0; i < 5; i++) {

if (i < 4) {

S = S + i;

} else {

S = S +2;

}

}

i bekommt die Speicherplatzadresse 13.

S bekommt die Speicherplatzadresse 14.

var S = 0;

for (var i = 0; i < 5; i++) {

if (i < 4) {

S = S + i;

} else {

S = S + 1 ;

}

}

Asssembler:

load #d 0 store Rd 14 ; S = 0 store Rd 13 ; i = 0 a1: Cmp #4; x < 4? JmpZ #addr a2 add Rd 14; store Rd 14 ; jmp a3; a2: load Rd 14; S = S + 1; add #d 1; store Rd 14; a3: load Rd 13; x + 1; add #d 1; store Rd 13; Cmp #5; x < 5? JmpZ #addr a1

Mikroprozessor: VHDL

Jedes Element im Blockschaltbild bekommt den entsprechenden VHDL code.| Block | Eingõnge: IN | Ausgõnge:OUT |

| RAM Modul: | ADDR(3..0), DATAW(3..0), WE | DATAR(3..0) |

| PC: | IR(3..0), sel_ram, jmp_pc | ADDR(3..0) |

| IR (7..0) | DATAR(7..0) | IR(7..0) |

| Logic: Instruction Decoder ID: | IR(7..0), C, Z | sel_ram, jmp_pc, ALU_CTRL() |

| Logic: ALU | DATAR(3..0), ALU_CTRL() | C, Z, DATAO(3..0) |

| ACC: | DATAO(3..0) | DATAW(3..0) |

Zur Beobachtung werden dann noch Eingõnge und Ausgõnge des Entwicklungsboards verbunden.

2 Taster werden f³r die Operationen 'Reset' und 'step' eingesetzt.

BTN():reset; BTN():step;

Die Zustõnde Fetch, Decode, Execute werden durch dp(0),dp(1) und dp(2) angezeigt.

Mit den Schiebeschaltern sw(0..4) wird die Darstellung auf den 4 Stellen der 7 Segment Anzeige ausgewõhlt:

BTN():reset; BTN():step;

Die Zustõnde Fetch, Decode, Execute werden durch dp(0),dp(1) und dp(2) angezeigt.

Mit den Schiebeschaltern sw(0..4) wird die Darstellung auf den 4 Stellen der 7 Segment Anzeige ausgewõhlt:

| sw | |

| 00000 | PC, IR, ACC |

| 00001 | address 0/jmp_pc/sel_ram/write 00CZ ALU |

| 1xxxx | Speicherinhalt der Adresse xxxx |

Mikroprozessor: VHDL Simulationsplan

Interessierende Signale:Register: PC,IR, ACC

RAM: addr, datar,dataw

Steuersignale: ALUCTRL, jmppc, selram, write

Simulation:

Alle Instruktionen werden getestet.

Bei Bedarf wird die Gesamtschaltung in Unterschaltungen zerlegt, die vorher getestet werden.

RESET: Adresse = 0; IR = 0 (Load 0); 2 Zyklen; (1) Neue Adresse Memory (2) Daten zum ACC

NOP: Adresse = 0 IR = x40,

Ld #8

Ld 13

St 14

Add 12

Add #1

Xor 3

Cmp #4

Jmp #4

...

Testing Small CPU

- Setze die Register. Aktiviere einen Clockzyklus und analysiere das Ergebnis:

- 16 Register, 16x8 Speicher: 216+2128 Testvektoren

- Boundary Scan: Setzen der Register

- Teilsysteme werden getestet

- Speicher, Programmadressgenerierung, Instruction Dekoder, ALU

- Gesamtsystem wird getestet

- Alle Instruktionen werden im RAM abgelegt

- F³r einen Test ben÷tigt man Eingangswerte und erwartete Ausgangswerte

- Spezifikation, Zustandstabelle

- Der Test kann bis zu 50% der Herstellungskosten verursachen

- Vorbereitung

- Durchf³hrung

Fragen und Diskussion

|

Instruction Set, Datenpfad, Steuerpfad, Akkumulator, CPU, Assembler