Übersicht

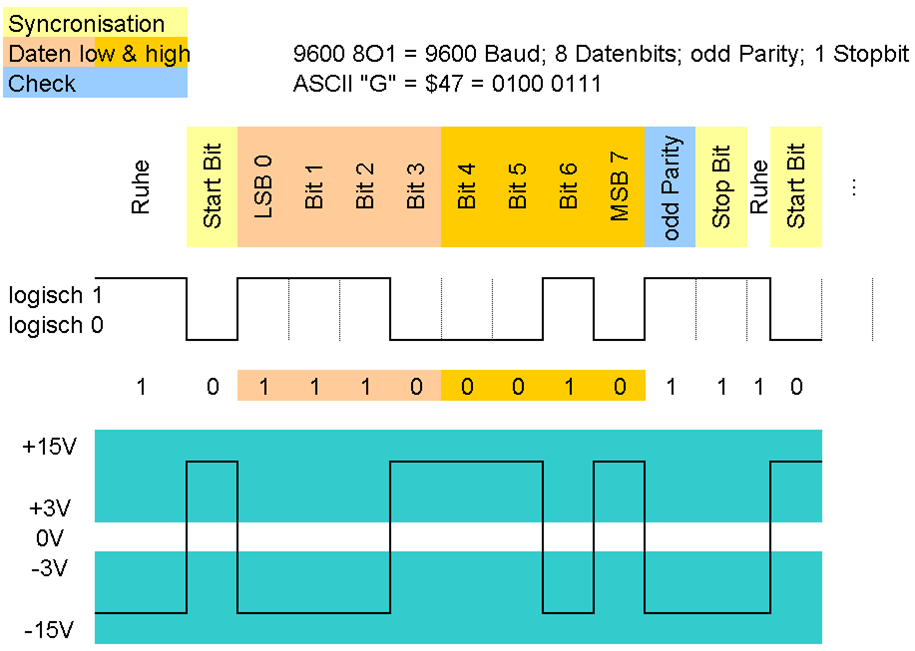

SPI und I2C Kommunikation

- Low level: Seriell, Baud rate, Anzahl Bits

- High level: Kommandos

- Arduino: Beispiel der erfolgreichen I2C und SPI Kommunikation

Messung der Kommandos und des Zeitverhaltens - Arduino: eingeschränkte Kommunikation

niedrige CLK Frequenz, baud rate, nur ein Kanal

- VHDL

- Copy, Paste, Test, Analyze, Modify, Repeat

- Modulo N Zähler: Zustandsmaschine

- Serial Parallel Converter

- I2C, SPI Interface

VHDL

VHDL: Wikipedia: Very High Speed Integrated Circuit Hardware Description LanguageTextuelle Beschreibung, Programmiersprache, Nebenläufigkeit

Verilog: Hardwarebeschreibungssprache

In dieser Vorlesung wird versucht mit minimalen Kenntnissen in begrenzter Zeit Hardware zu beschreiben und zu realisieren (FPGA).

Strategie

Kopieren, Modifizieren, TestenWas erwarten Sie von einer Programmiersprache?

Schlüsselwörter

Variablen, Typen

Zuweisungen

Struktur: Strichpunkte, Funktionen, Blöcke

Verzweigungen und Schleifen

Variablen, Typen

Zuweisungen

Struktur: Strichpunkte, Funktionen, Blöcke

Verzweigungen und Schleifen

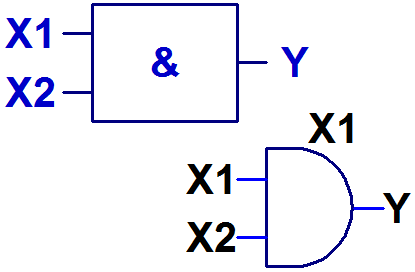

Darstellung boolescher Verknüpfungen

Schaltfunktion UNDY = f(x1,x2) = x1 ^ x2 = x1 · x2 Wahrheitstabelle

|

Schaltsymbol, Schaltverhalten

VHDL Beschreibung

|

VHDL Beschreibung

|

VHDL Beschreibung

|

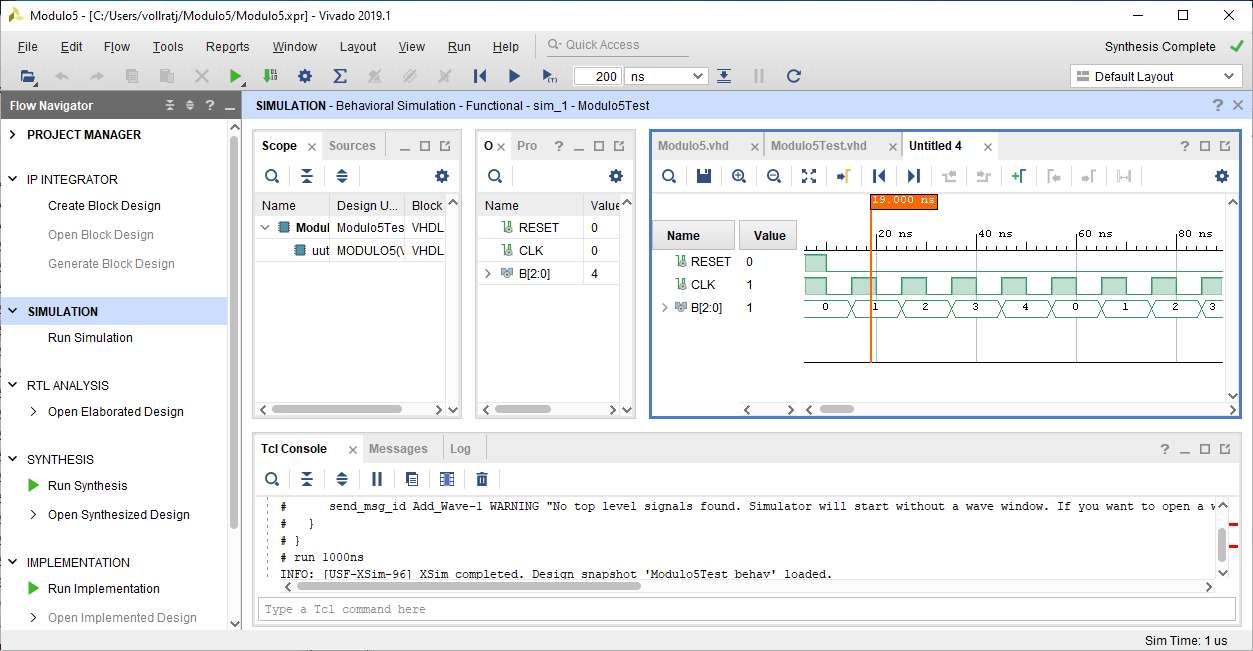

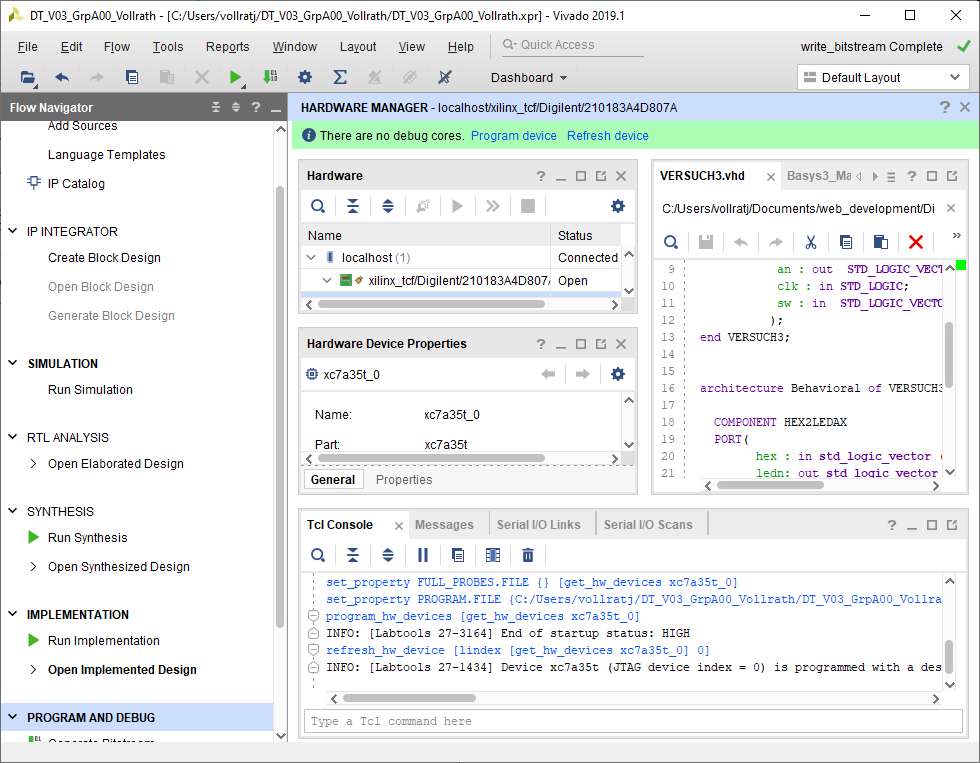

Entwicklungsumgebung (IDE)

Xilinx Vivado

Integrated development environment (IDE).

Entwicklungsumgebungen sehen alle sehr ähnlich aus und sind folgendermaßen aufgebaut:

Links gibt es den "Flow Navigator" der die Schritte Entwurf("IP Integrator"), Simulation und Hardware Konfiguration ("RTL Analysis", "Synthesis", "Implementation") bereitstellt.

Entwurf: Zusammenstellung von Schaltungen durch VHDL, Verilog oder vordefinierten Blöcken (IP-Catalog).

Simulation: Eine logische Schaltung wird mit geeigneten Stimuli (Eingangssignalen) simuliert.

Mit Hilfe der Simulation erzeugt man eine Wahrheitstabelle um die Schaltung zu verifizieren.

Hardware Konfiguration: Aus einer textuellen Beschreibung soll eine Konfigurationsdatei für einen Logikschaltkreis erzeugt werden.

Diese Punkte entsprechen dem Kompilieren und Debuggen einer Programmierumgebung.

In Abhängigkeit des Schrittes ändern sich die rechts daneben gezeigten Fenster.

Rechts ist der Texteditor mit Syntaxhighlighting.

Schlüsselwörter werden farbig hervorgehoben.

In der Mitte ist der Baum mit allen verwendeten Dateien.

Im unteren Bereich sieht man Statusmeldungen (Fehler).

Entwicklungsumgebungen sehen alle sehr ähnlich aus und sind folgendermaßen aufgebaut:

Links gibt es den "Flow Navigator" der die Schritte Entwurf("IP Integrator"), Simulation und Hardware Konfiguration ("RTL Analysis", "Synthesis", "Implementation") bereitstellt.

Entwurf: Zusammenstellung von Schaltungen durch VHDL, Verilog oder vordefinierten Blöcken (IP-Catalog).

Simulation: Eine logische Schaltung wird mit geeigneten Stimuli (Eingangssignalen) simuliert.

Mit Hilfe der Simulation erzeugt man eine Wahrheitstabelle um die Schaltung zu verifizieren.

Hardware Konfiguration: Aus einer textuellen Beschreibung soll eine Konfigurationsdatei für einen Logikschaltkreis erzeugt werden.

Diese Punkte entsprechen dem Kompilieren und Debuggen einer Programmierumgebung.

In Abhängigkeit des Schrittes ändern sich die rechts daneben gezeigten Fenster.

Rechts ist der Texteditor mit Syntaxhighlighting.

Schlüsselwörter werden farbig hervorgehoben.

In der Mitte ist der Baum mit allen verwendeten Dateien.

Im unteren Bereich sieht man Statusmeldungen (Fehler).

Beispiel: Logikfunktion

entity ANDX is

Port ( X : in STD_LOGIC_VECTOR (3 downto 0);

y : out STD_LOGIC);

end ANDX;

architecture Behavioral of ANDX is

signal H1:STD_LOGIC;

begin

h1 <= x(1) and x(2);

y<= (h1 or x(0)) and x(3);

end Behavioral;

Hier wird das Steuerwort 'signal' verwendet.

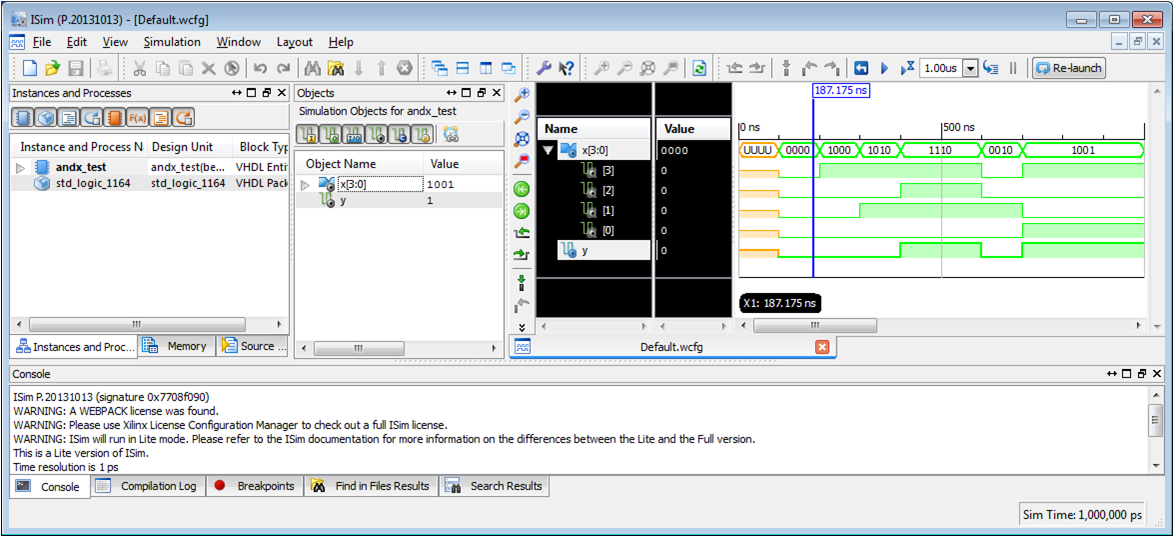

Test (1)

ENTITY ANDX_test IS

END ANDX_test;

ARCHITECTURE behavior OF ANDX_test IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT ANDX

PORT(

X : IN std_logic_vector(3 downto 0);

y : OUT std_logic

);

END COMPONENT;

--Inputs

signal X : std_logic_vector(3 downto 0); -- := (others => '0');

--Outputs

signal y : std_logic;

Die entity ANDX_test hat keine Eingänge oder Ausgänge.

In der Architecture findet man erst die verwendeten Komponenten (COMPONENT) und dann die Leitungen oder Register (signal).

In der Architecture findet man erst die verwendeten Komponenten (COMPONENT) und dann die Leitungen oder Register (signal).

Test (2)

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: ANDX PORT MAP (

X => X,

y => y

);

Als erstes wird die zu testende Schaltung (unit under test, uut) implementiert

und verbunden (PORT MAP).

Da die Schaltung ANDX mehrmals verwendet werden kann, wird dieser Instanz der name uut zugeordnet.

Da die Schaltung ANDX mehrmals verwendet werden kann, wird dieser Instanz der name uut zugeordnet.

Test (3)

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

wait for 100 ns;

-- insert stimulus here

x <= (others => '0'); wait for 100 ns;

x <= "1000"; wait for 100 ns;

x(1) <='1'; wait for 100 ns;

x(2) <='1'; wait for 200 ns;

x(3 downto 2) <= "00"; wait for 100 ns;

x <= "1001"; wait for 100 ns;

wait;

end process;

END;

Mit der Anweisung 'process' kann man eine Abfolge definieren.

Die 'wait' Anweisungen bestimmen das zeitliche Verhalten.

Die Anweisungen werden nacheinander von oben nach unten abgearbeitet.

Nur bei einer expliziten Zuweisung kann sich ein Signal ändern.

Die 'wait' Anweisungen bestimmen das zeitliche Verhalten.

Die Anweisungen werden nacheinander von oben nach unten abgearbeitet.

Nur bei einer expliziten Zuweisung kann sich ein Signal ändern.

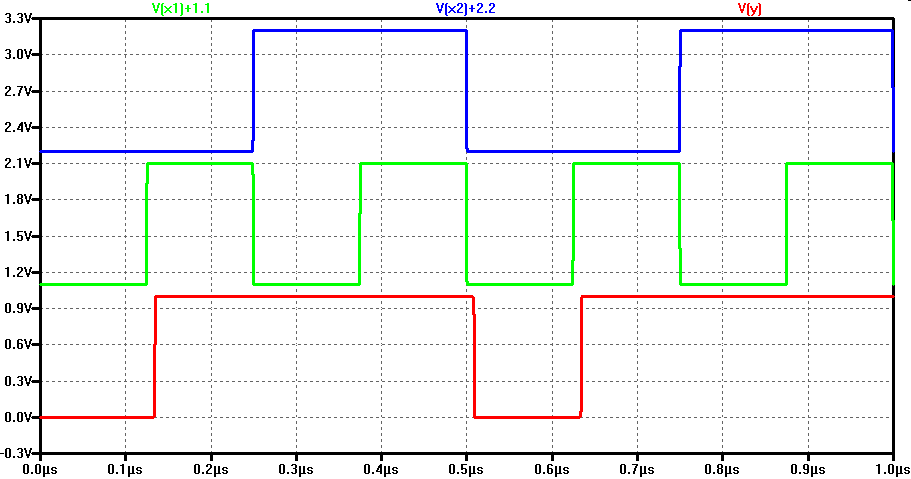

Simulationsergebnis

Schaltungsblöcke

Wiederverwendbarkeit, Componenten, mehrstufige Logik

- Component

- signal

- uut: ANDX port map ( X => X, Y => Y);

Die Entwicklungsumgebung generiert ein Template (leere Hülle) zum Test einer Schaltung.

Man muss nur die zeitliche Abfolge der Signale einfügen.

Man muss nur die zeitliche Abfolge der Signale einfügen.

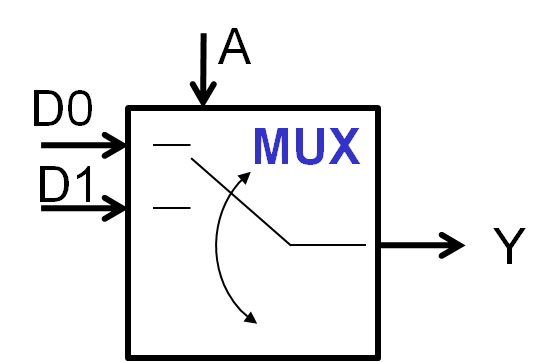

Ein Multiplexer in VHDL

|

|

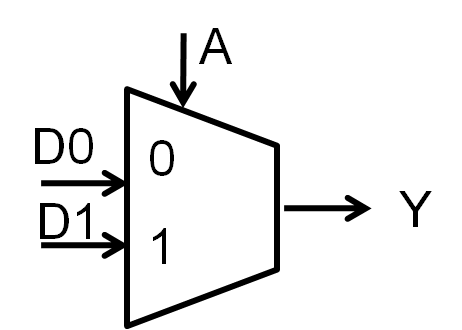

Multiplexer und Demultiplexer

Funktion:- Die Konzentration von n Leitungen auf eine Leitung: Multiplexer

- Die Verteilung von einer Leitung auf n Leitungen: Demultiplexer

Eingänge:

n Signale: D0..Dn-1

i = ld(n) Auswahlsignale: A0..Ai

Ausgang: Y

Anwendung

- Vermittlung von Telefongesprächen, Internetverbindungen

- Parallel-Serien- und Serien-Parallel-Umsetzung

- Mikroprozessor zur Auswahl der Verarbeitungsoperation

- Speicherglieder

2-1 Multiplexer

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||

|