Elektronik 317 Serien-Parallel WandlerProf. Dr.J—rg Vollrath16 Zustandstabellen |

|

pdf Vorlesung

Mitschrift der Vorlesung

Mitschrift der Vorlesung

Video der 17. Vorlesung (1.12.2021)

|

Lðnge: 1:11:00 |

0:00:00 Willkommen 0:0:10 Seriell-Parallelwandler 0:01:09 Schieberegister 0:03:34 Simulation 0:04:42 Asynchronous CLR 0:09:08 Setup und Hold Zeiten 0:15:03 Setup Zeit zwischen FlipFlops 0:17:13 Hold Zeiten 0:20:23 Zustandstabelle des Schieberegisters 0:21:03 Éberschrift Spalten 0:22:00 Anzahl Zeilen 0:22:18 Was fehlt? Das CLR 0:23:58 Diskussion Anzahl der Zeilen 0:27:52 Erstellung einer Zeile 0:28:38 Mehrere Wahrheitstabellen 0:29:43 Kompakte Wahrheitstabelle 0:31:08 Kompakteste wahrheitstabelle 0:32:22 Schieben Multiplikation oder Division mit 2 0:34:24 LFSR Schieberegister 0:37:20 LTSPICE Simulation 0:42:27 Pseudozufallszahlensequenz 0:44:44 Bus Definition 0:47:36 Serielle Ébertragungsprotokolle 0:51:20 Diskussion serielle Schnittstelle, Datenauge 0:57:03 OSI Schichtenmodell 0:59:58 Schicht 1:UART 1:06:08 Baud rate |

R■ckblick und Heute

R■ckblick:

- Zustandsdiagramme

- Modulo 5 Zðhler

- Spezifikation: Symbol, Zeitverhalten

- Zustandsdiagramm, Zustandstabelle, Minimalform

- VHDL Beschreibung und Test

- Schaltplan, LTSPICE und Test

- Ampelsteuerung, MP3 player

Schieberegister

Anwendung:

|

|

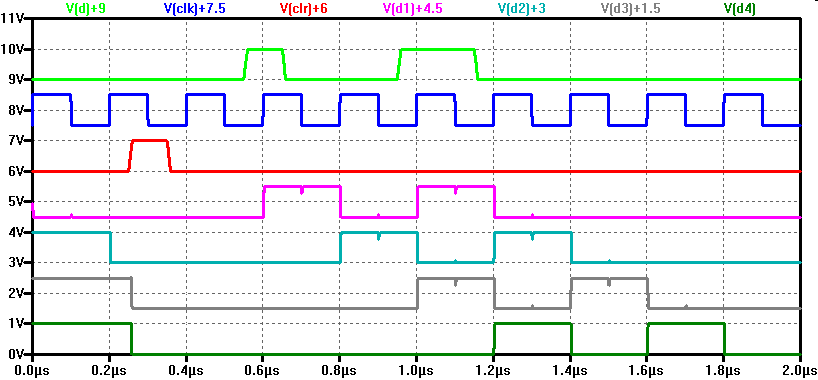

Geben Sie Setup und Hold Zeiten an!

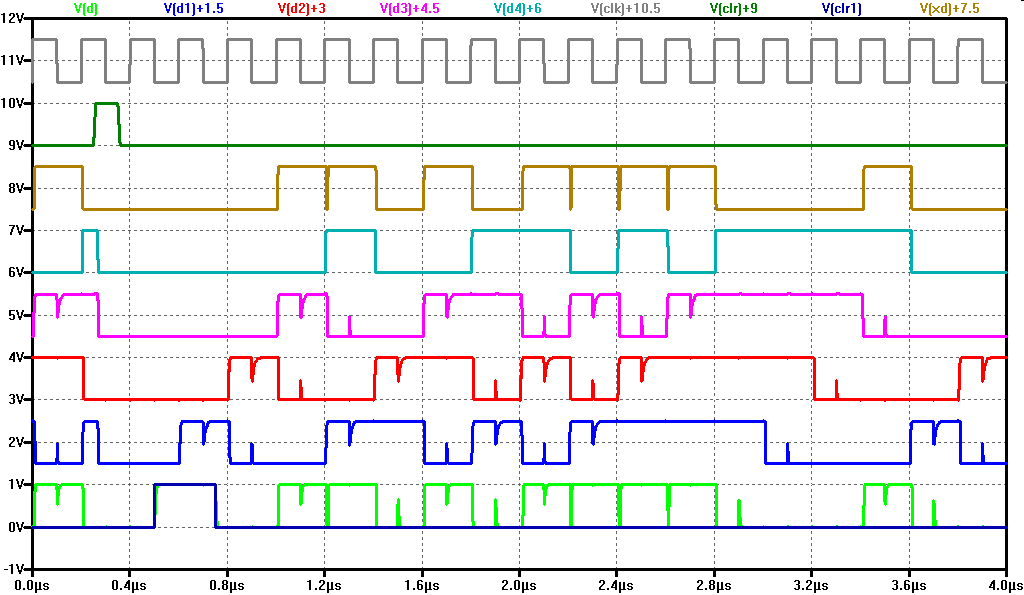

Linear Feedback Shift Register (LFSR)

Anwendung:

|

|

Sequenz (D4, D3, D2, D1): 1, 2, 4, 9, 3, 6, 13, 10, 5, 11, 7, 15, 14, 12, 8, 1 ..

| Anzahl Register | Verkn■pfung | Zahlenbereich |

| 2 | D2 xor D1 | 3 |

| 3 | D3 xor D2 | 7 |

| 4 | D4 xor D3 | 15 |

| 8 | D8 xor D6 xor D5 xor D4 | 255 |

| 16 | D16 xor D15 xor D10 xor D4 | 65535 |

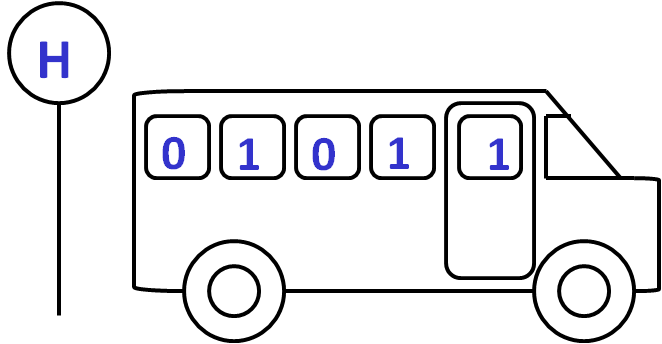

Bus Definition

|

|

Serielle Ébertragungsprotokolle

- Der RS232C- bzw. COM-Standard des PCs dient der Kommunikation mit Peripheriegerðten.

- IýC-Bus: Konfiguration von ICs

- CAN-Bus, Flex-Ray-Bus: Kommunikation von ICs in Kraftfahrzeugen

- SATA-Bus: schnelle Festplatten in PCs

- SPI-Bus: Kommunikation zwischen verschiedenen ICs.

- USB-Bus: Peripheriegerðte am PC

- Ethernet-Bus: Netzwerkkommunikation

- HDMI, DVI, Display Port Bus: Digitale serielle Grafikschnittstellen

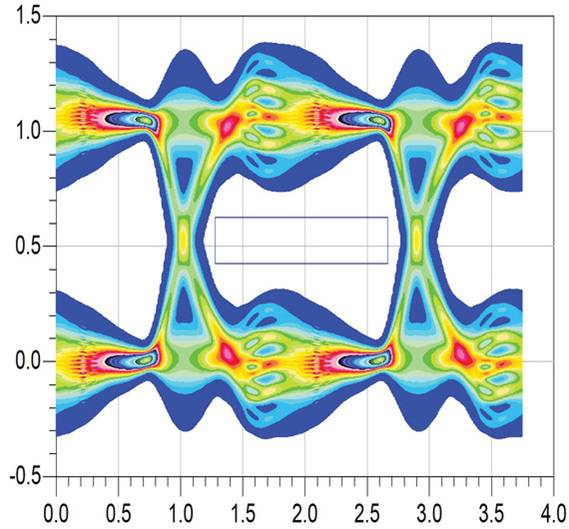

Diskussion serielle Schnittstelle

|

|

OSI Schichtenmodell

Open Systems Interconnection Reference Model| OSI Schicht | Einordnung | Protokollbeispiel | Einheit | Kopplung | |

| 7 | Anwendung (Application) | Anwendungsorientiert | HTTP FTP SMTP |

Daten | Gateway, Content-switch |

| 6 | Darstellung (Prðsentation) | ||||

| 5 | Sitzung (Session) | ||||

| 4 | Transport (Transport) | Transportorientiert | TCP, UDP | Router | |

| 3 | Vermittlung (Network) | IP | |||

| 2 | Sicherung (Data Link) | Ethernet, Token Ring | Rahmen, Frames | Bridge, Switch | |

| 1 | Bit■bertragung (Physical) | Bits | Repeater, Hub | ||

Asynchrone serielle Ébertragung

- Punkt zu Punkt

- M—glichst wenige Leitungen -> Hohe Datenrate, Taktfrequenz

- Parallel Seriell Wandler

- Seriell Parallel Wandler

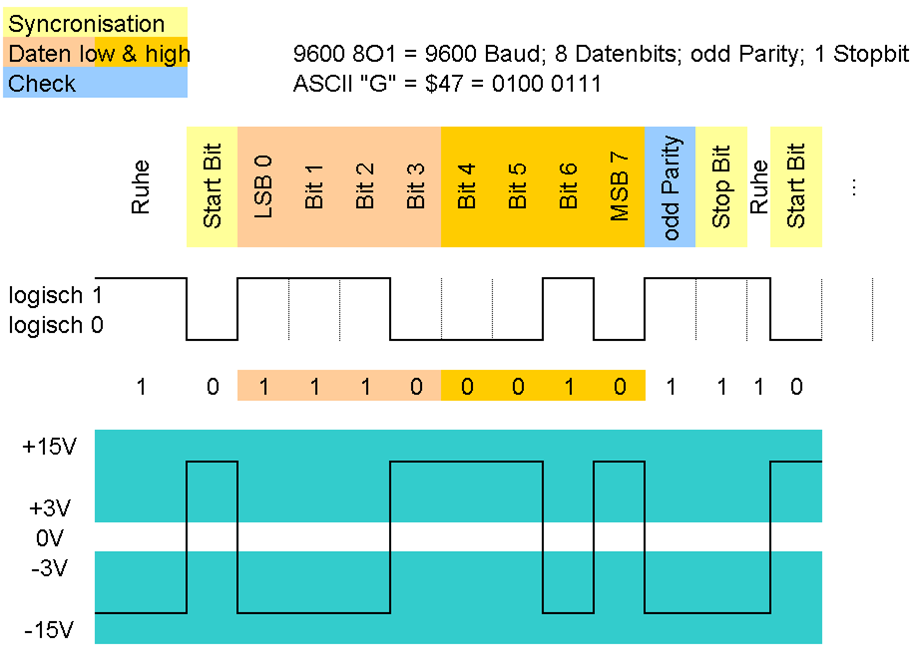

Schicht 1: UART

Universal, asynchronous receiver and transmitterBeispiel Ébertragung des Zeichens "G"

Zustand, logische Information, Bit,Pegel

Baud Raten und Parity

Baud RatenSymbolrate Bitrate (bit/s); Bitdauer |

ParityFehlererkennung Anzahl der '1'er Even Parity (XOR) and odd NOT(XOR) parity |

Eigenschaften

|

|