Elektronik 316 ZustandsmaschineProf. Dr.Jörg Vollrath15 Register |

|

Video der 16. Vorlesung (24.11.2021)

|

Länge: 1:11:00 |

0:0:0 Setup und Hold Zeiten 0:2:45 Erläuterung am Bild 0:4:15 LTSPICE simulation Setup Zeit mit DFF mit CLR 0:6:10 Simulationsergebnis 0:7:50 Ablesen der Zeiten 0:9:45 Genauere Simulation tSetup 0:14:10 Maximale Frequenz (fCLK) 0:20:15 DFF Eingänge und Ausgänge, CE, R, TE, TDI, TDO 0:22:25 Zustandsdiagramm und Zustandstabelle 0:28:15 Bauen Sie einen Modulo 5 Zähler 0:30:55 Schritte zur Lösung 0:35:15 Zählsequenz 0:37:25 Zustandsdiagramm 0:38:25 Zustandstabelle 0:40:15 Beschriftung der Zustandstabelle 0:40:55 Warum die letzten 3 Zeilen? 0:42:30 Ausgangsmuster bestimmen 0:45:30 Werkzeuge zur Schaltungsrealisierung? 0:48:10 Zeile die eine '1' ergibt 0:51:4 B1(n+1) 0:53:44 LTSPICE Schaltung 0:58:27 Simulationsergebnis 1:0:37 Diskussion des Ergebnisses 1:2:24 Zustandstabelle und Vereinfachung |

Video der 16. Vorlesung (8.12.2023)

|

Länge: 1:11:00 |

0:0:0 Video Digitaltechnik 0:0:50 D Flip Flop, positiv flankengesteuert 0:1:43 Eingänge, Zustände, Ausgänge 0:2:0 Test 0:4:32 Scan Test, Scan Flip Flop, Register 0:5:32 Logik, Verzögerung, setup und hold Zeit 0:7:13 fmax = 1/ Tmax = 1/(tPDDFF+tPDLogik + tsetup) 0:8:58 Leistungsverbrauch und Begrenzung der Integration 0:12:57 Diskussion Arbeitsspeicher und Spannungspegel 0:15:50 Zustandstabellen 0:17:38 Modulo 5 Zähler 0:19:0 Projektplanung Aufgabenstellung klären 0:20:15 Sequenz 0,1,2,3,4,0,1,2,3,4 0:21:13 Blockdiagramm Zustandsmaschine 0:21:50 Sum of Product SOP 0:24:30 Zustandsnamen 0:25:30 Reset Diskussion 0:27:30 Möglichkeiten, Zeilen der Zustandstabelle 0:28:30 Zustand n+1 0:35:35 Zustandsgraph 0:37:47 Eintragen jeder Zeile als Pfeil 0:39:21 Zustandsdiagramm 0:40:13 MSB LSB, Reihenfolge und Gewichtung der Stellen 0:42:13 Vorteile eines Zustandsdiagramms 0:44:21 Sum of products '1'er am Ausgang werde mit UND Funktion dargestellt 0:46:13 Z2n+1 0:47:40 Z0n+1 0:49:19 Schaltplan Eingänge und Inverter 0:50:40 NAND Schaltung für SoP 0:53:8 Z1n+1 0:54:46 Z0n+1 0:55:48 Diskussion Optimierung 0:57:17 Versuch Digitaltechnik 0:59:20 Aufbau im Video 1:0:2 Test der Schaltung 1:0:56 Programmierbarer Logikbaustein 1:2:59 Diskussion Test und Verifikation, Messung 1:5:56 Zustandstabelle und Minimierung Karnaugh Veitch 1:8:46 Schaltplan 1:9:53 Zeitsimulation mit LTSPICE und überprüfen des Ergebnisses |

Rückblick und Heute

Rückblick:

- Schaltnetz und Schaltwerk

- Ein CMOS Schalter

- Schaltbild DFF, Scanflipflop

- Setup und Hold Zeit

- Zustandsdiagramm

Heute:

- Zustandsdiagramme

- Modulo 5 Zähler

- Spezifikation: Symbol, Zeitverhalten

- Zustandsdiagramm, Zustandstabelle, Minimalform

- VHDL Beschreibung und Test

- Schaltplan, LTSPICE und Test

- Ampelsteuerung, MP3 player

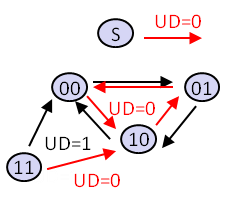

Zustandsdiagramm, Zustandsgraph

|

|

Ein Zustandsdiagramm benötigt immer eine Legende, damit man weiss was dargestellt wird.

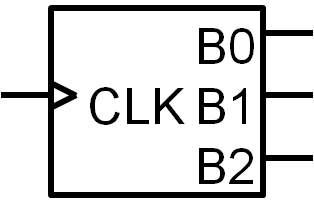

Modulo 5 Zähler: Aufgabenstellung

Bauen Sie einen Modulo 5 Zähler.|

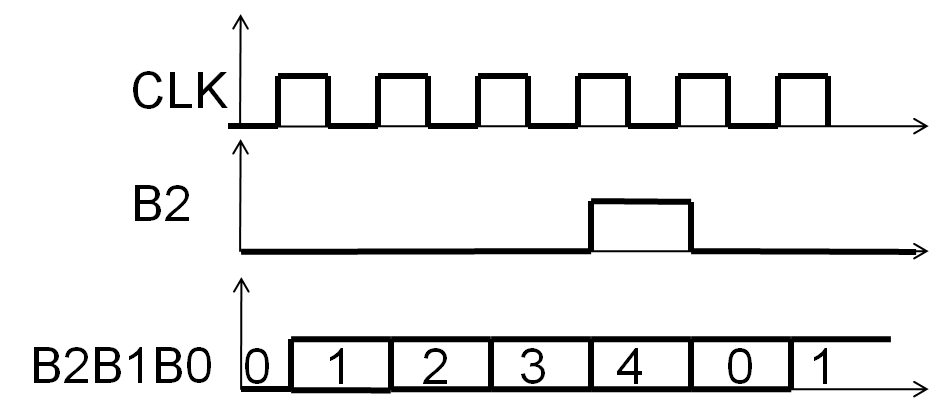

Modulo 5 Zähler: 0,1,2,3,4,0,1,2,3,4,0.. CLK Mit jeder steigenden Flanke wird Eins hochgezählt Taktteiler: Drei FF werden benötigt. |

|

Dies ist eine offen Aufgabenstellung. Die Spezifikation ist unvollständig.

Impliziert wird eine Taktsteuerung.

Steuert das Taktsignal das Zählen oder ein enable Eingang (CE)?

Impliziert wird eine Taktsteuerung.

Steuert das Taktsignal das Zählen oder ein enable Eingang (CE)?

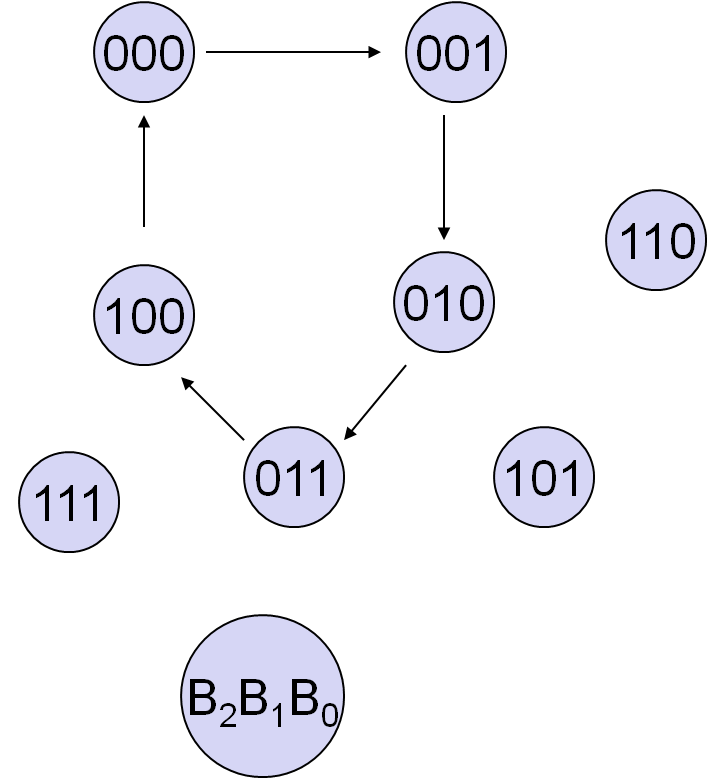

Modulo 5 Zähler: Zustandsdiagramm

|

3 Speicherzellen 8 Zustände 5 Zustände werden benutzt. Kein Signal an den Pfeilen, da die Zustandsänderung auf jeden Fall durchgeführt wird. |

|

Modulo 5 Zähler: Zustandstabelle

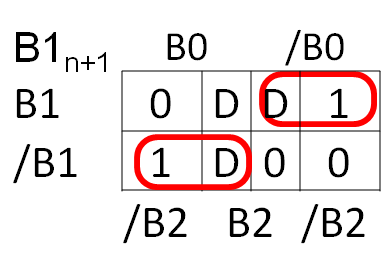

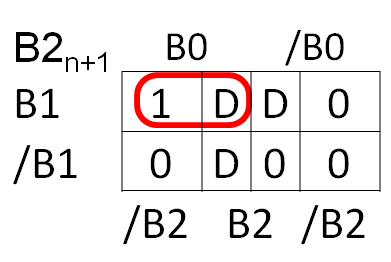

Eine Zustandstabelle wird erzeugt und mit Karnaugh Veitch minimiert.

|

B0n+1=/B0n·/B2n  B1n+1=(B0n·/B1n) + (/B0n·B1n)  B2n+1= B0n·B1n |

Modulo 5 Zähler: Schaltungsrealisierung

LTSPICE code

Man sieht eine typische Medwedew-Zustandsmaschine.

Die Ausgänge werden für die Erzeugung des nächsten Zustands invertiert und nichtinvertiert

links bereitgestellt.

Die disjunktive Normalform wird durch NAND Gatter in der Mitte dargestellt.

Je nach logischer Verknüpfung werden mehrere NAND Gatter zusammengeschaltet und mit den entsprechenden Signalen verbunden.

Die disjunktive Normalform wird durch NAND Gatter in der Mitte dargestellt.

Je nach logischer Verknüpfung werden mehrere NAND Gatter zusammengeschaltet und mit den entsprechenden Signalen verbunden.

Modulo 5 Zähler: Schaltungssimulation

LTSPICE code

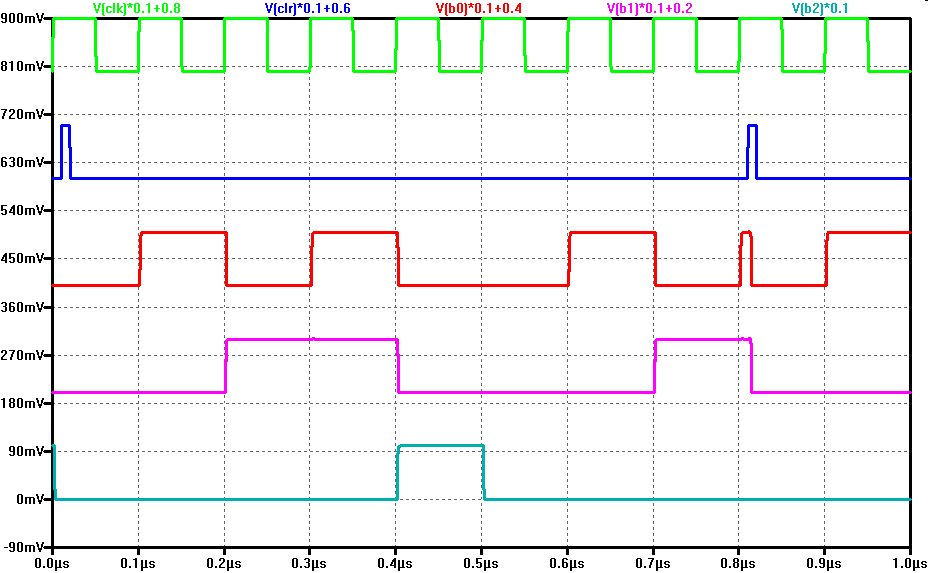

In der Simulation sieht man das CLK-Signal, clr, und die Zählerausgänge b0, b1, b2.

Am Anfang kann man sehen wie b2 durch das clr-Signal "1" auf "0" gesetzt wird.

Dann sieht man das Hochzählen von b2,b1,b0 bei steigender CLK-Flanke.

000, 001, 010, 011, 100, 000,...

Das clr-Signal bei 0.8us setzt b0 und b1 auf "0" zurück.

Am Anfang kann man sehen wie b2 durch das clr-Signal "1" auf "0" gesetzt wird.

Dann sieht man das Hochzählen von b2,b1,b0 bei steigender CLK-Flanke.

000, 001, 010, 011, 100, 000,...

Das clr-Signal bei 0.8us setzt b0 und b1 auf "0" zurück.

Hochschule für angewandte Wissenschaften Kempten, Jörg Vollrath, Bahnhofstraße 61 · 87435 Kempten

Tel. 0831/25 23-0 · Fax 0831/25 23-104 · E-Mail: joerg.vollrath(at)fh-kempten.de

Tel. 0831/25 23-0 · Fax 0831/25 23-104 · E-Mail: joerg.vollrath(at)fh-kempten.de

Impressum