Interface Electronics

Laboratory Exploring Data Converters

Fall 2015

Prof. Dr. Jörg Vollrath

Overview

This laboratory investigates a real data converter. It is intended to study performance using standard laboratory equipment.Link to: Laboratory instructions

- Measurement set up: Electronic Explorer

- DAC Architecture: C2C, R2R

- Ramp measurement

- Sine measurement

- ADC architecture: SAR

- ADC control with a NEXYS3 FPGA board

- Ramp measurement

- Sine measurement

- Setup and Hold characterization

- Summary

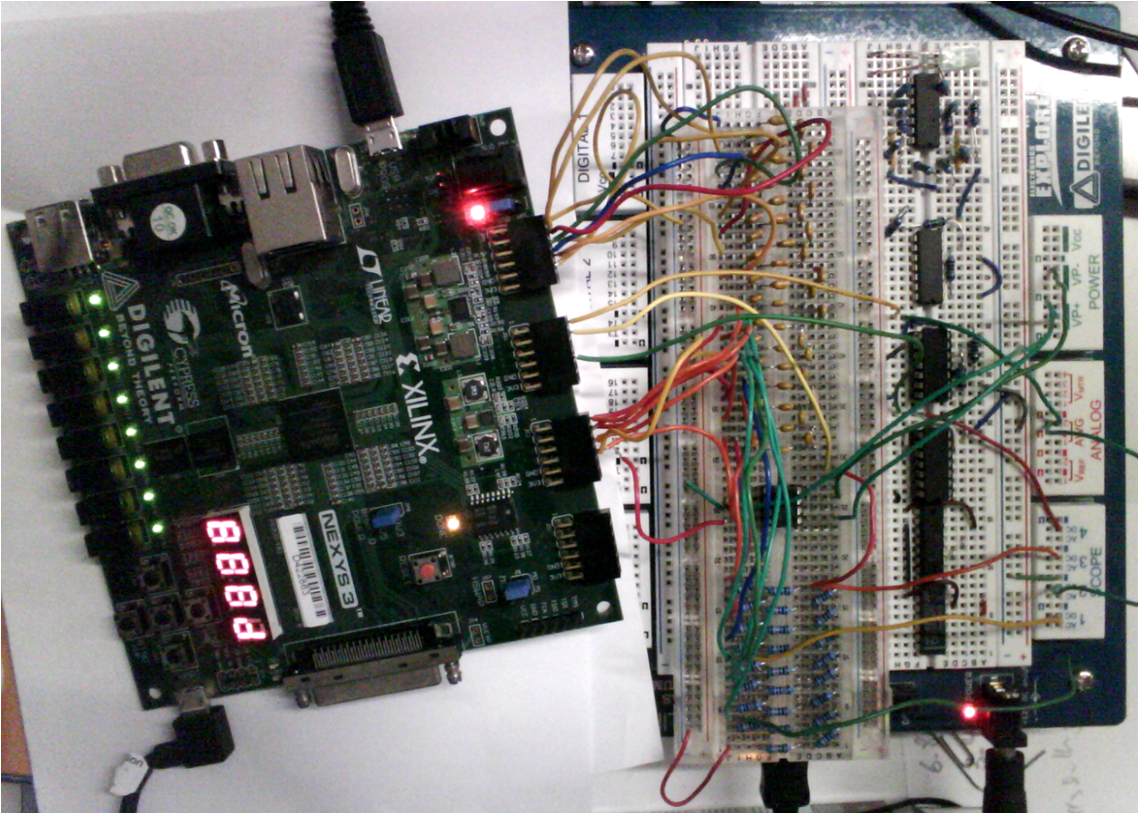

Laboratory Equipment

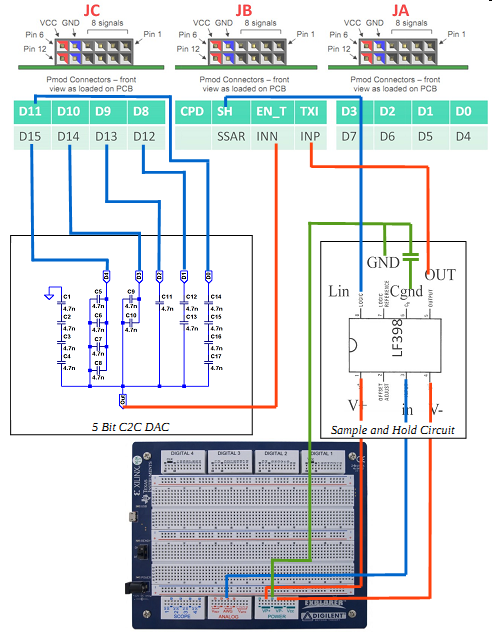

Electronic ExplorerDigital patterns are generated and the result can be measured with an oscilloscope.Oscilloscope: 8k samples, 10 Bit, 40MSps Input Impedance: \( 9M\Omega \), 10pF Logik analyzer and pattern generator: 32 channel, 100 MSps Arbitrary pattern depth: 512 vectors Arbitrary waveform generator: 14 Bit, 40MSps NEXYS 3 FPGA board3 PMOD connectors with 8 channels, 200 MHz eachUSB seriell interface to transfer data 8 switches |

Data converter1% precision resistors of 100k for 8 Bit R2R DAC.74nF for upper 8 Bit of C2C DAC. LF398N sample and hold (10us). |

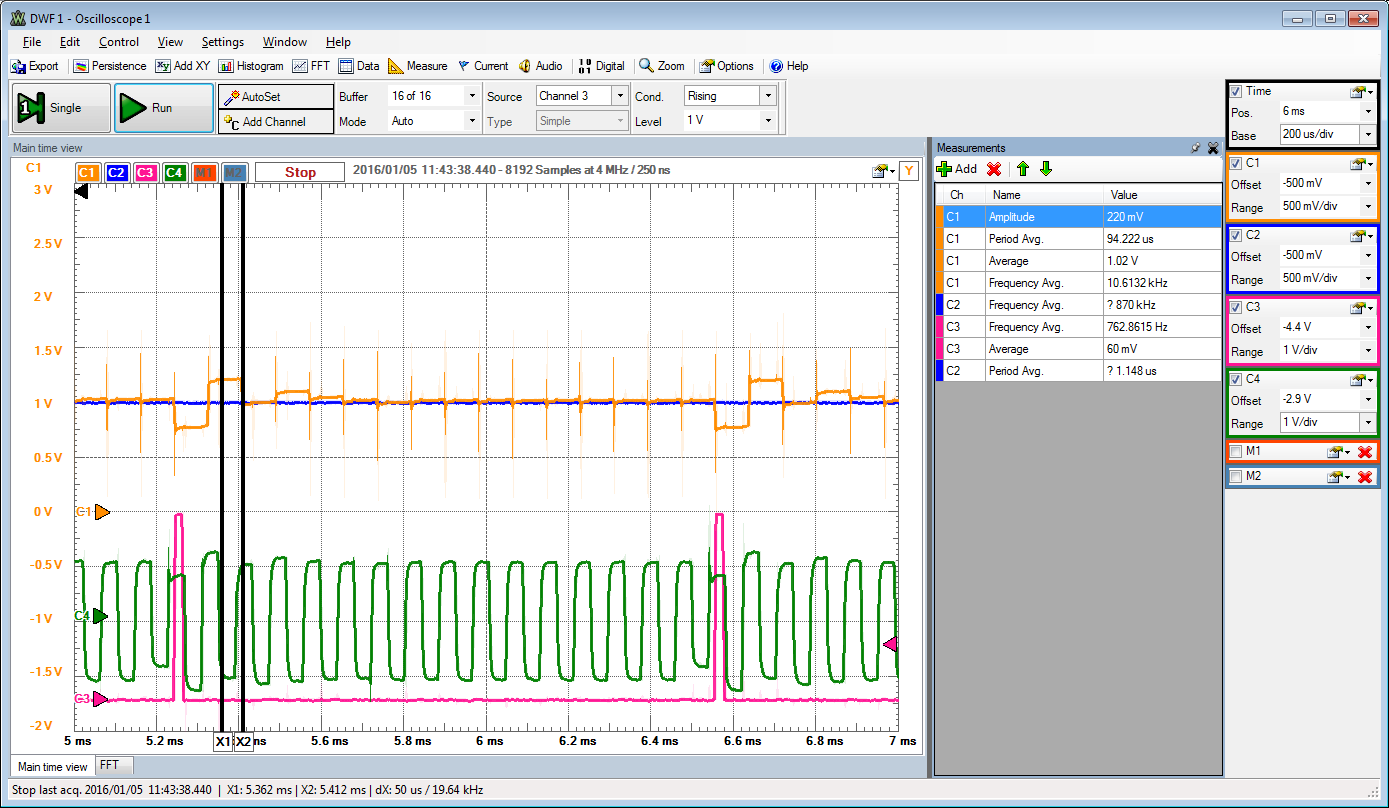

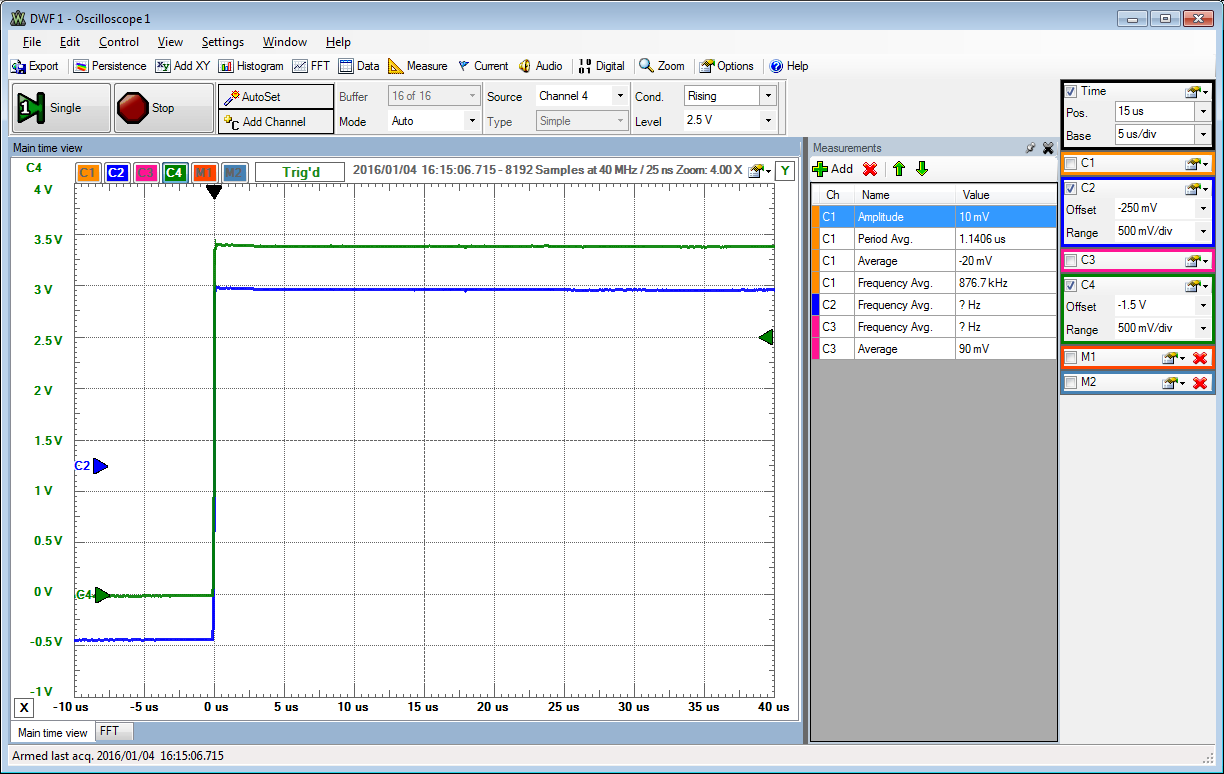

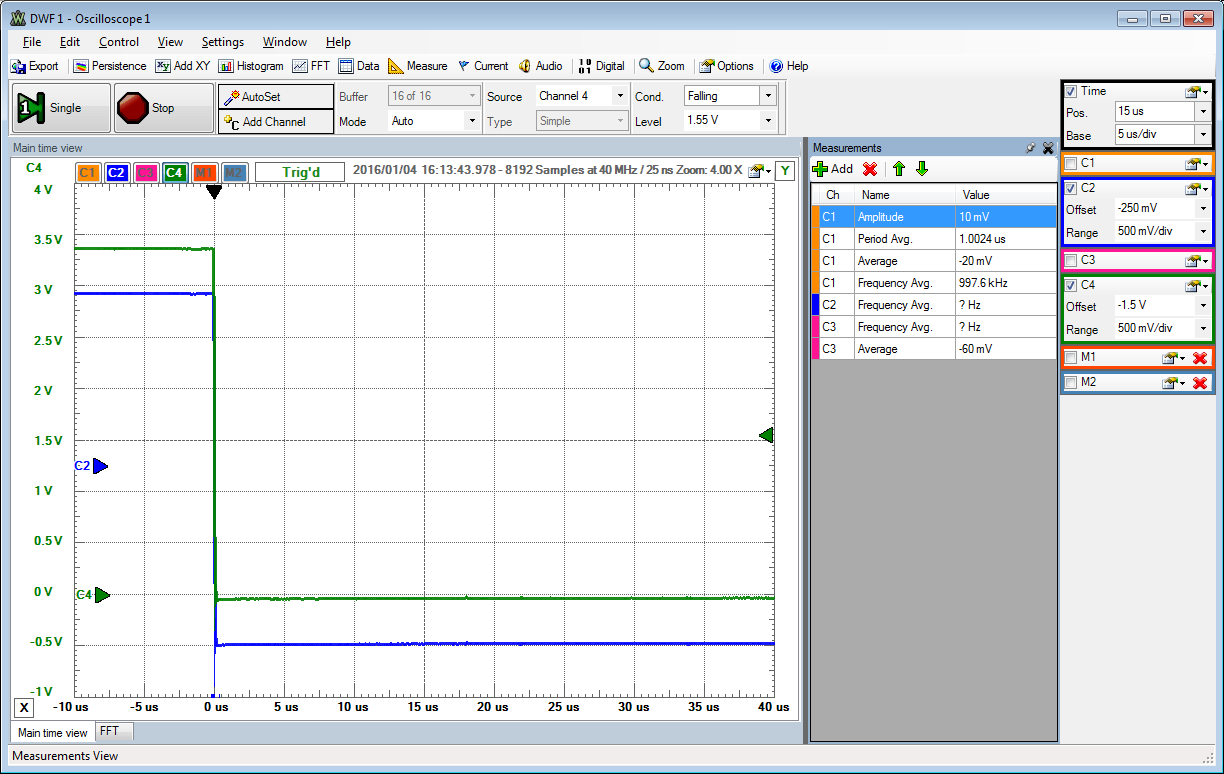

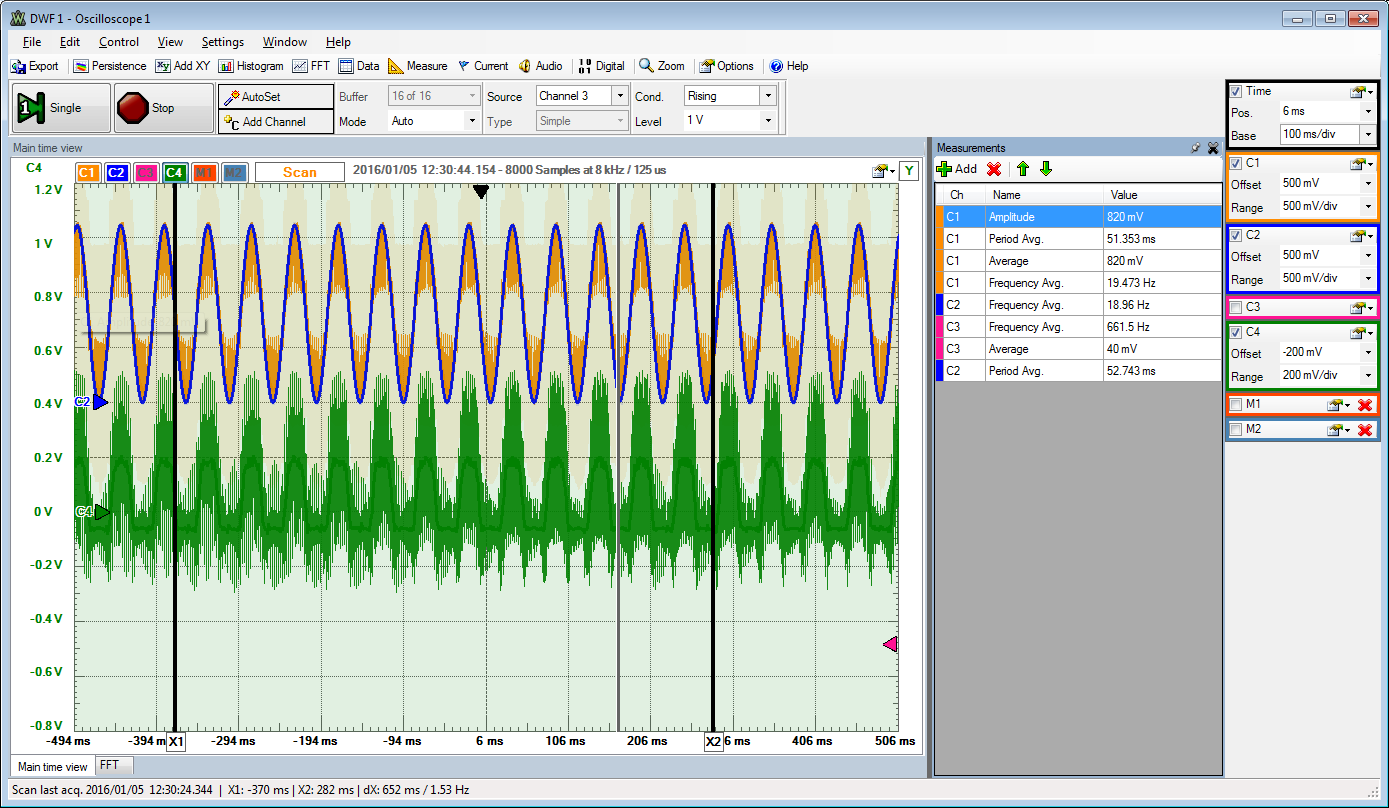

SAR operation snapshot

C1: DAC output after SH.

C2: AWG1 input signal

C3: SH start of conversion, sample and hold signal.

C4: DAC output signal

DAC output works only good with oscilloscope(R = 1 MOhm, C = F) at output.

It can be seen how 16 steps are done during succesive approximation.

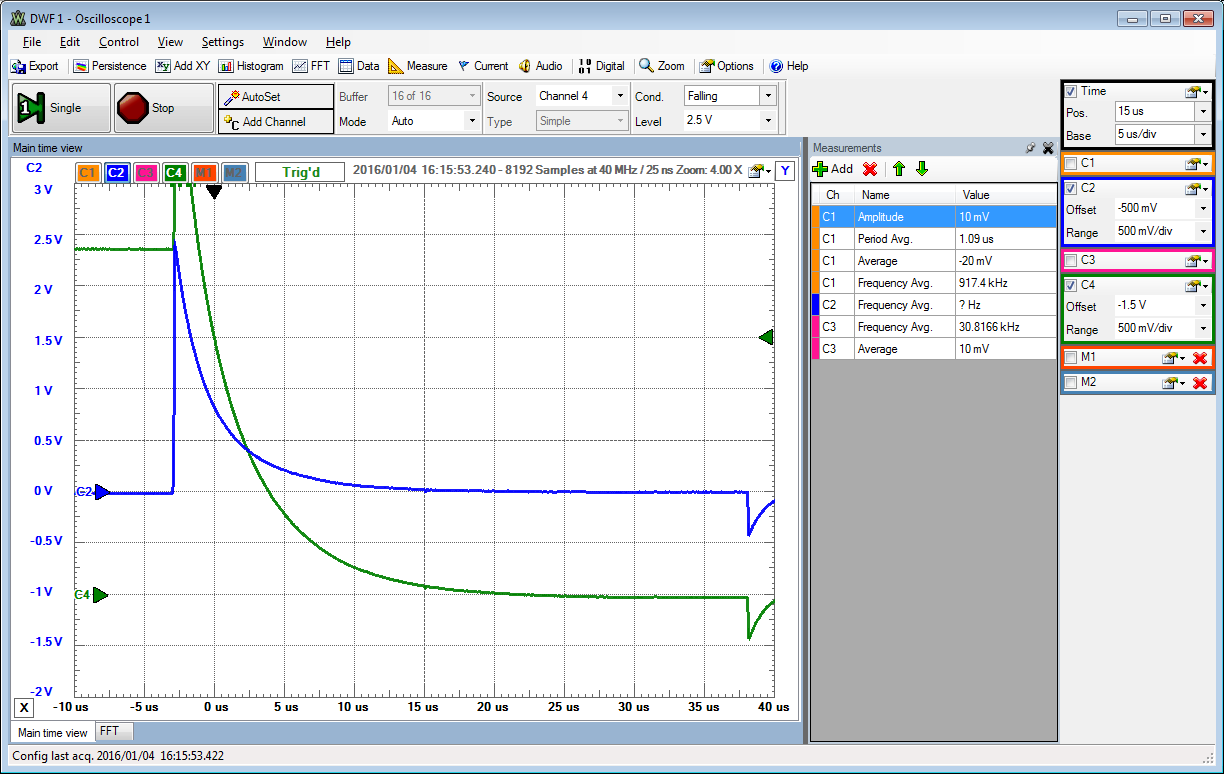

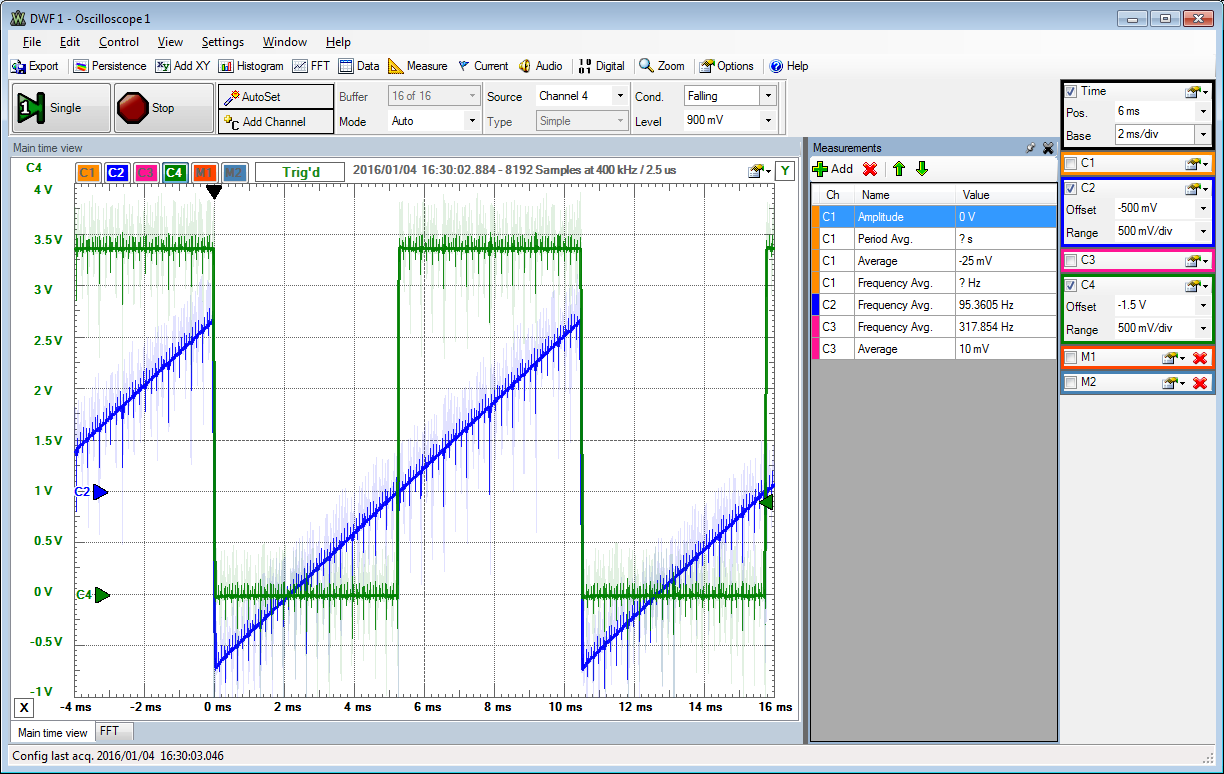

Settling time and ramp measurement

Output waveform and digital input signals can be measured. Digital input signals should be rectangular and reach full level. Weak digital drivers can limit settling time.Since the oscilloscope has a 10 Bit ADC, an 8 Bit C2C DAC was used (sw6..5 = 11).

Only the C2C DAC was connected to the outputs of the FPGA.

Settling time was measured for full level rising and falling and midlevel rising and falling for a sawtooth signal (sw4..3 = 10,01).

The worst case settling time can be observed at mid level switching.

Assuming an exponential capacitance charging curve a settling time of 40 us can be determined.

\( v(t) = V_{FS} \left( 1 - e^{-\frac{t}{\tau}} \right)\)

If it takes \( t_1 = 4 \mu s \) to reach \( 0.5 V_{FS} \), it takes \( 2 \cdot t_1 \) to reach \( 0.75 V_{FS} \). 8 Bits need \( 8 t_1 = 8 *4 \mu s = 32 \mu s \) to reach a precision less than 0.5 LSB. The closest option is 40 us (sw2..0 = 011).

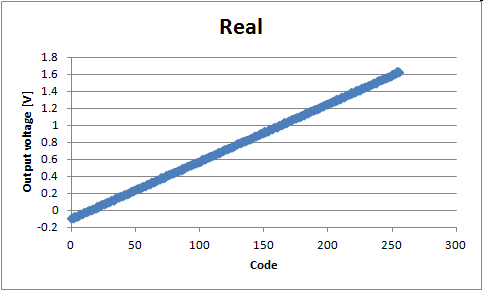

Ramp measurement

The oscilloscope records 8192 values at a time. Since the period of the sawtooth is 10.48ms this gives 4195 values. 16 values per level. Only the average of the last 3 values for each level are used for the DAC transfer curve.

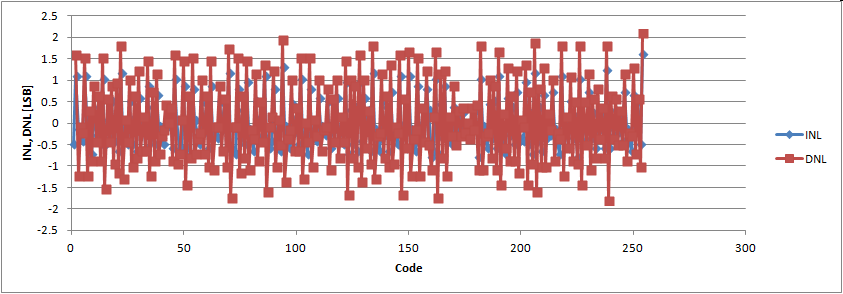

DAC transfer curve INL and DNL

Measured data are embedded into this document via JavaScript array and are then processed for the graphs.

INL is below 4 so uncalibrated 2 Bits are lost giving a resolution of 6 Bits.

Eliminating DNL <= -1 using a lookup table probably achieves a resolution of 7 Bits.

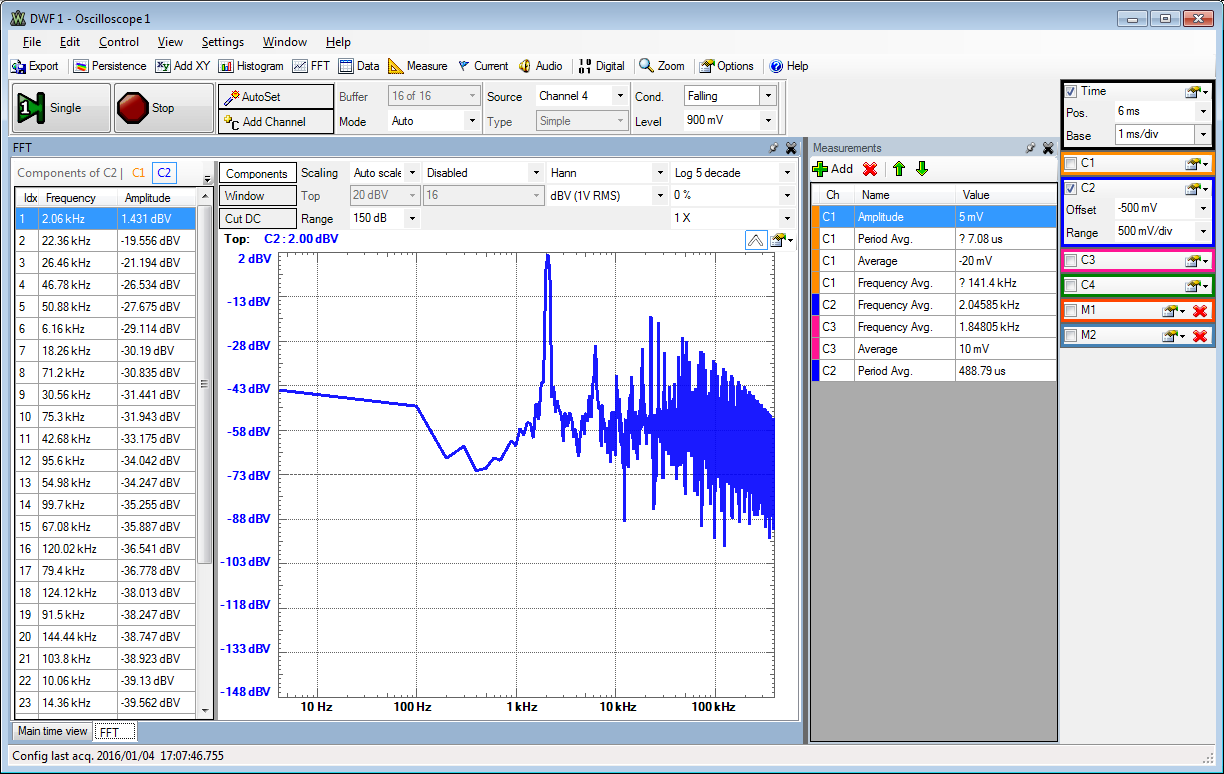

Spectral test of DAC

Using sw4..3 = 11 generates a sine wave for the DAC. This works only with 16 Bit mode, leaving driving bits 0..7 at 0V.

The signal strength is 1.42 dbV at 2.06kHz and the next highest peak is at -19.5 dbV at 22.36kHz.

How is a DAC spectral test done and signal to noise ratio calculated?

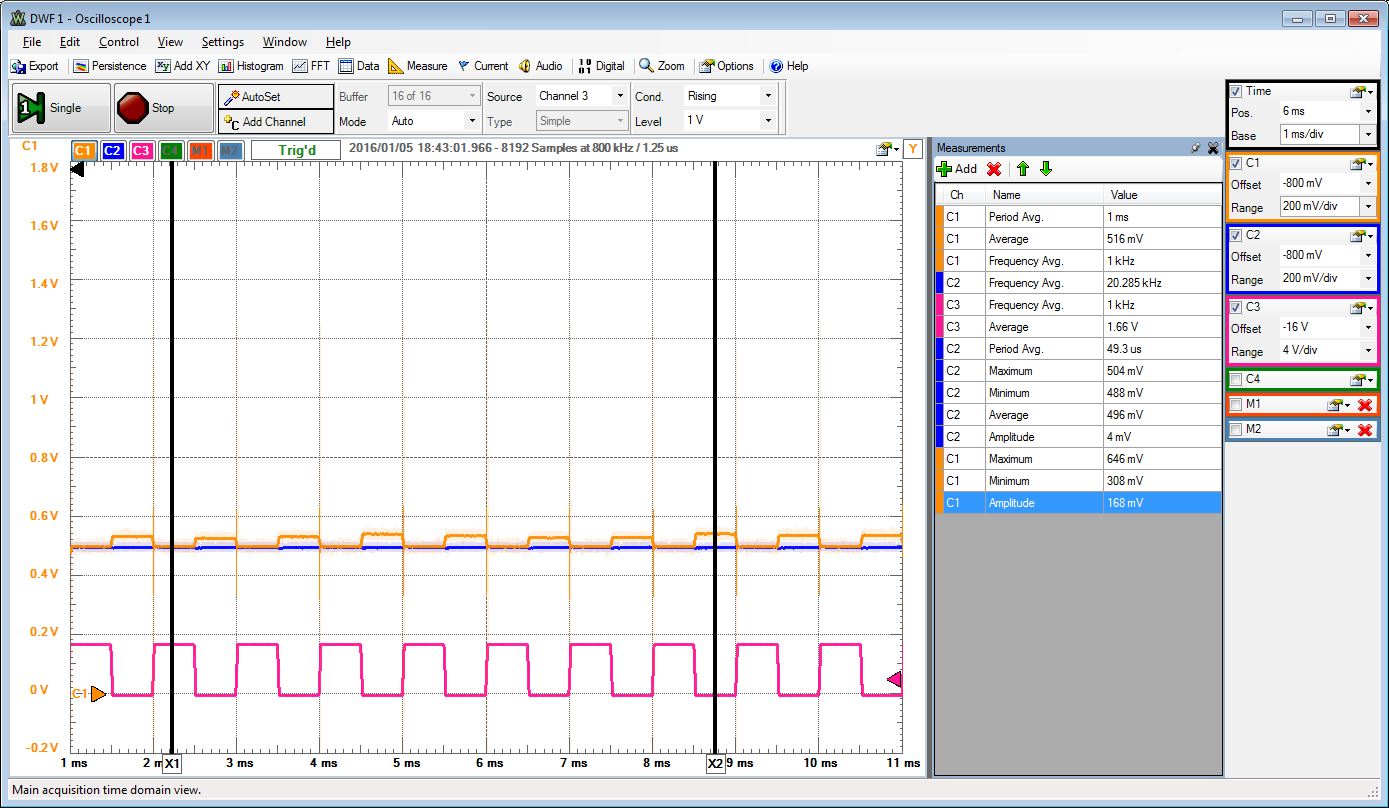

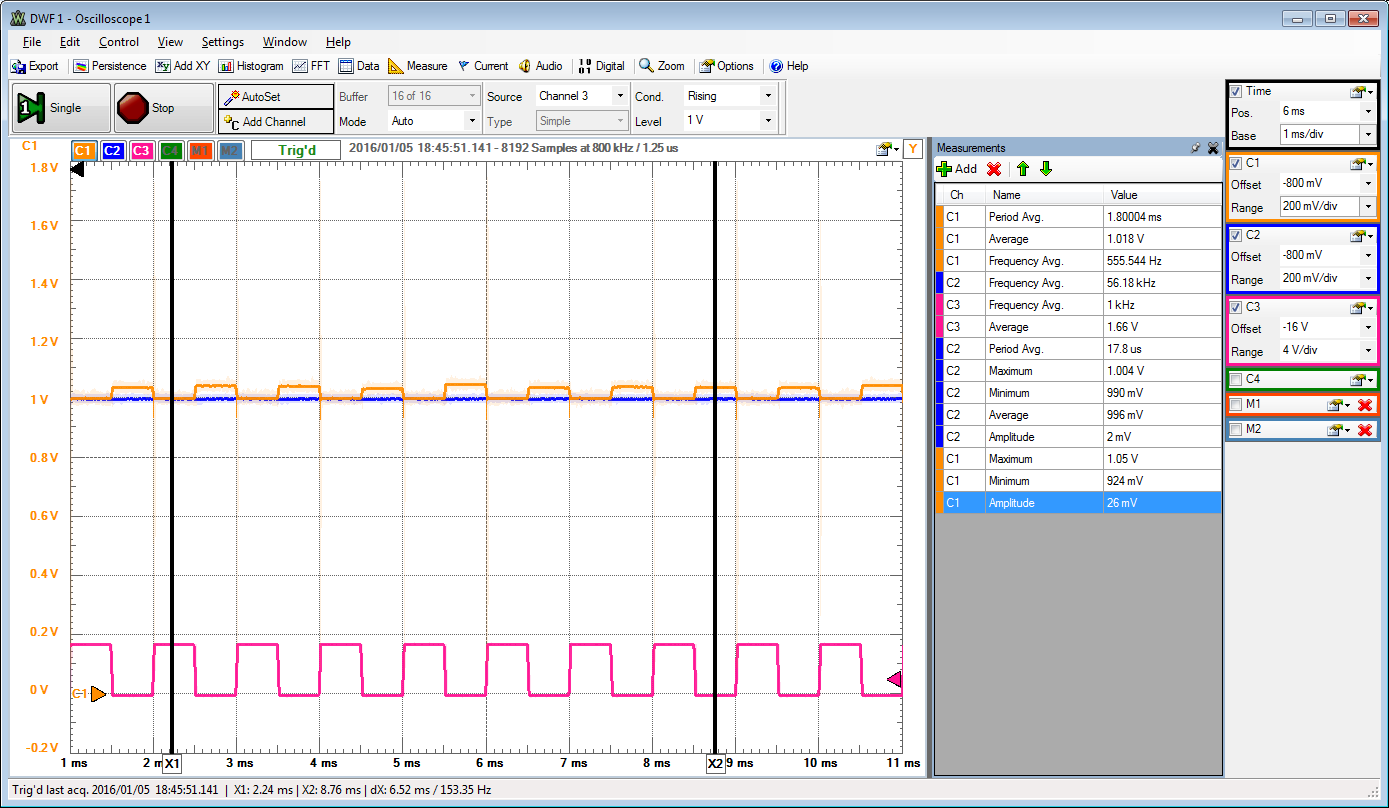

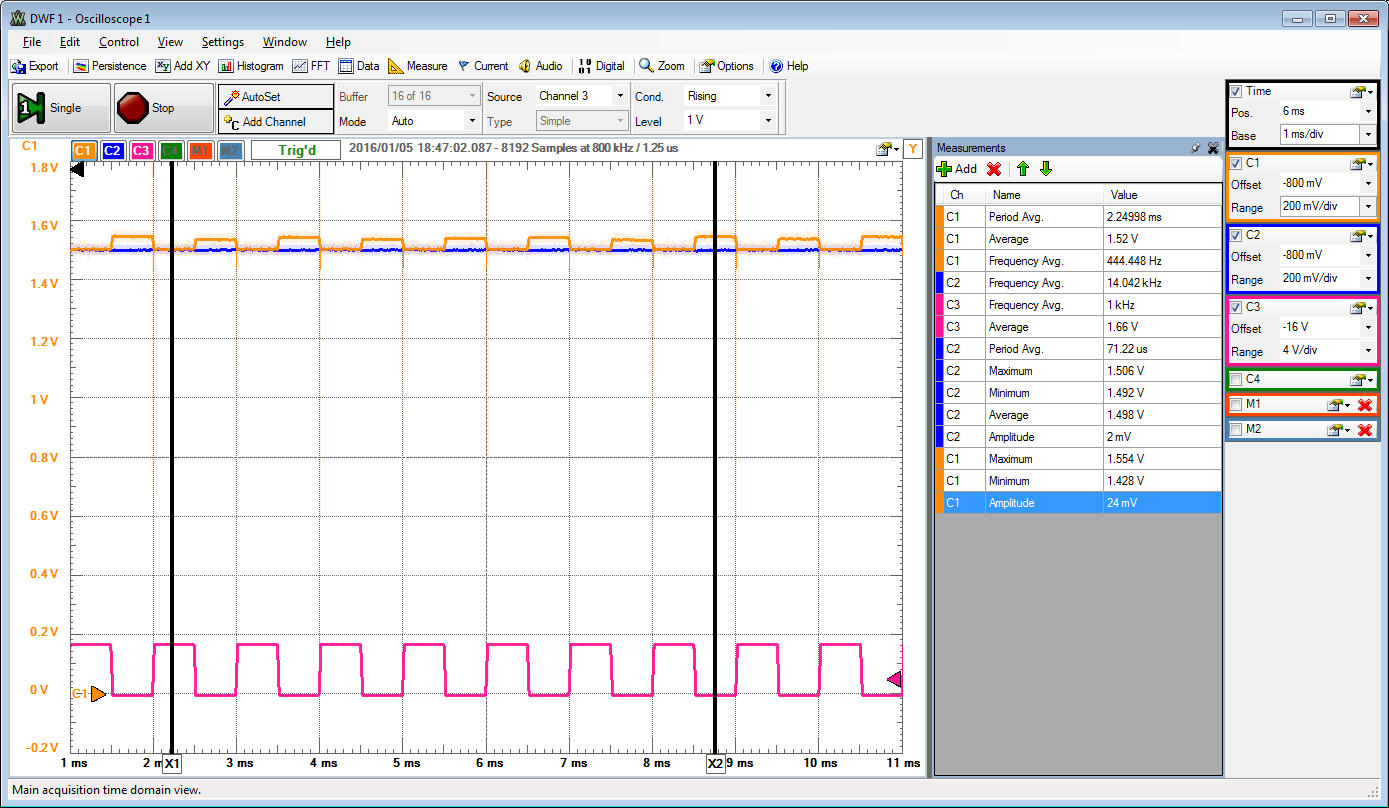

Sample and hold operation

There is a sample and hold circuit needed to keep the input voltage during conversion constant, controled via signal SH.The C2C DAC eliminates DC component. therefore positive and negative voltages will occur.

sw7 is used to invert the DAC output for half the cycle reducing the number of effective bits by one and eliminating a DC component. To feed this signal to the input receiver of the FPGA it is necessary to use a second sample and hold circuit which transfers only positive voltages to the FPGA. The second sample and hold is controled by signal SH1.

First clock/control feedthrough is measured.

C1: Signal after SH.

C2: AWG1 constant input signal

C3: SH control signal.

0.5 V, 1.0 V, 1.5 V input signal 26 mV amplitude output.

The sample and hold adds 50 mV to the signal.

Is this result depending on the load capacitance?

SAR transfer curve

Setup: 1.3ms per 16 Bit sample. Range: -90mV..1.63V8 Bit sampling 10 values per Bit gives accuracy of 0.1 LSB.

Time: 2560 * 1.3ms = 3.32s

Frequency ramp: 0.15Hz

UART transmits 2 hex values per sample.

Effective resolution should be 7 Bit.

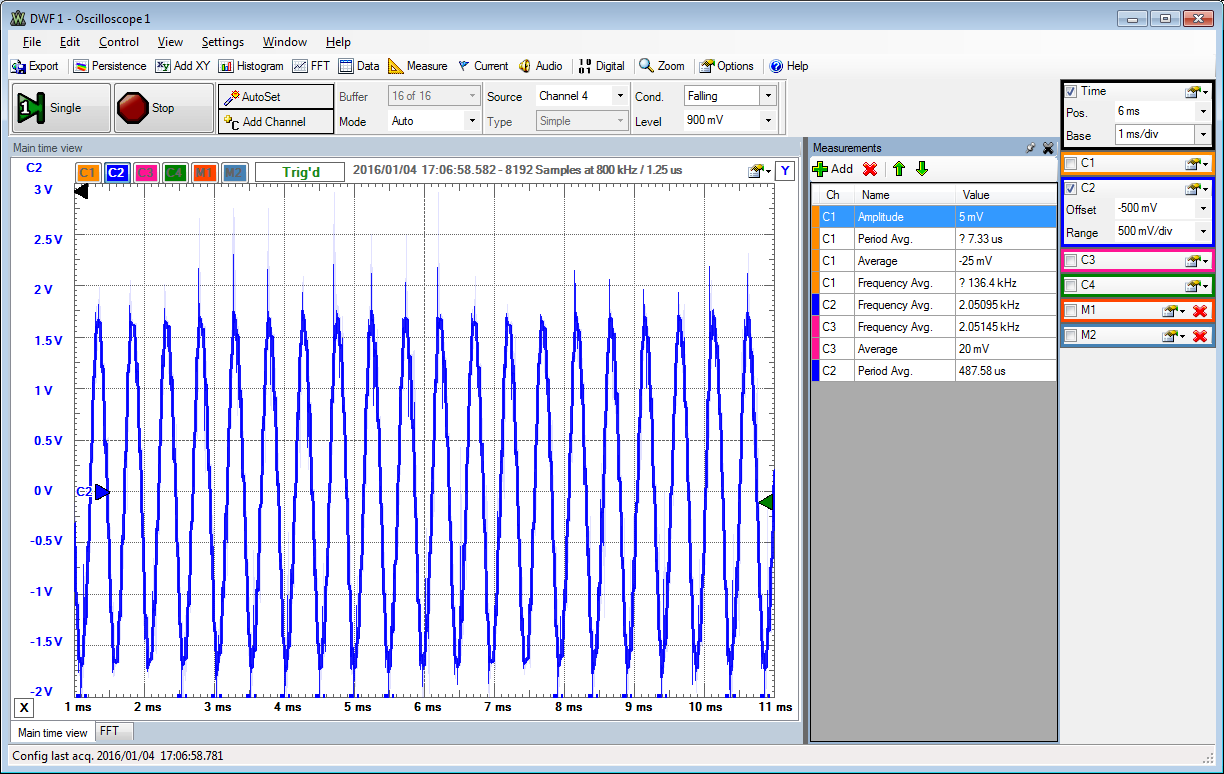

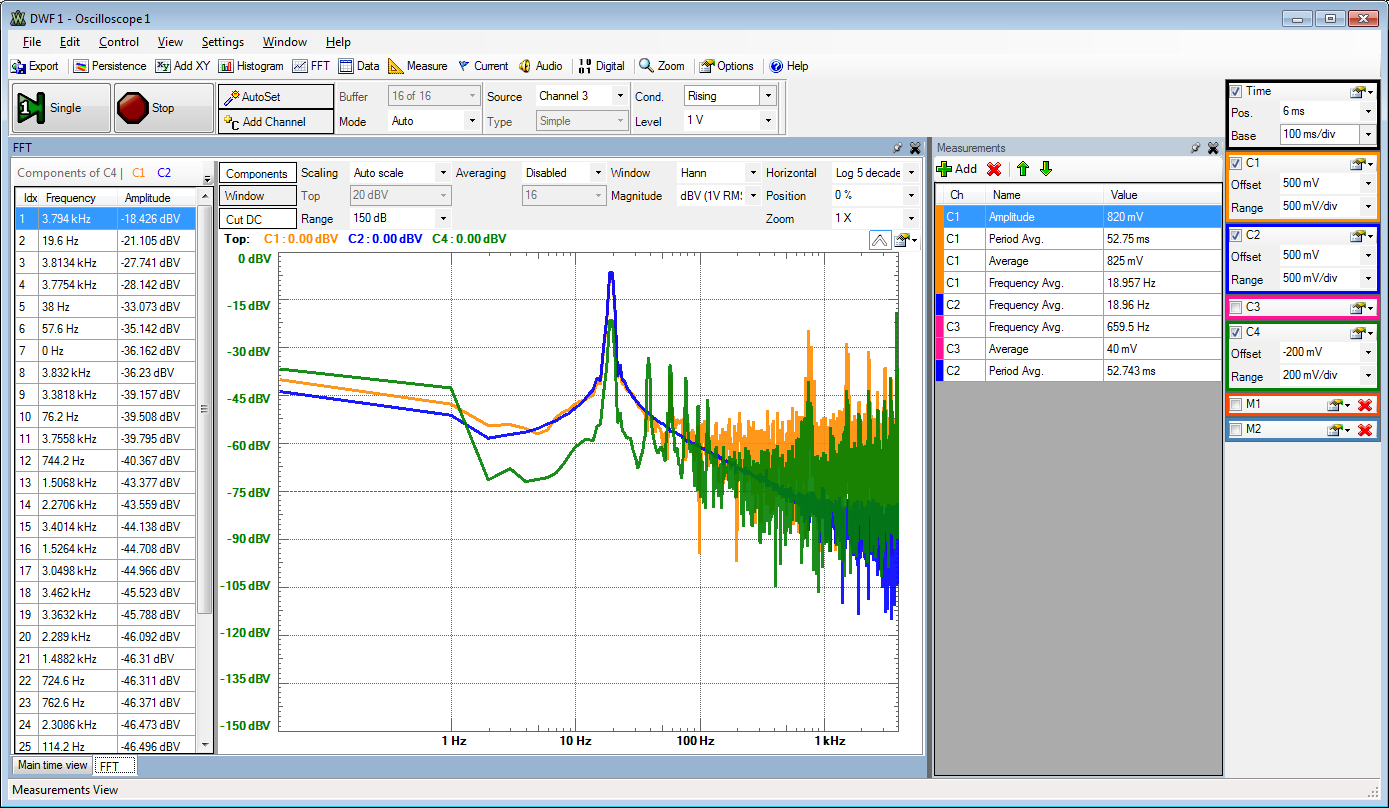

Spectral test

1.3ms per sample. 8 bit 256 values take 16 * 256 = 4096 samples. 5.3248 seconds. 101 periods gives 18.96 Hz for input sine signal.38400 Baud rate, 8 characters (1 Byte + 2 start stop) per value gives 38400/8/10 = 480 samples per second. The output code was transmitted twice giving a data rate of 240 samples per seconds.

Since 4096 samples were taken for FFT of digital output data (0..255) it took 16s. Therefore the base frequency code of 1 is equivalent to 0.0625Hz. The signal of 18.96Hz is then around 400.

Sine time signal:

x-axis: log SNR = 1.73 dB + 6.07 B dB + 10 log10( N / 2 )

B: Number of Bits

N: Number of samples = 16 * 2 B

N = 2048 -> 30 dB

There is bleeding because a non integer number of periods. Realistic noise level is -20dB + 36 dB = 16 dB. SNR = 30 dB - 16 dB = 24 dB gives ENOB = (24 dB - 1.73 dB) / 6.07 dB = 4 Bit.

Signal: 20 * log (256) = 48 dB

Summary

An 8 Bit C2C SAR was built and has a ENOB of 4 Bits and Ts = 16 * 80 us = 1.28 ms sample time and 781 Hz sampling frequency.The input range is from -90mV to 1.63V with a intended step size of 6.7mV. No special circuit design or calibration was done. An effective number of bits for ramp measurement is 6 Bit and for spectral test is 4 Bit.

Measured data are embedded into this Webpage as JavaScript array for inspection and further investigations.

Link to: Detailed laboratory instructions

Future work

- LTSPICE model SAR:

- Measure Capacitances

- Measure internal resistance of FPGA pin driver

- Simulate and evaluate ramp and sine signal

- Higher Resolution: B

Select and sort capacitances and or implement error correction for better resolution (12 Bit). - Higher Speed: fs

- Select lower capacitances to achieve higher speeds (MHz range).

- Implement buffer in FPGA

- Select different sample and hold circuit for higher speed.

Hochschule für angewandte Wissenschaften Kempten, Jörg Vollrath, Bahnhofstraße 61 · 87435 Kempten

Tel. 0831/25 23-0 · Fax 0831/25 23-104 · E-Mail: joerg.vollrath(at)fh-kempten.de

Impressum