Interface ElectronicsLaboratory 03: ADC DAC AnalysisGroupA1,****06, A |

Overview

- ADC & DAC Setup

- Simulation and analysis of a ramp signal: DNL, INL and LSB

- Simulation and analysis of a sine signal: DNL, INL, SNR

- Summary

Schematic for ADC & DAC

|

code4Bit_ADC_DAC_pipe_simple |

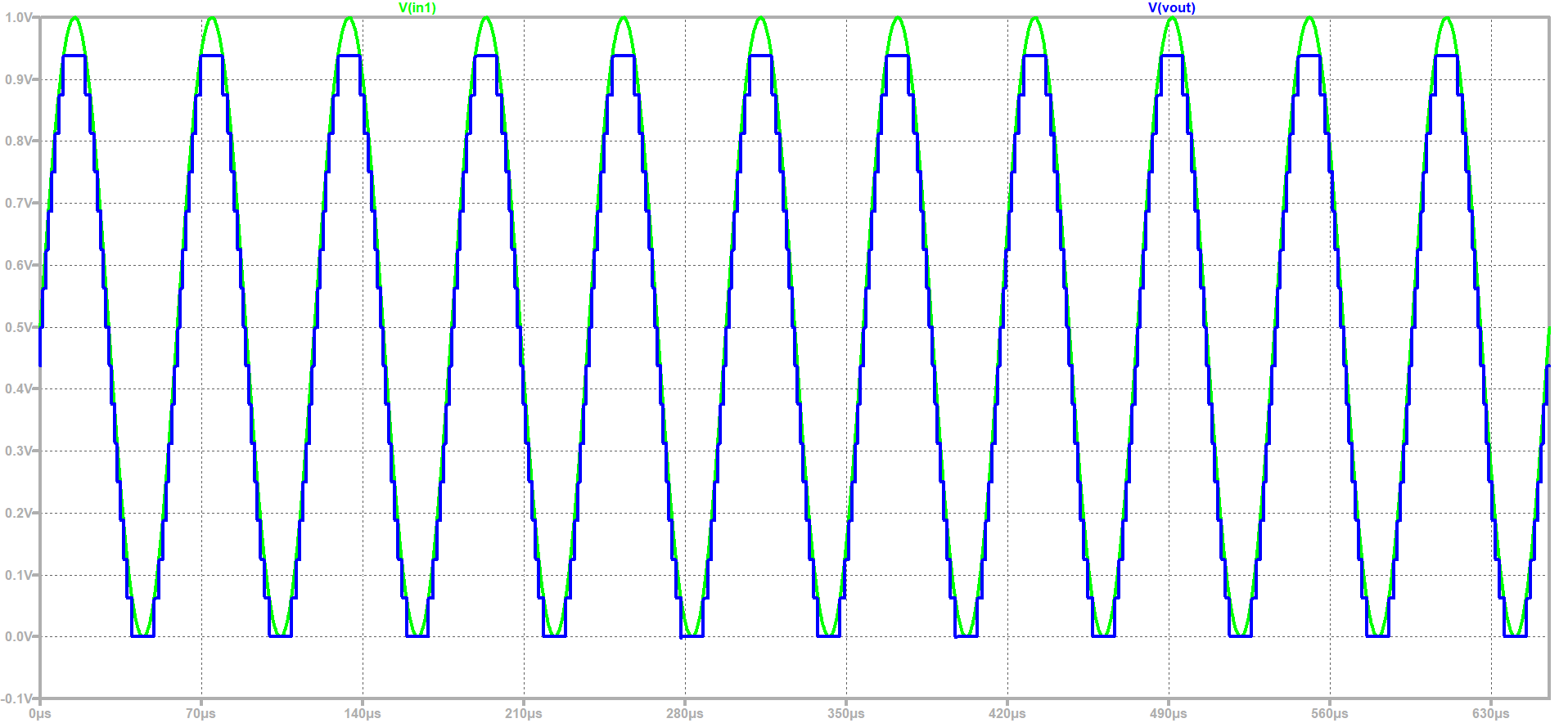

4 Bit ADC and DAC simulation for Sine Wave

- A 4 bit ADC DAC with ideal components is simulated with sine wave as input signal. |

|

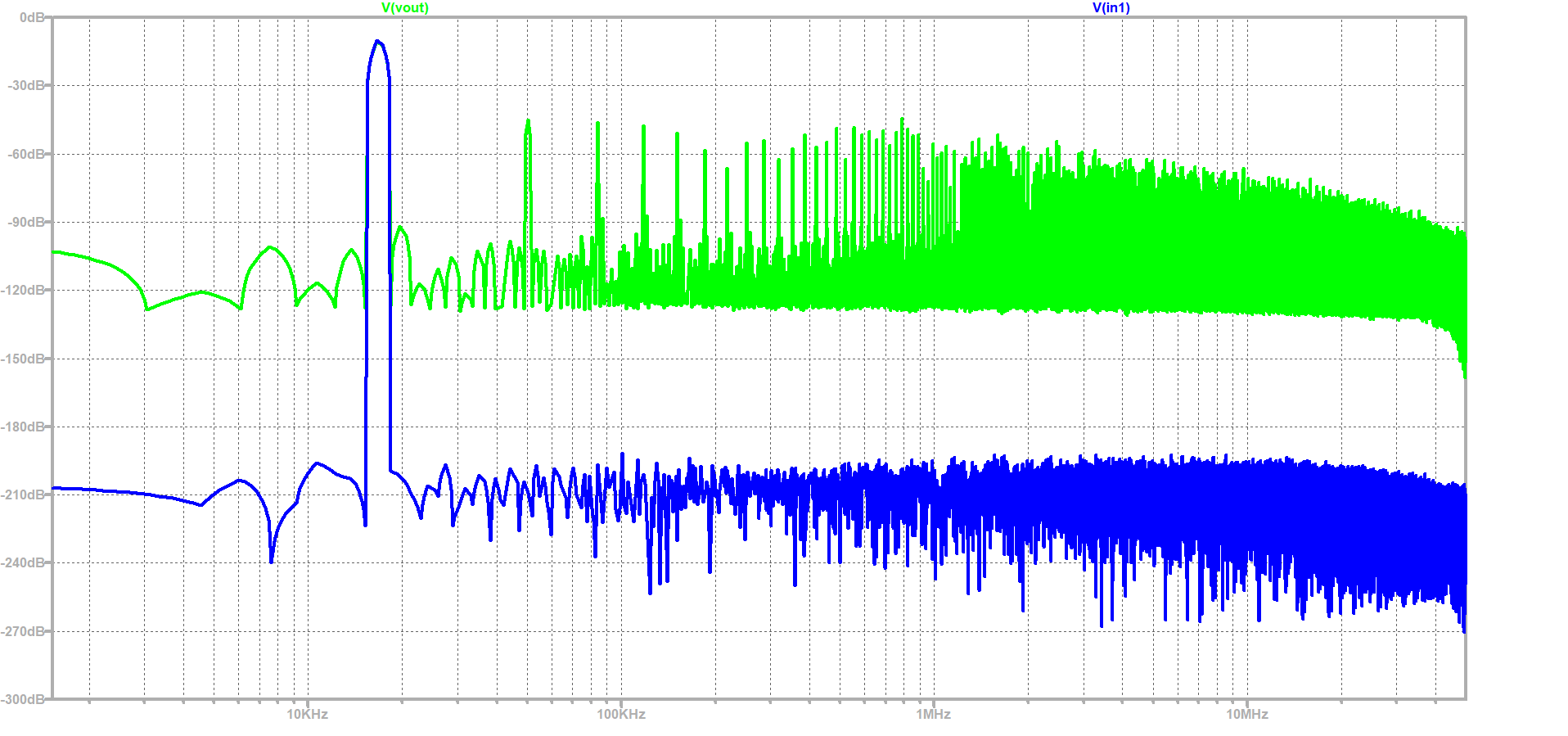

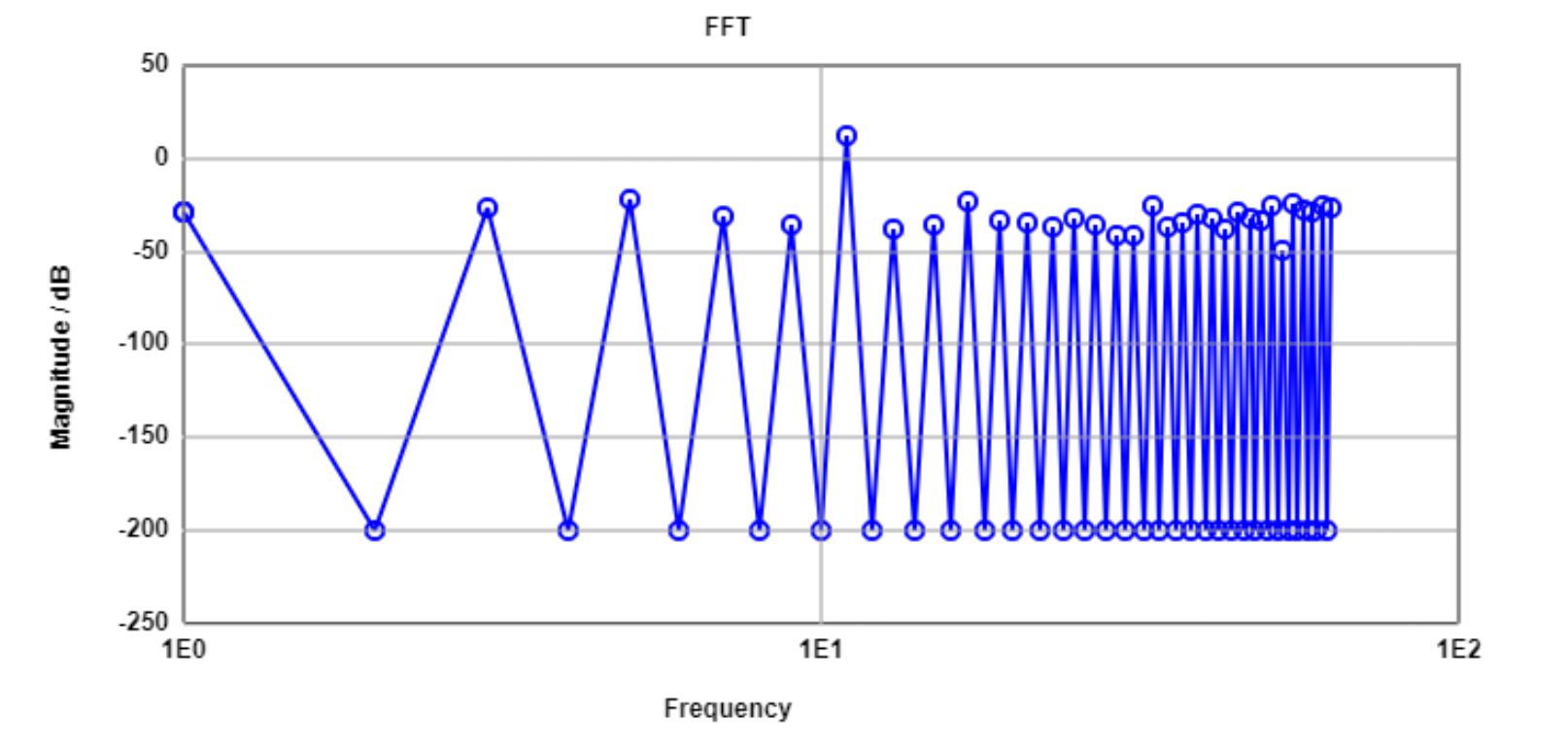

FFT of 4 Bit ADC and DAC with Sine input

- A FFT of 4 Bit ADC abd DAC is done by LTSPICE. |

|

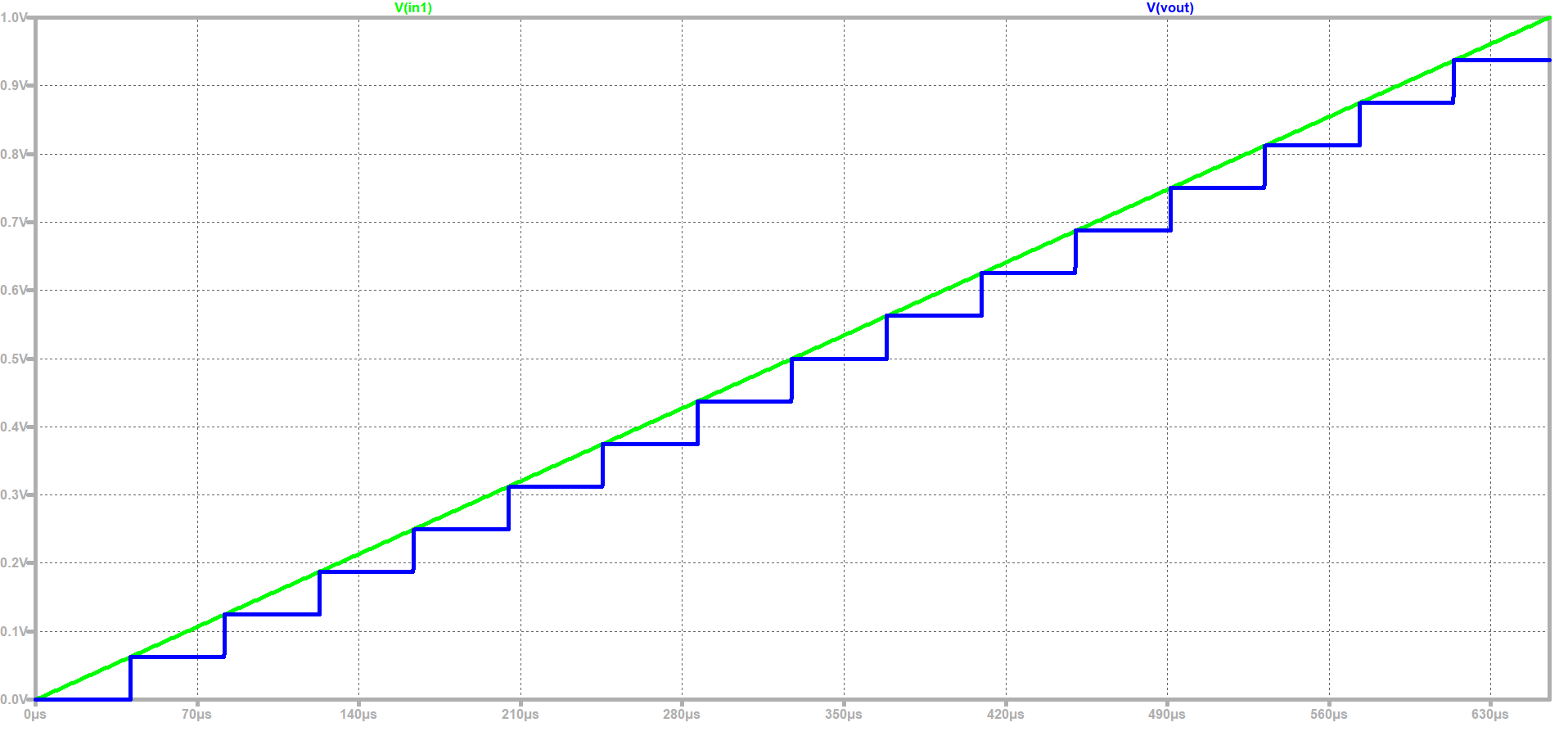

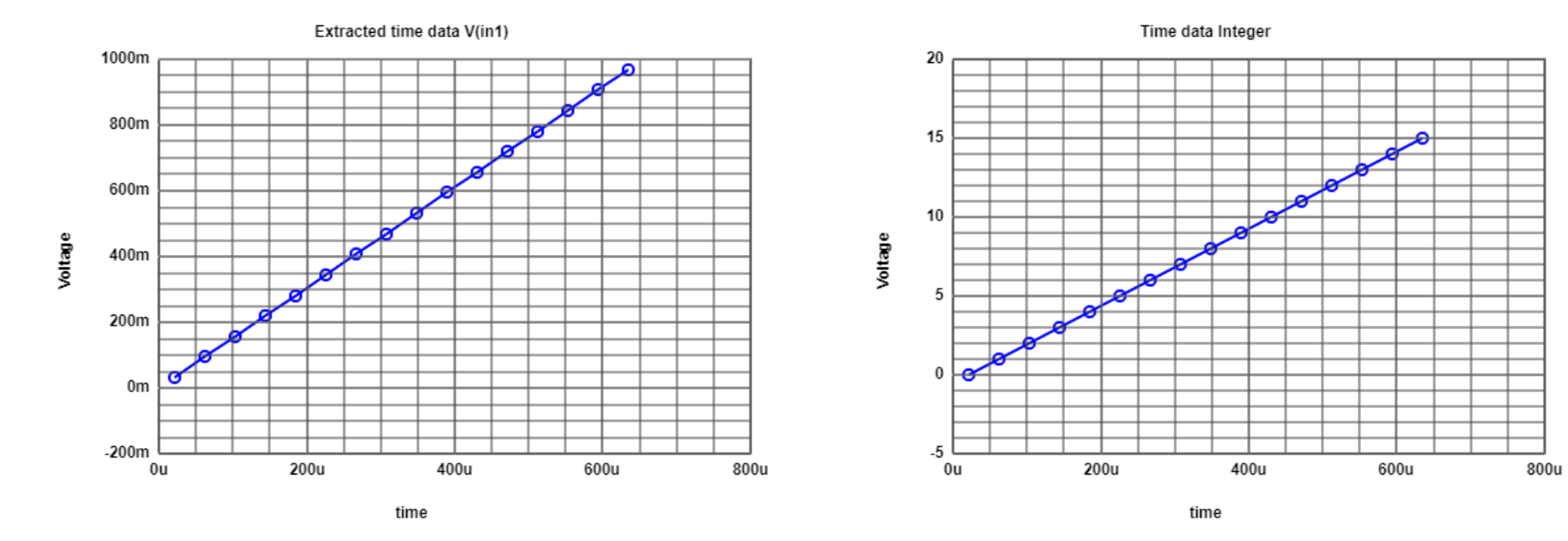

Ramp Test of DAC ADC

- Ramp test is performed for FFT to check signal to noise.

- Another voltage source is required for ramp and that is added by the following command.

- V1 in1 0 PULSE(0 1 0 655.36u 655.36u 0 1310.72u)

- Since LTSPICE simulation has varied step size so so to extract data poitns we need external data processors.

|

|

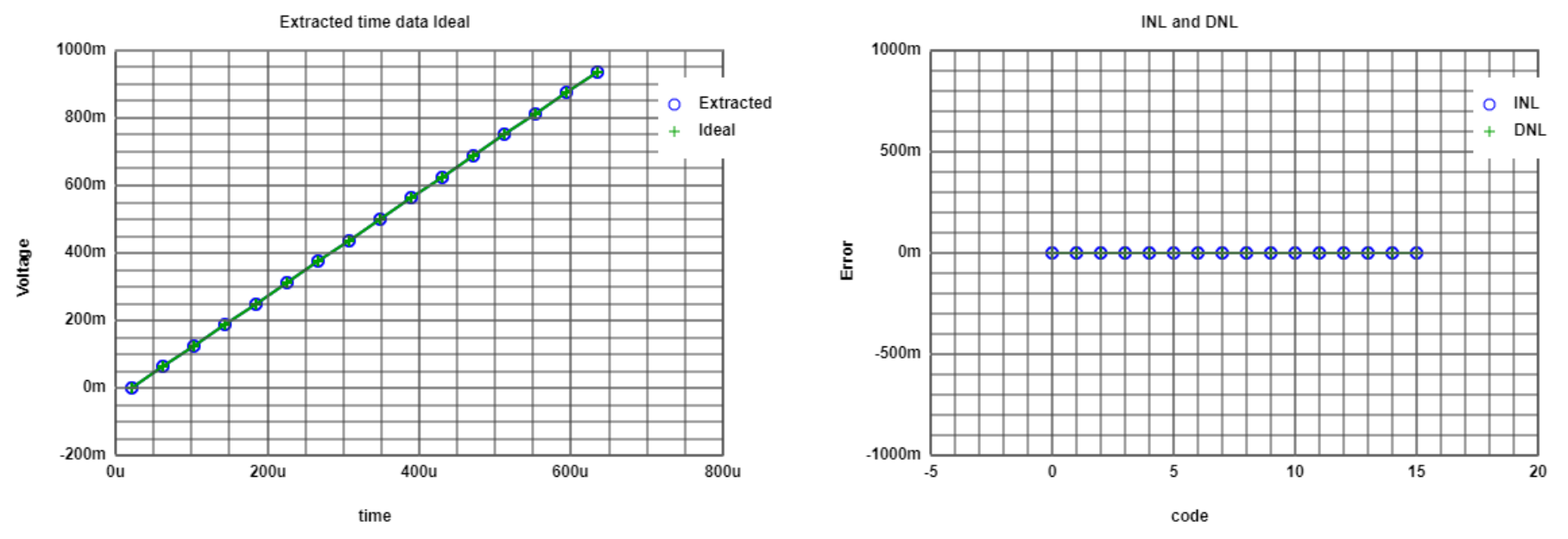

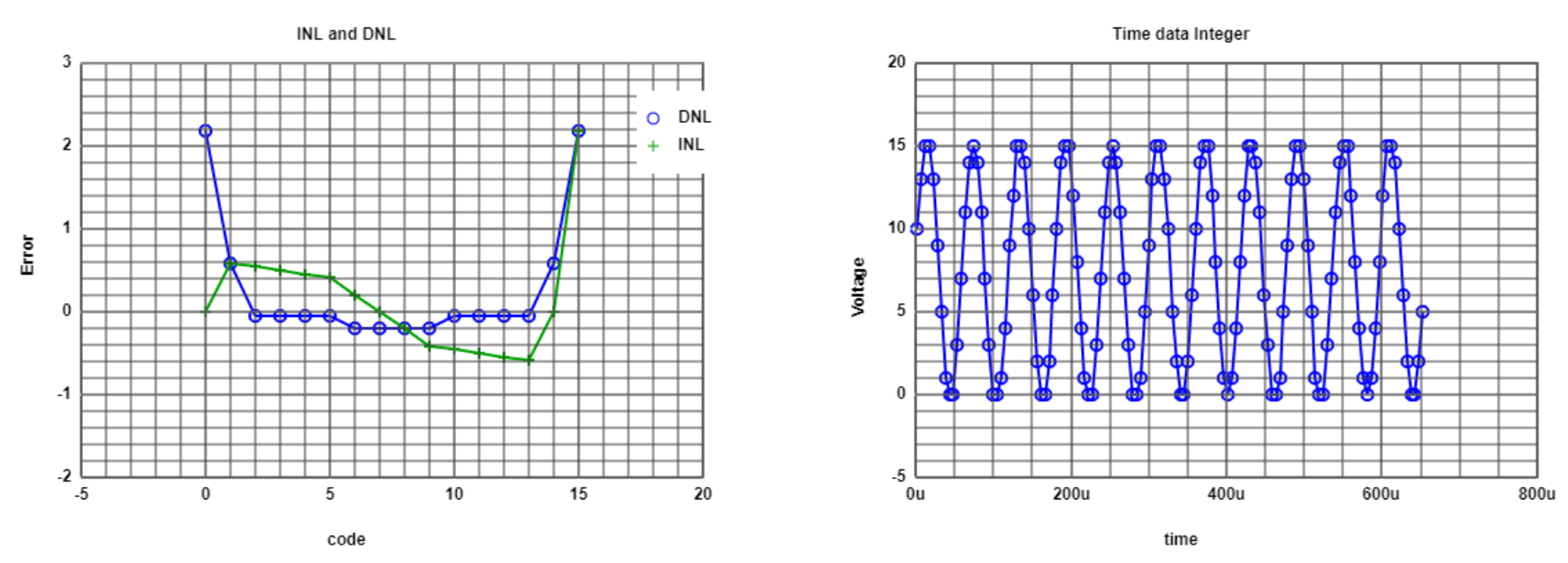

Data Analysis for Ramp Signal

|

|

|

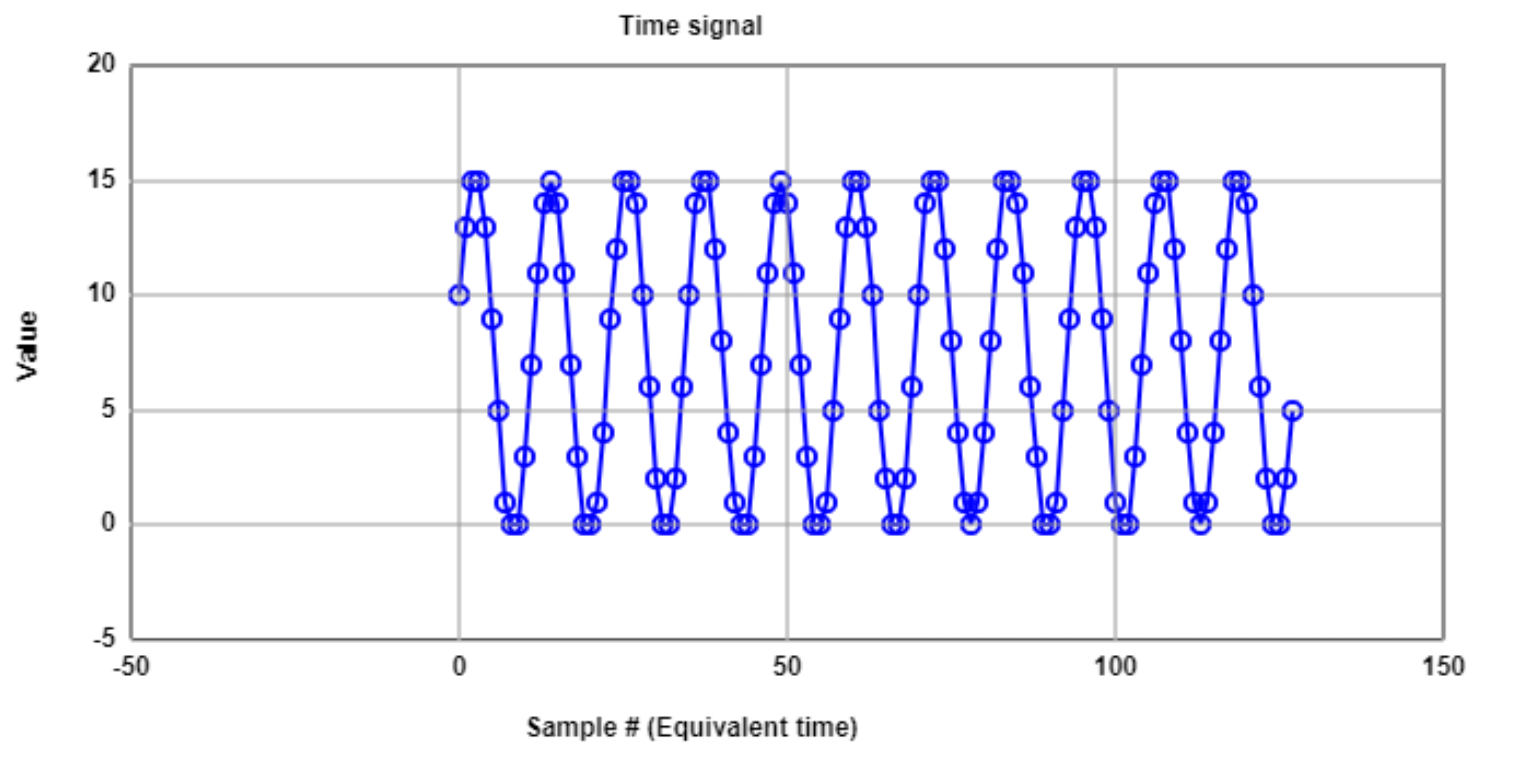

Data Analysis for Sine Input

|

|

|

|

|

|

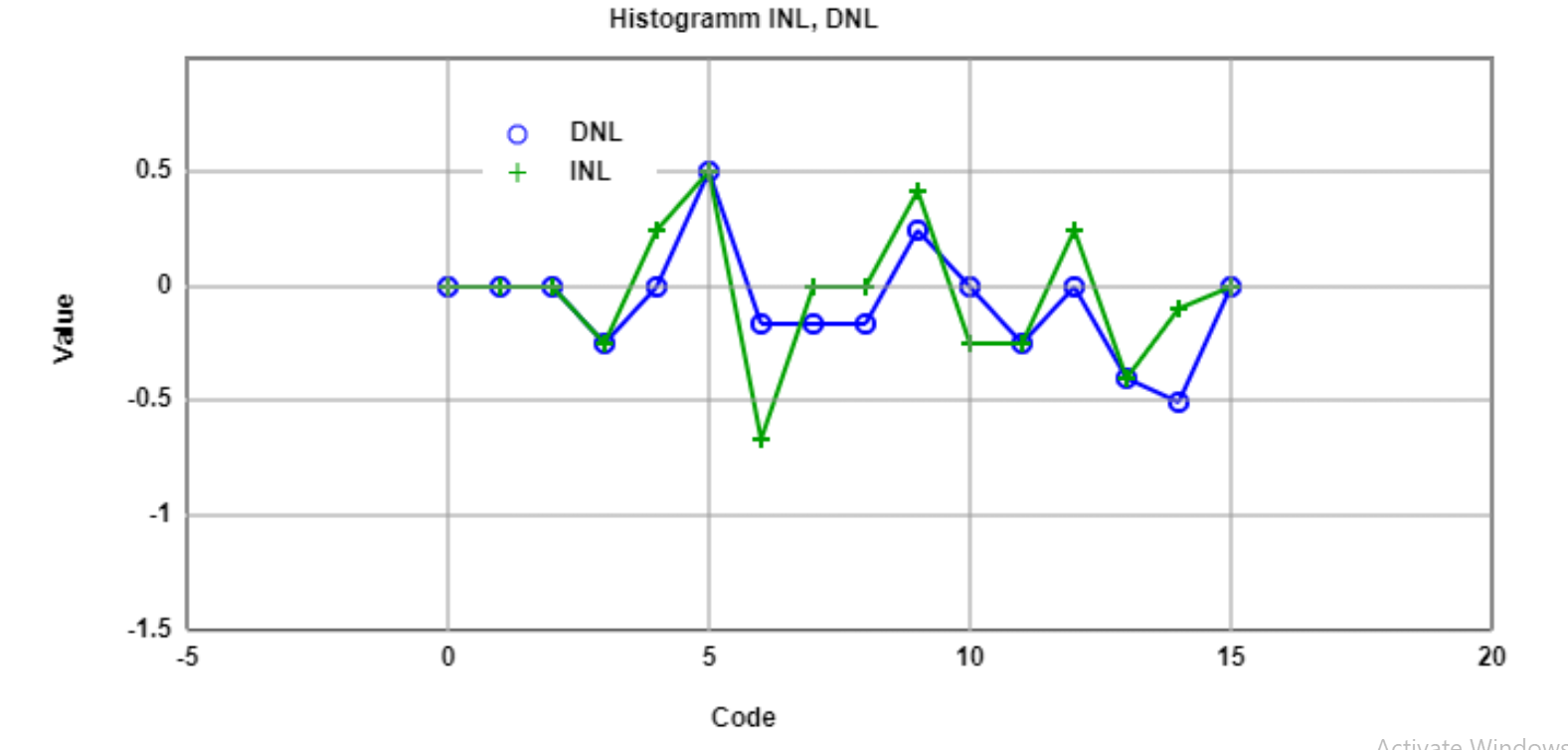

R2R DAC Simulation

- The adjacent schematic shows the 4-Bit R2R DAC |

code4Bit_ADC_DAC_pipe_R2R |

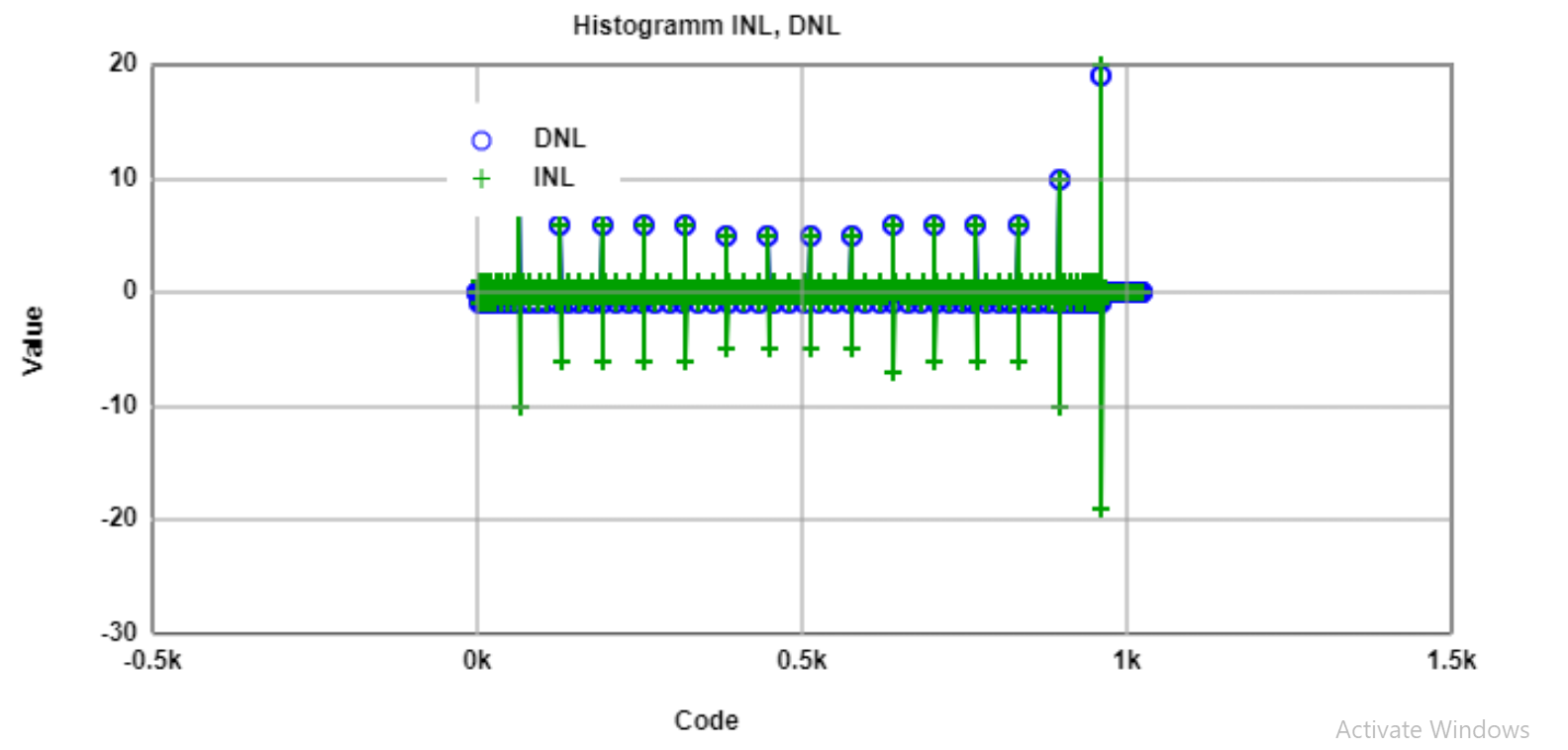

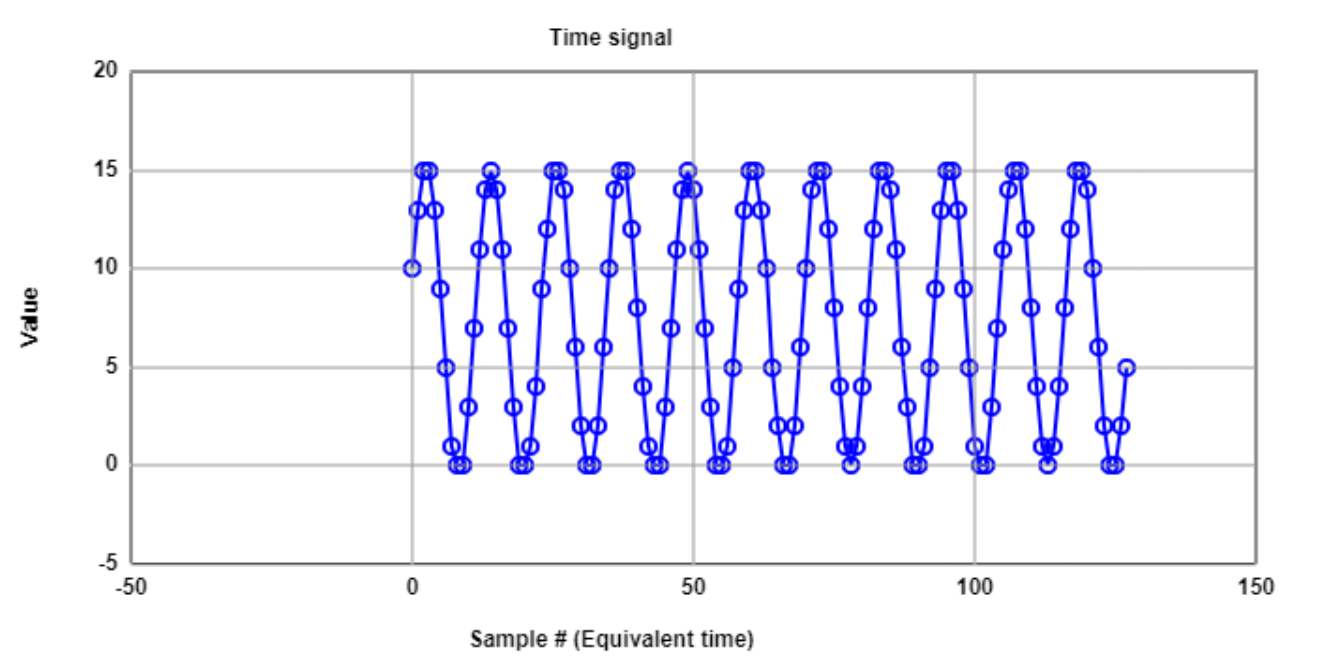

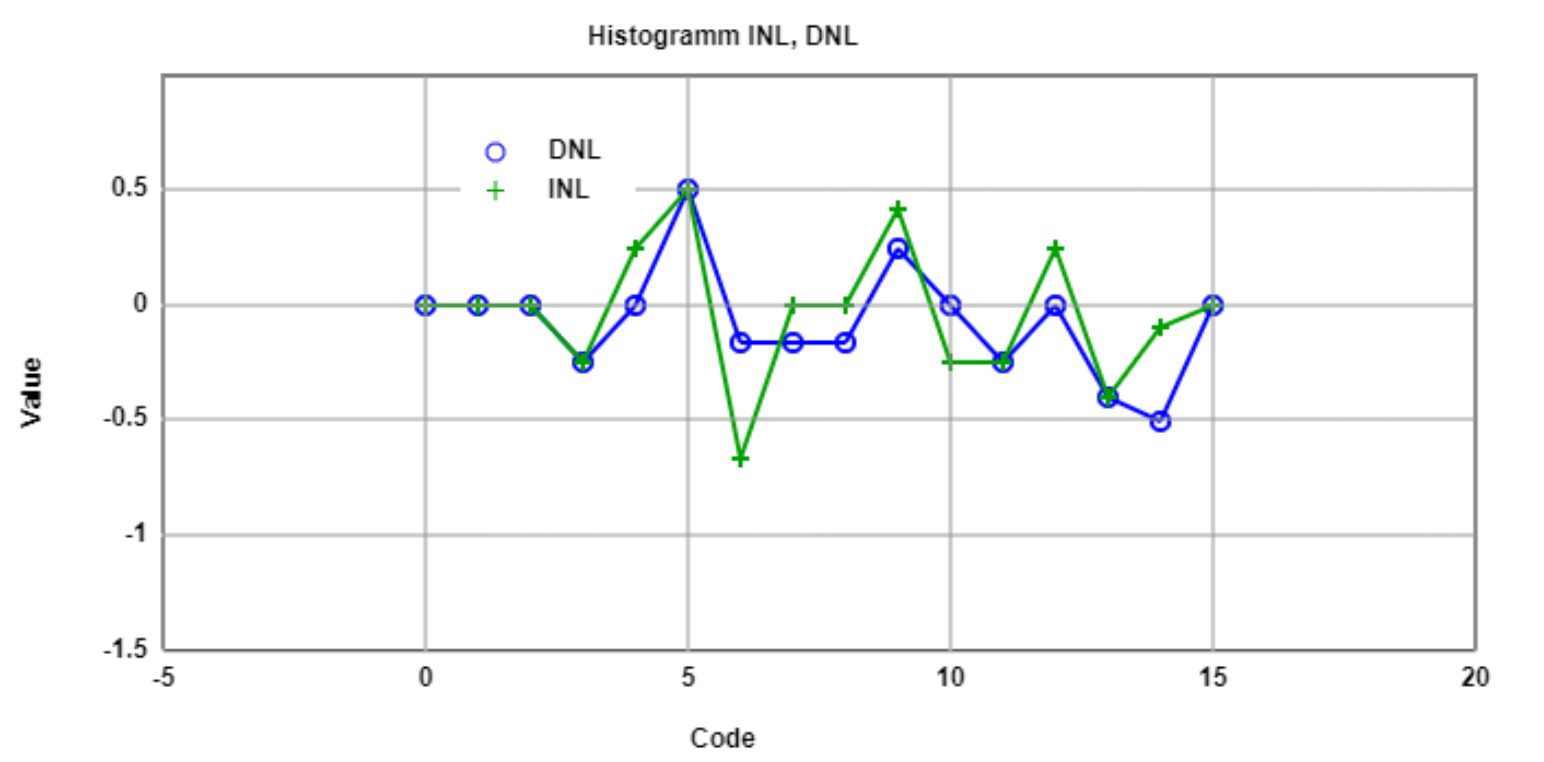

- The Histogram and INL and DNL values are shown in the following graphs.

|

|

|

- Now a ramp test is simulated and INL, DNL are calulated and the Histogram with INL and DNL values are shown in the following graphs. SummaryIn this laboratory assignment, I have performed analysis of an ideal ADC and DAC circuit. I have introduced the error via changing the values of resistor to observe the error in the ADC DAC circuit. The sine and ramp analysis are conducted and FFT spectrum, SNR, INL, DNL Histogram are observed. While reporting my findings, I have also learned how to make 2x2 table to better format the graphs and text in an HTML webpage. Hochschule für angewandte Wissenschaften Kempten, Jörg Vollrath, Bahnhofstraße 61 · 87435 Kempten Tel. 0831/25 23-0 · Fax 0831/25 23-104 · E-Mail: joerg.vollrath(at)fh-kempten.de Impressum

|