Interface ElectronicsLaboratory 01GroupB06, ***215, K |

Overview

- Install webpage template

- Download LTSpice files

- Simulation analysis

- Summary

Installation of webpage

- Download the template.zip file

- Unzip the file

- Copied Directory 2019_GroupX to 2020_GroupB06_Kunadiya

- In the directory

Test for 4 Bit ADC and DAC

|

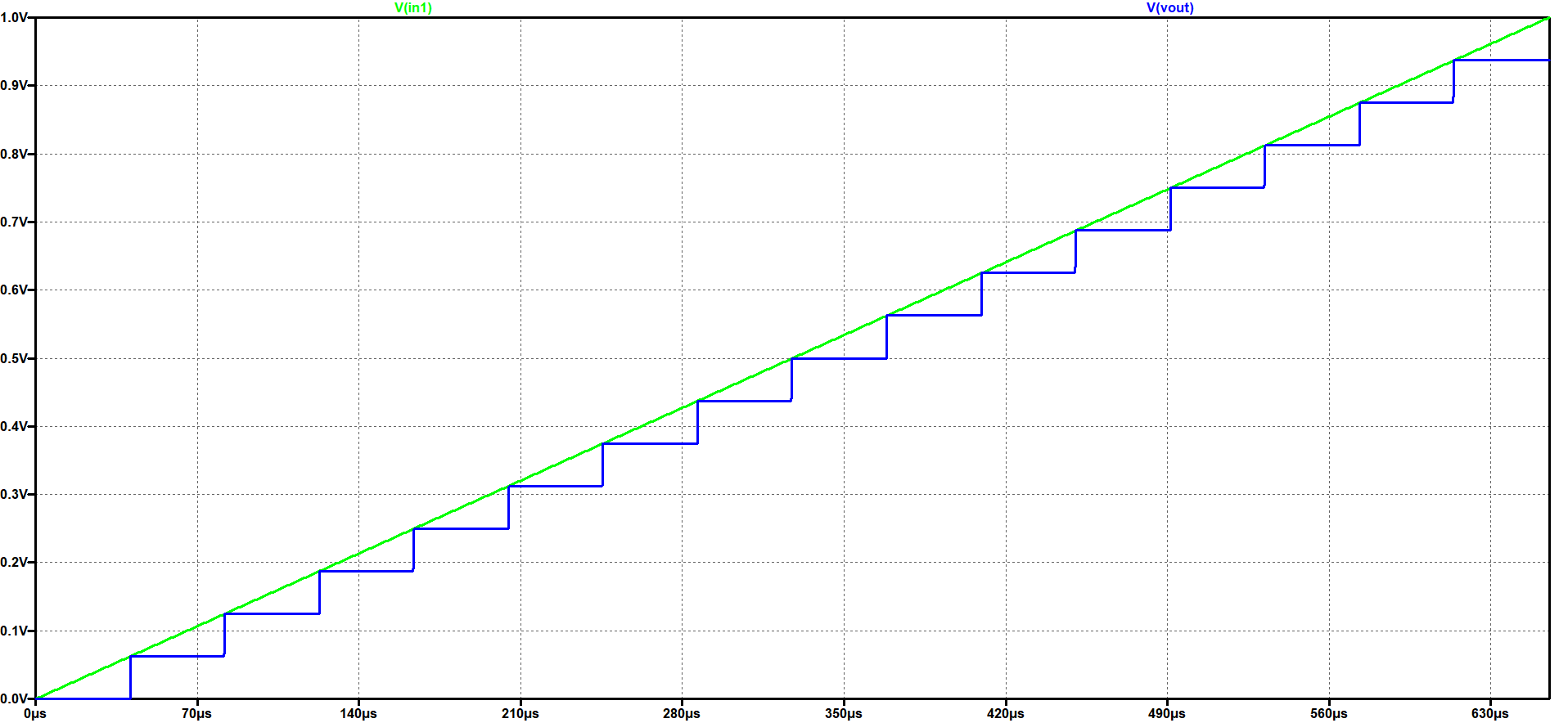

A 4 Bit ADC and DAC test can be simulated in LTSPICE. The file were download and LTSpice simulation was started. The output file size can be limited by using the .save dialog option. A voltage source was added with a ramp 0v to 1v with a rise time of 655 µs. The pictures shows a ramp impact voltage and the DAC ramp output voltage over 16 steps can be seen. With a measurement statement the voltage levels were extracted. .Measure TRAN V0000 FIND V(Vout) AT=20u At 60us time the output of 0.0625 V is given for the code 0001. V0001: V(vout)=0.0625 at 6e-005 No error in the voltage level can be seen. It is an ideal ADC and DAC.  |

LTSPICE schematics

|

JavaScript module SPICE_HTML_2018_02/LTSPICE.js Canvas, Control, Link, Code parts Add schematics to processing list ID has to be the same as the schematic name.   |

Obeseravation

|

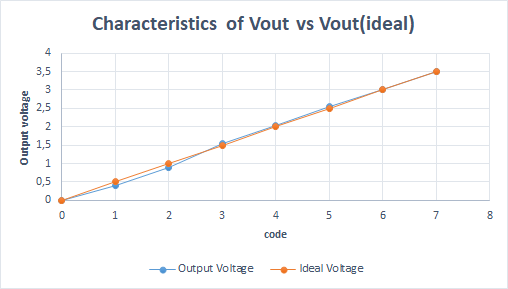

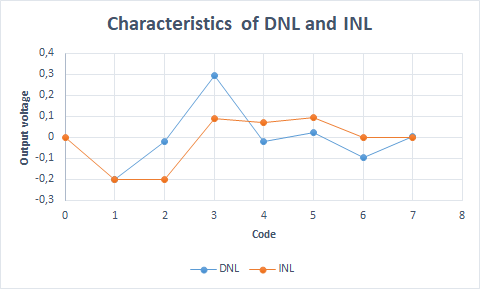

First of all I have learnt a lot of things from Lab1 . Here I observed and learnt about how to make webreport through the help of HTMLcode. Then I have learnt LTSpice simulation program. I did 4 Bit ADC and DAC simulation in the LTSpice. Then I made and observed Graph of Vout(real) vs Vout(ideal) and another Graph of DNL vs INL. |

Conclusion

|

Finally, the importance of Lab1 learn how to make webreport, another thing is how to simulated 4Bit ADC and DAC, how to use Msexcel for graph showing after do numerical terms such as calculated LSB, DNL, and INL. and show the changes of points voltage. |

References

[1] Making of a Webreport , Vollrath