Microelectronics03 ElectricProf. Dr. Jörg Vollrath |

|

Electric, LTSPICE: Simulation of a NFET, design of a layoutLänge: 1:04:23 |

0:43 Task create transistor 1:55 Bottom up approach 2:40 Take notes 3:47 Open Laboratory 1/2 web page 4:09 Electric configuration 4:22 Preferences 4:55 Maximum memory, maximum permanent space 5:17 Technology: mocmos, 6 Layers 6:01 Scale: λ = 500nm, Feature size F = 1000nm 7:35 Mark all libs 7:50 Color Scheme: White Background 8:20 Tools, Simulation, Spice 9:15 preferences: Run Spice 9:40 Command line for LTSPICE: program LTC\LTspiceXVII\XVIIx64.exe

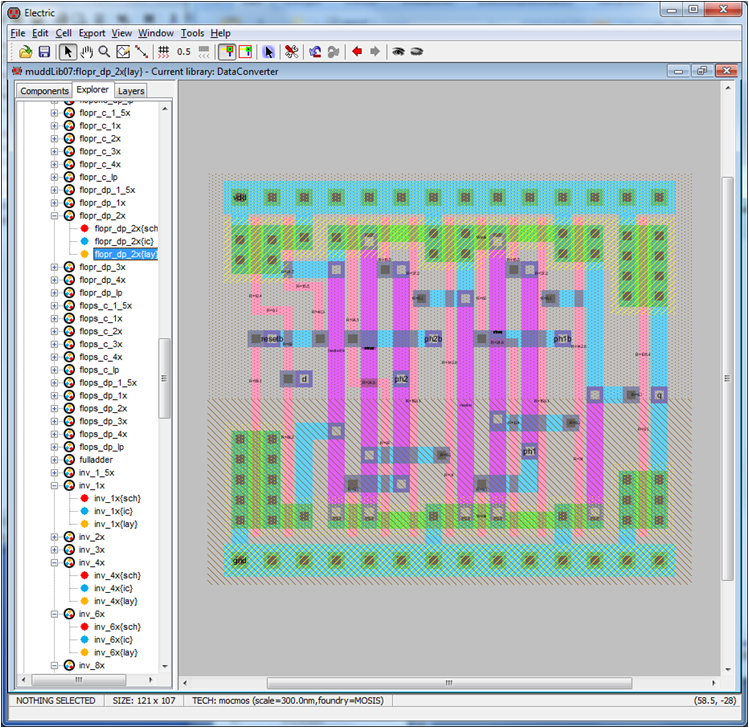

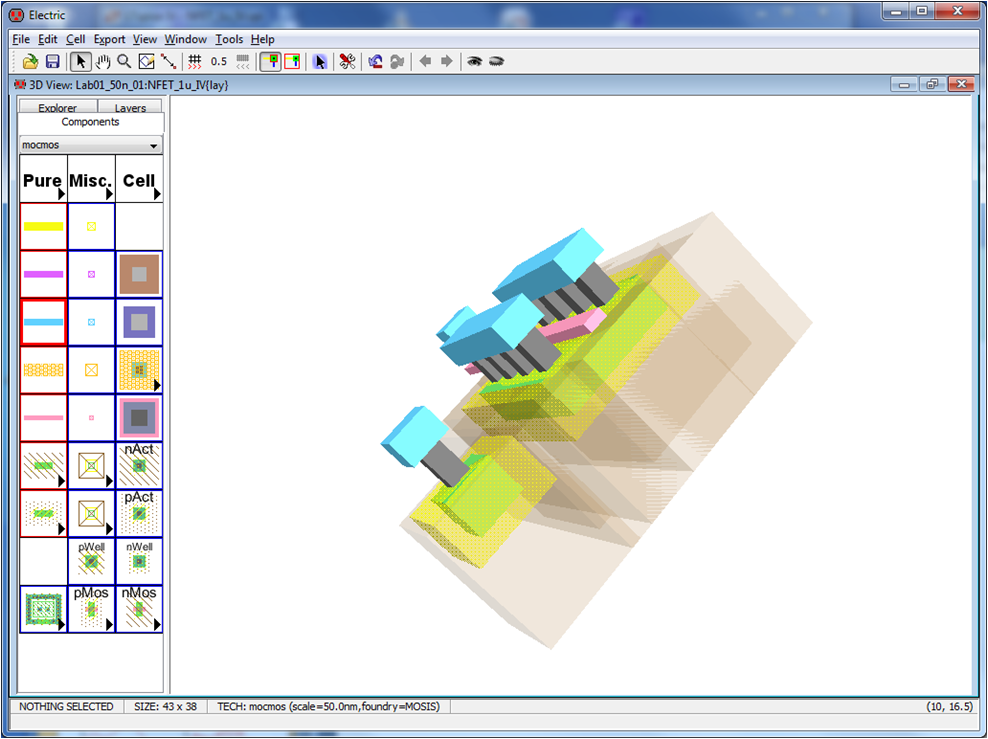

or program (x86) LTC\LTspiceIV\scad3.exe 11:20 Insert quotation marks. 13:40 Arguments for spice 14:24 Working result directory 15:50 Web page laboratory 1/2 16:47 Export Preferences Start simulation of NMOS transistor schematic 17:52 Start simulation of NMOS transistor 18:15 file copy: cmoesedu_models.txt, Lab01_1u_00.jelib 19:20 File open library 17:52 Start simulation of NMOS transistor 20:00 Electric messages 23:38 EDA explanation, tabs 24:00 Explorer, library, NFET schematic 24:33 NFET transistor pins and LTSPICE code, size 25:48 Transistor model 26:23 Voltage sources 26:42 Set Spice model 27:14 Insert LTSPICE text 28:00 Voltage sources, nodes and names 28:50 Transistor model, simulation statement 29:23 Start Spice simulation 29:40 error .option nopage just delete the options line 30:59 Schematic view 37:25 SPI file, no schematic, only netlist 37:53 run, remove .options line 38:28 add trace: show simulation curves 39:00 Output characteristic of a NFET Start layout 40:14 Create layout cell 41:10 Components 41:45 NMOS transistor layout 42:26 NMOS width and length 43:26 NMOS SPICE model name 42:43 Cycle selection 44:26 NMOS drain and source 44:50 NMOS gate polysilicon contact 45:10 Make connections 45:40 Export gate 46:50 Make connections 50:50 NFET source, drain 51:25 Connection 52:30 Resize 52:50 Design rule error 53:20 Drain export 55:40 Bulk pwell contact 56:35 SPICE text 57:00 SPICE simulation 57:20 Add trace 57:40 Voltage source VS node missing 58:40 File, save plot settings 59:30 Verifiy fix 1:01:35 Save active library |

Overview

- Electronic Design Automation (EDA)

- Electric

- Preferences

- Layout: Scale, Design Rules

- Schematic: Entry, Simulation

- Tools: Design rule check, equivalence checking

- Tool: Synthesis

- Tool: Compaction

- Libraries

- Test and Documentation

Electronic Design Automation (EDA)

- Idea to integrated circuit

- Schematic

- Layout

- Test

- Mask manufacturing

- Documentation

- Companies:

- Cadence

- Mentor

- Synopsis

Electric Layout Program

|

|

Electric Layout Program

|

|

Electric Layout Tutorial

Tutorial 1:- Start Electric

- Memory increase, background color

- Select process,

- Save library

- Start drawing resistors

- Schematic (sch), resistor, n-well, pick and place, adjust property

- Design rule check (DRC)

- Layout (lay), n-well resistor, properties

- Design rule check (DRC)

- Tool NCC Layout versus schematic (LVS)

- Circuit drawing

- Second resistor, label nodes

- Insert Spice simulation commands

- Simulate with LTSPICE

Tutorials

http://cmosedu.com/videos/electric/electric_videos.htm2016_04_12_Micro_Lab01

Electric Tools

- Tools, DRC, Check hierarchical (F5)

- Minimum size

- Minimum distance

- One object multiple errors

- Moving S/D contact to transistor with and without connection

- Simulation (Spice), Write Spice deck

- Preferences setup

- Include files for transistor models should be in target directory

- Big simulation files can be created, watch out for disk space.

- Tools, NCC, Schematic and Layout (LVS)

- Matching transistors, labels, nets, exports

- Tools, Silicon Compiler, Convert current cell to layout

- Starts with a VHDL description

- No VHDL vectors allowed

- Only structural description allowed:

Subcircuits and connections - View, Make View

- Schematic -> VHDL -> Layout