Microelectronics |

||

|

Microelectronics deals with design, manufacturing and test of integrated transistor circuits. At the beginning emphasis was on integrating as many transistors as possible in a small area achieving high operating speeds (timing closure). Nowadays in 10 nm technologies manufacturing costs and mask costs are very high and millions of transistors are available. Focus has changed to identify applications where millions of chips are needed (mobile phones) and to be able to build and verify robust circuits with millions of transistors in a short time frame. Microelectronics maintained a steady 30% productivity gain every 2 years over the last 30 years. Semiconductor manufacturing is using roadmaps, data collection and analysis (Big Data), simulation, automation in software and hardware (Industry 4.0) and dedicated test strategies (Design for test) and verification to be successfull. |

|

Strategies in microelectronics:

- Realize any solution and optimize later only when needed: Premature optimization is evil.

- Verify each step as soon as possible: Do simulations and manufacturing data measurement

- Use automation and avoid manual work: Manual work adds possible errors and takes fixed amount of time

- Expect 30% productivity increase every year

- Be right on time: Every year a new product generation is needed. Sometimes advanced products fail.

- Reuse circuits and analyze competitors.

- Any task can be divided into smaller tasks hierarchically until a solution is found.

Lecture

16.03.2026, 23.3.2026

companies, references

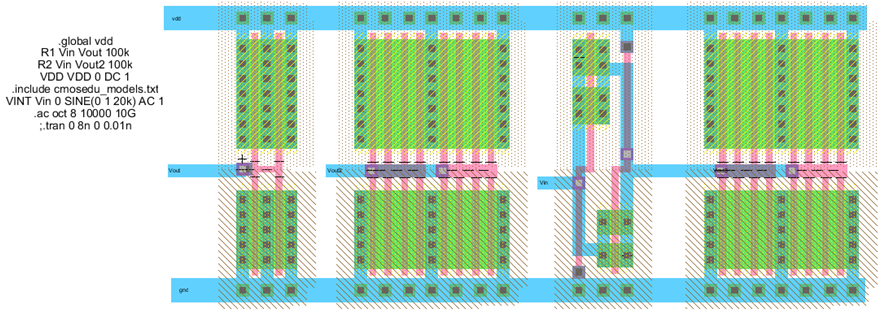

Electrical simulation (LTSPICE): LTSPICE

Design and layout: Electric VLSI design system

Reading:

Video Introduction 17.03.2021

Video Laboratory start 22.03.2021

1. Introduction:

Microelectronics, background, course content,companies, references

Electrical simulation (LTSPICE): LTSPICE

Design and layout: Electric VLSI design system

Reading:

Video Introduction 17.03.2021

Video Laboratory start 22.03.2021

23.03.2026

History

Moore's law

MOSFET transistor to chip

Reading:

Video Moore, Hierarchy, Inverter 24.03.2021

2. Microelectronics History

Transistor evolutionHistory

Moore's law

MOSFET transistor to chip

Reading:

Video Moore, Hierarchy, Inverter 24.03.2021

23.03.2026

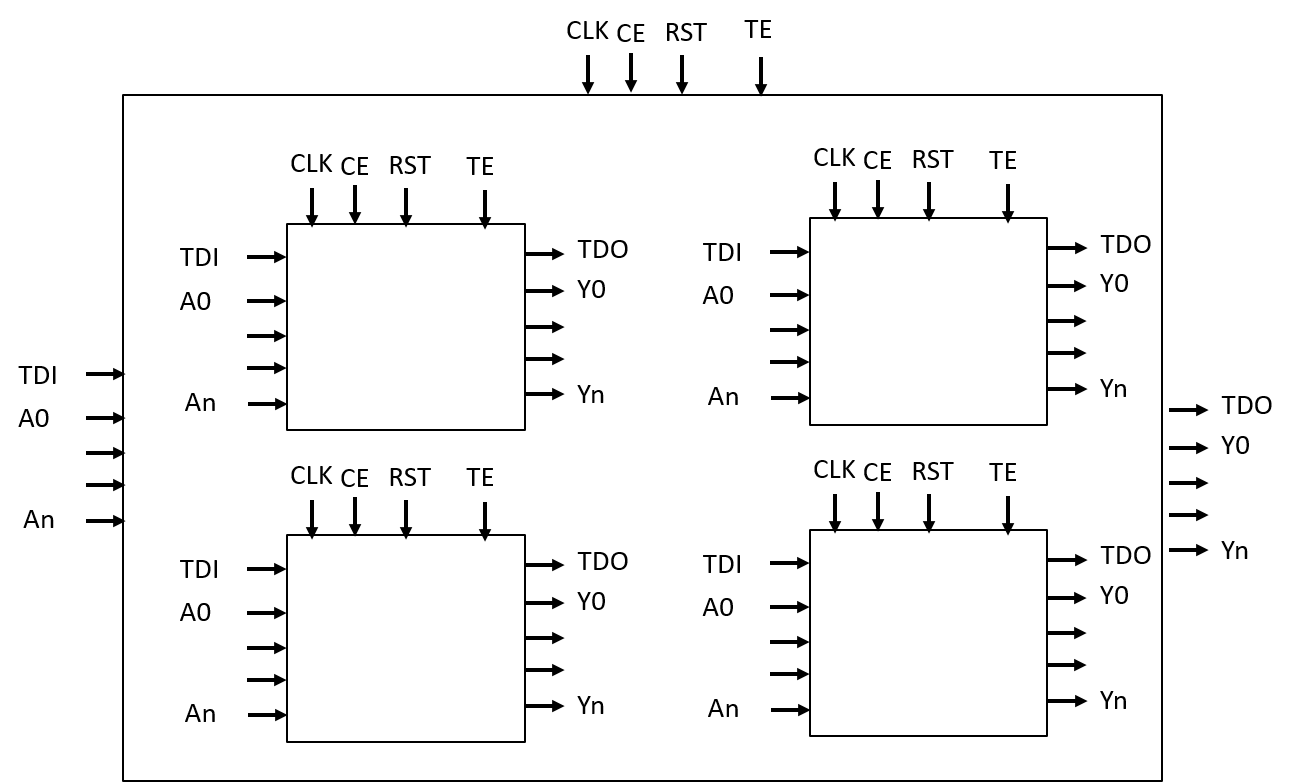

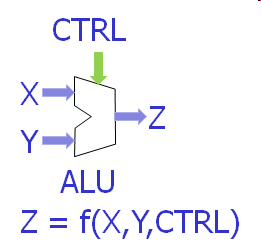

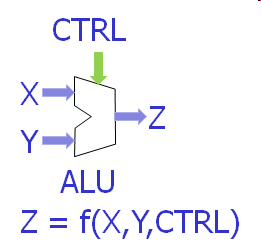

Design flow of Systems

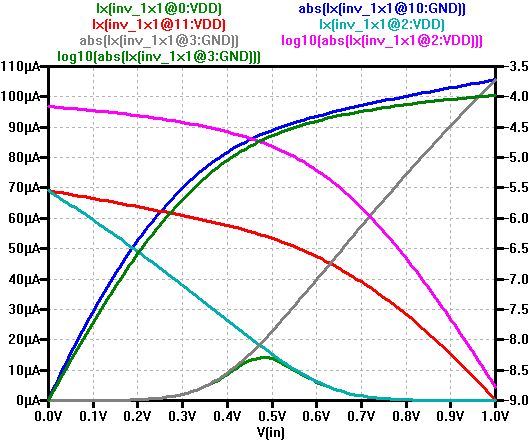

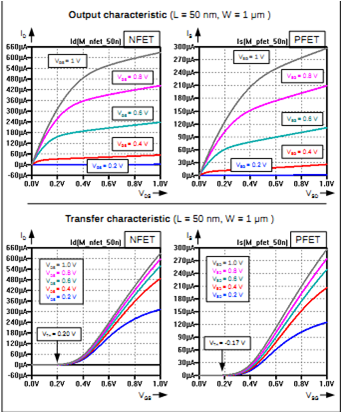

MOSFET: IV curves

Vth, β = KP/2, λ

Transfer and output curves

Static equation

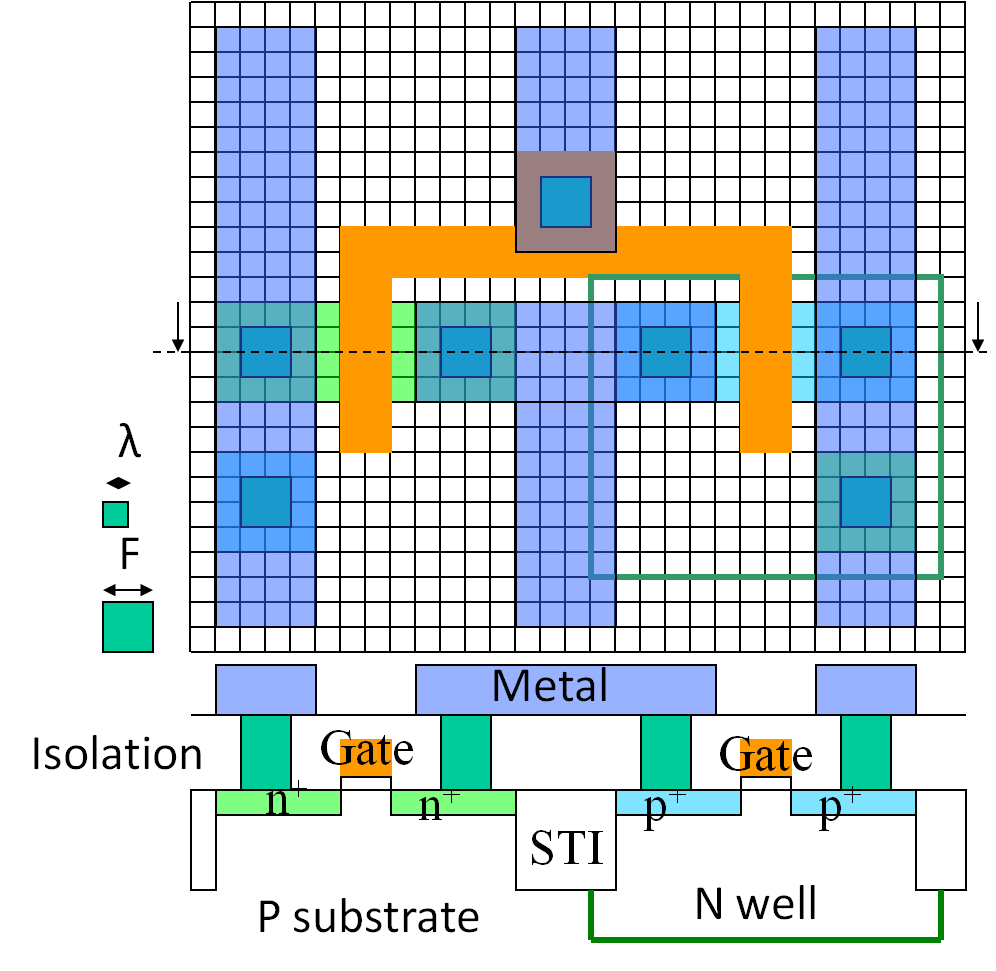

Layout and cross section

Reading:

Video MOSFET 31.03.2021

3. MOSFET

ASIC, FPGA and microcontroller technologiesDesign flow of Systems

MOSFET: IV curves

Vth, β = KP/2, λ

Transfer and output curves

Static equation

Layout and cross section

Reading:

Video MOSFET 31.03.2021

30.03.2026

MOSFET switch model(R, C),

Inverter

IV curve

Propagation delay

Standard cell

Pass gate (PG)

Transmission gate (TG)

Laboratory 01: Design and simulation of 1μm and 50 nm CMOS transistors

Reading:

Video Inverter 14.04.2021

4. MOSFET Inverter:

MOSFET as capacitorMOSFET switch model(R, C),

Inverter

IV curve

Propagation delay

Standard cell

Pass gate (PG)

Transmission gate (TG)

Laboratory 01: Design and simulation of 1μm and 50 nm CMOS transistors

Reading:

Video Inverter 14.04.2021

13.04.2026

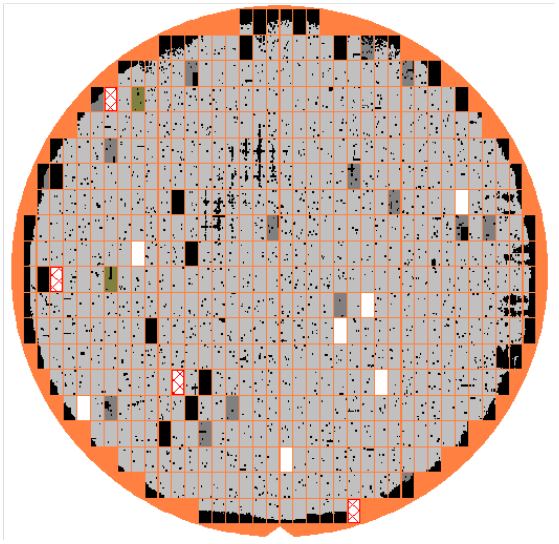

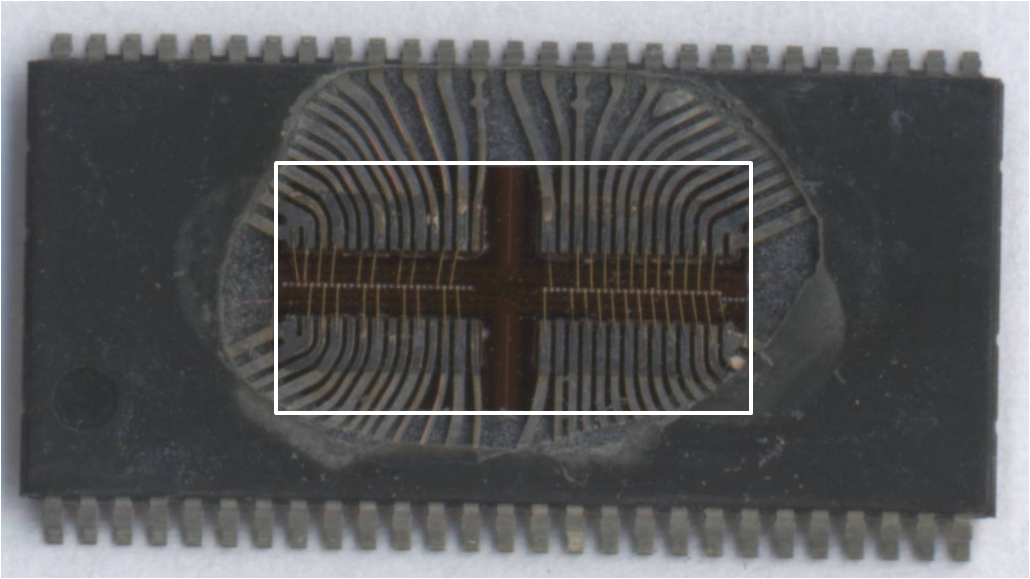

Yield

Fabrication process

Top view, Cross section

Laboratory 02: Design and simulation of 1 μm and 50 nm CMOS transistors

Reading:

Video Process 19.04.2021

5. IC Manufacturing:

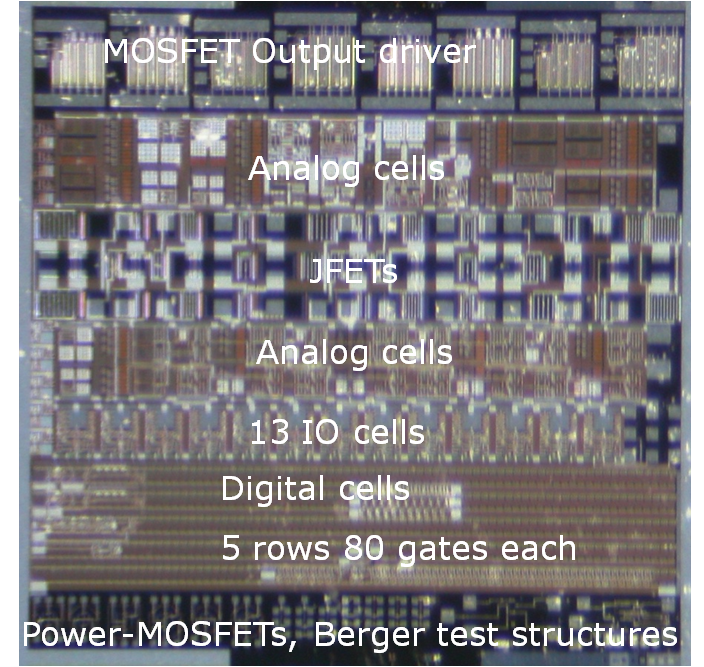

Wafer, chipsYield

Fabrication process

Top view, Cross section

Laboratory 02: Design and simulation of 1 μm and 50 nm CMOS transistors

Reading:

Video Process 19.04.2021

20.04.2026

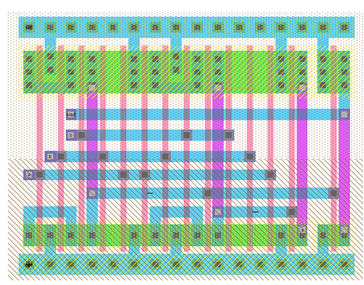

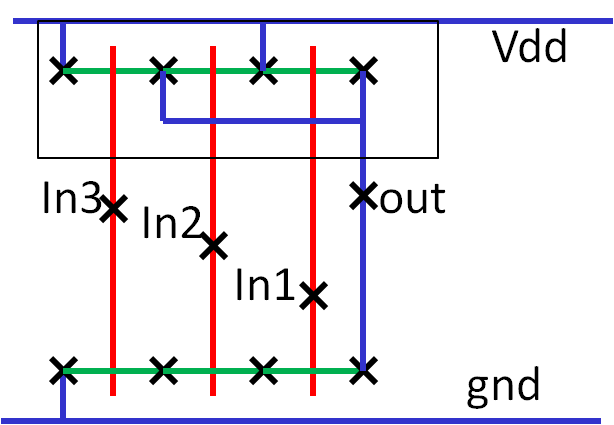

Layout and stick diagram

Laboratory 03: Design and simulation of 1 μm and 50 nm CMOS transistors

Reading:

Video Design Rules 28.04.2021

6. Design Rules and Alignment

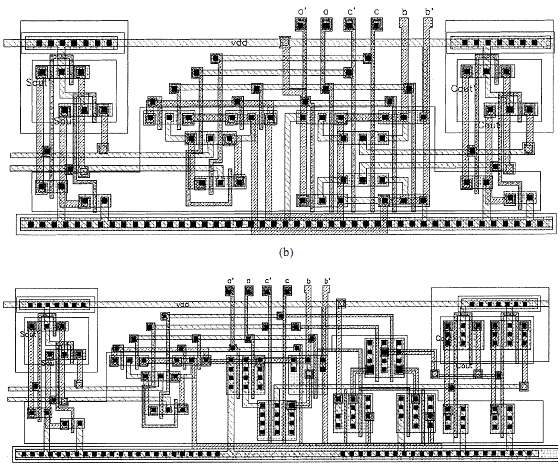

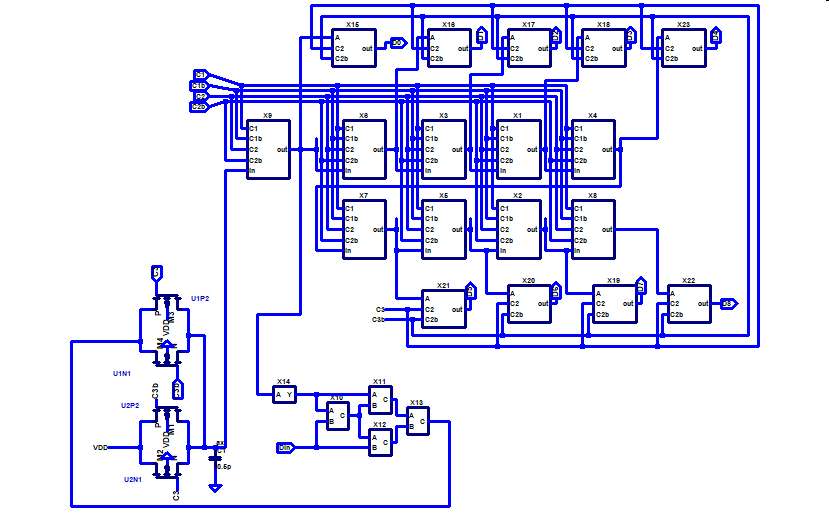

SchematicLayout and stick diagram

Laboratory 03: Design and simulation of 1 μm and 50 nm CMOS transistors

Reading:

Video Design Rules 28.04.2021

27.04.2026

AOI (AND, OR, INVERT) design style,

Laboratory 04: A CMOS inverter

Reading:

Video RLC and CMOS Logic 5.05.2021

Video Silicon Compiler 10.05.2021

7. RLC in Microelectronics

NAND gate: parasitic resistance and capacitance, RCX extraction From logic gate layout to chip layout,AOI (AND, OR, INVERT) design style,

Laboratory 04: A CMOS inverter

Reading:

Video RLC and CMOS Logic 5.05.2021

Video Silicon Compiler 10.05.2021

04.05.2026

Cell layout,

System synthesis,

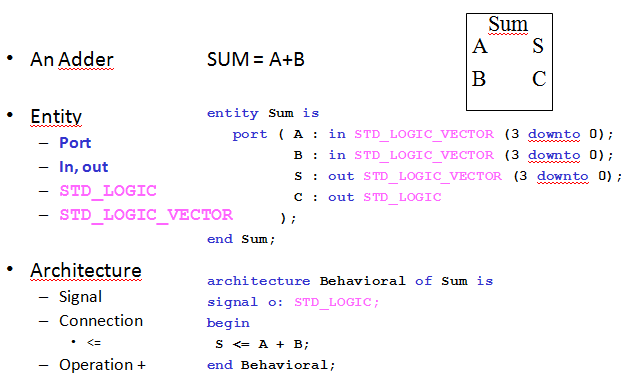

VHDL entity and architecture

Synthesis and silicon compiler

VHDL hardware definition language

Entity, architecture, ports, busses, signals, hierarchy, state machine, test

Laboratory 05: A CMOS inverter

12.05.2021 Video Truth table design style, VHDL

Reading:

17.05.2021 Video Laboratory Multiplier

8. Silicon Compiler: From VHDL to Layout

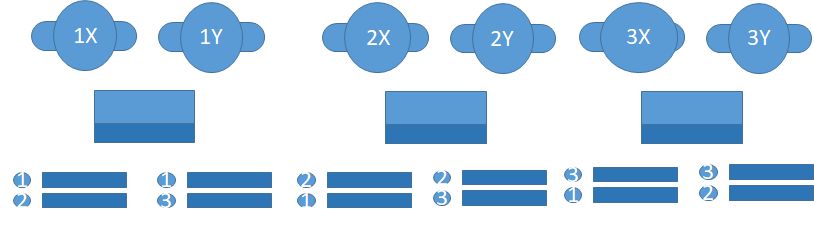

Unit Transistor,Cell layout,

System synthesis,

VHDL entity and architecture

Synthesis and silicon compiler

VHDL hardware definition language

Entity, architecture, ports, busses, signals, hierarchy, state machine, test

Laboratory 05: A CMOS inverter

12.05.2021 Video Truth table design style, VHDL

Reading:

17.05.2021 Video Laboratory Multiplier

11.05.2026

Delay and pipeline operation

Reading:

Video Delay and power 2.06.2021

Video Laboratory Multiplier 31.05.2021

9. FPGA, VHDL and Delay

ASIC, FPGADelay and pipeline operation

Reading:

Video Delay and power 2.06.2021

Video Laboratory Multiplier 31.05.2021

18.05.2026

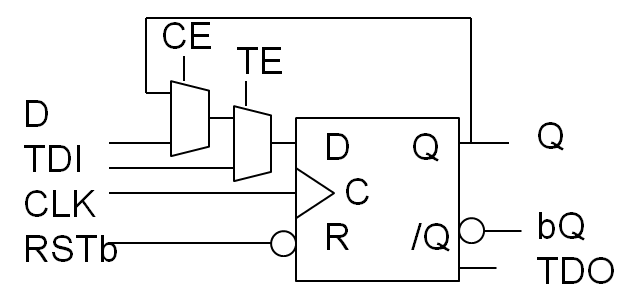

State machine

Scan FF

Reading:

D-Flip-Flop, state machine 9.06.2021

Video Laboratory Multiplier 7.06.2021

10. Microelectronics System Design

D-Flip-FlopState machine

Scan FF

Reading:

D-Flip-Flop, state machine 9.06.2021

Video Laboratory Multiplier 7.06.2021

01.06.2026

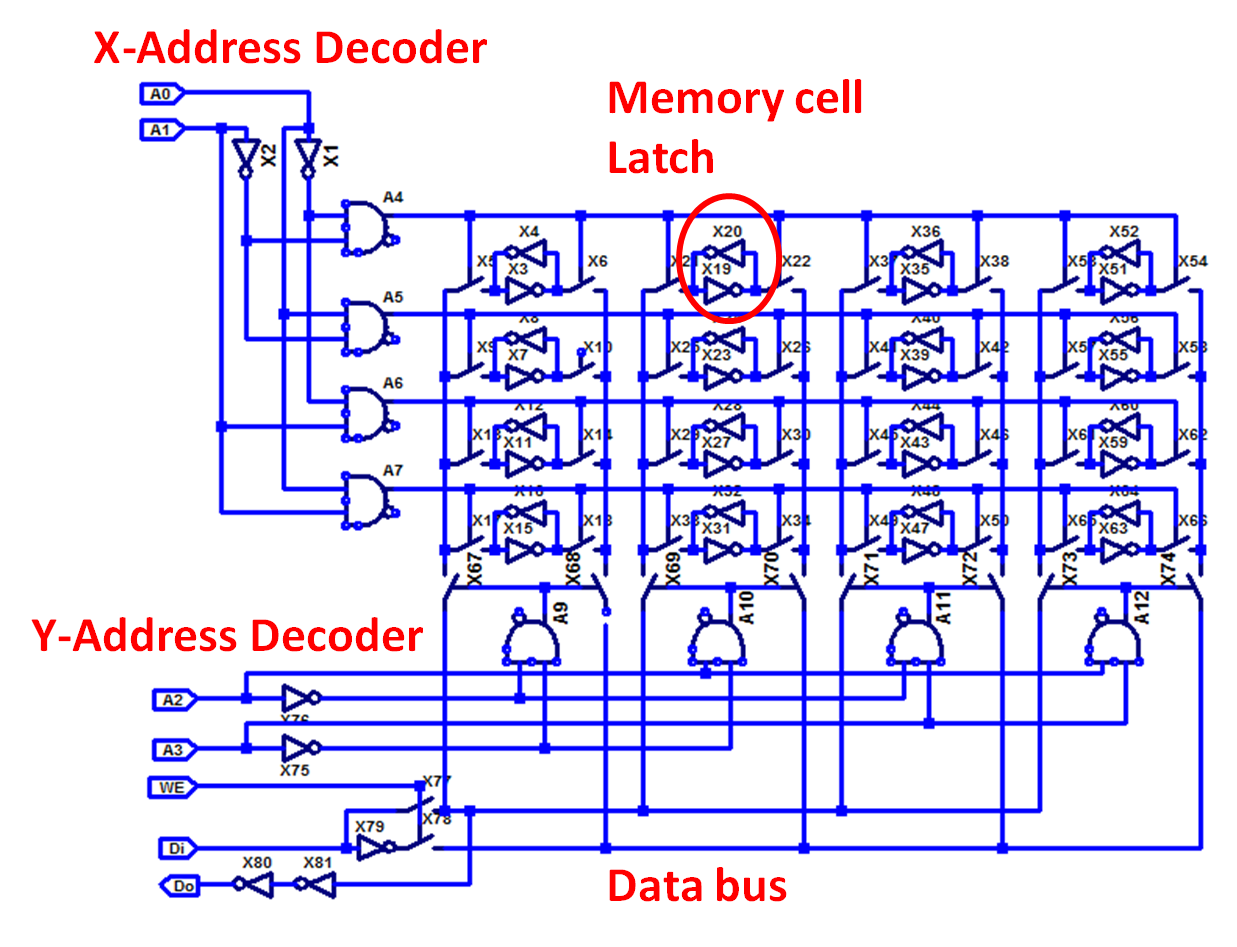

Example:Samsung 21nm, 48LV, 3 Bit per cell, 256Gb NAND Flash

Reading:

Video Memories 16.6.2021

Video Laboratoray 14.06.2021

11. Memories

SRAM, DRAM, FlashExample:Samsung 21nm, 48LV, 3 Bit per cell, 256Gb NAND Flash

Reading:

Video Memories 16.6.2021

Video Laboratoray 14.06.2021

8.06.2026

Input outputs,

Clock

Reading:

Video Power, vdd, clock and input outputs 19.05.2020

Notes about laboratory 20.05.2020

12. Power

Package,Input outputs,

Clock

Reading:

Video Power, vdd, clock and input outputs 19.05.2020

Notes about laboratory 20.05.2020

15.06.2026

Challenges of microelectronics

Review

Laboratory: Progress and Questions

Reading:

Video Design for test, faults, test 26.05.2020

13. Design for Test

DefectsChallenges of microelectronics

Review

Laboratory: Progress and Questions

Reading:

Video Design for test, faults, test 26.05.2020