Microelectronics Laboratory2023 Synthesis of a PWMProf. Dr. Jörg Vollrath |

Outline

- Specification of a PWM

- C description of a PWM

- VHDL description of a PWM

- Specification, block diagram, subcircuits

- Summary

This laboratory shows an example of a layout synthesis without using commercial tools.

A step by step update will be done.

A step by step update will be done.

Specification

|

|

- Input and output signals

Input: CLK, WE, A0, D0..Di, EN Output: PWM - Include a clock generator?

- Make a schematic, layout and simulation

- Extract propagation delay and power consumption

- Make a data sheet

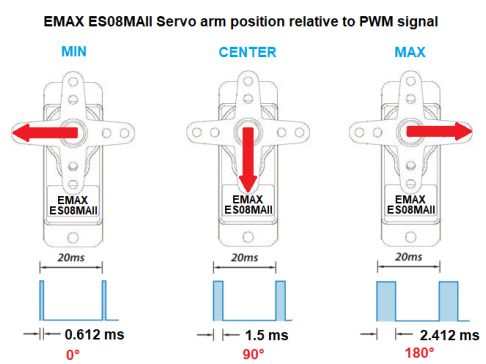

Count: 20 ms / 10 ns = 2 000 000

N-Bits: 21

CountH: 2.412 ms = 241 200

NH-Bis: 18

N-Bits: 21

CountH: 2.412 ms = 241 200

NH-Bis: 18

PWM Realization

- Arduino Maker WiFi 1010

- BASYS3 FPGA

VHDL description of a PWM

VHDL code from:

FPGA Prototyping by VHDL Examples, Xilinx Spartan-3 Version, Chu, Wiley, ca 90.- Euro,

http://academic.csuohio.edu/chu_p/rtl/ VHDL modules:

- Generic modulo m counter: list_ch04_11_mod_m.vhd

- Test: Timing behaviour

- Create PWM variants

- Full length up counter

- Full length down counter

- 4-Bit scalable up counter

- 4-Bit scalable down counter

- Test PWM

- Synthesize, measure

BASYS3 pin connection file

- Start Vivado and create new project "PWM_<lastName2Initials><FirstName2Initials>"

- Select Default part "xc7a35tcpg236-1" for BASYS3 board

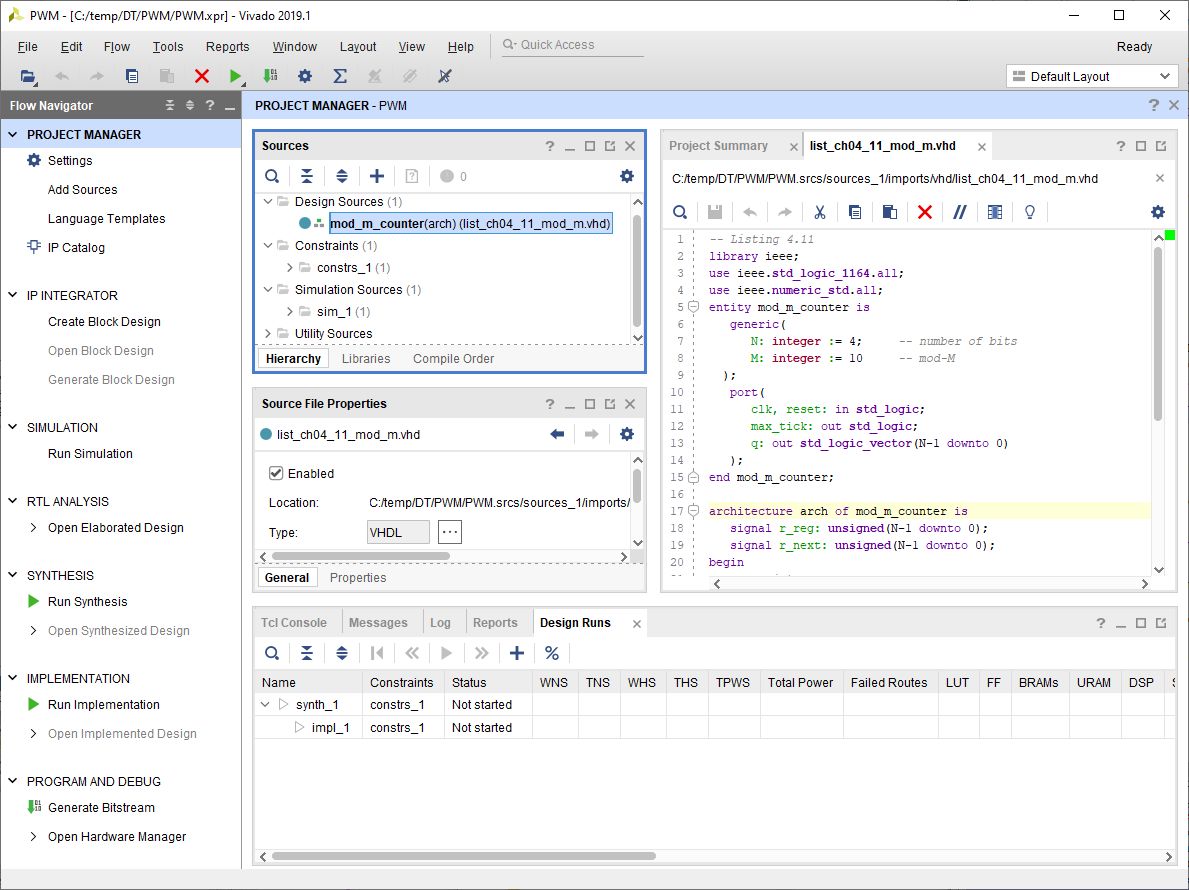

Xilinx Vivado PWM

Start Xilinx Vivado. Configure the project part "xc7a35tcpg236-1" for BASYS3 board and VHDL.

Figure: Vivado project manager

Add list_ch04_11_mod_m.vhd as Design Sources

Add Basys3_Master.xdc as Constraints

Edit constraint file: switches, LED counter selection and setting (upper bits),

PMOD: PWM signal for servo and oscilloscope

Create top level pwm

Create test top level pwm

Create variants

Create synthesis file:

After synthesis run Tcl console write_vhdl <filename>. This gives a structural post synthesis description.

Add Basys3_Master.xdc as Constraints

Add list_ch04_11_mod_m.vhd as counter

Add top_pwm.vhd as top file connecting to hardware

Add top_pwm_sim.vhd for simulation

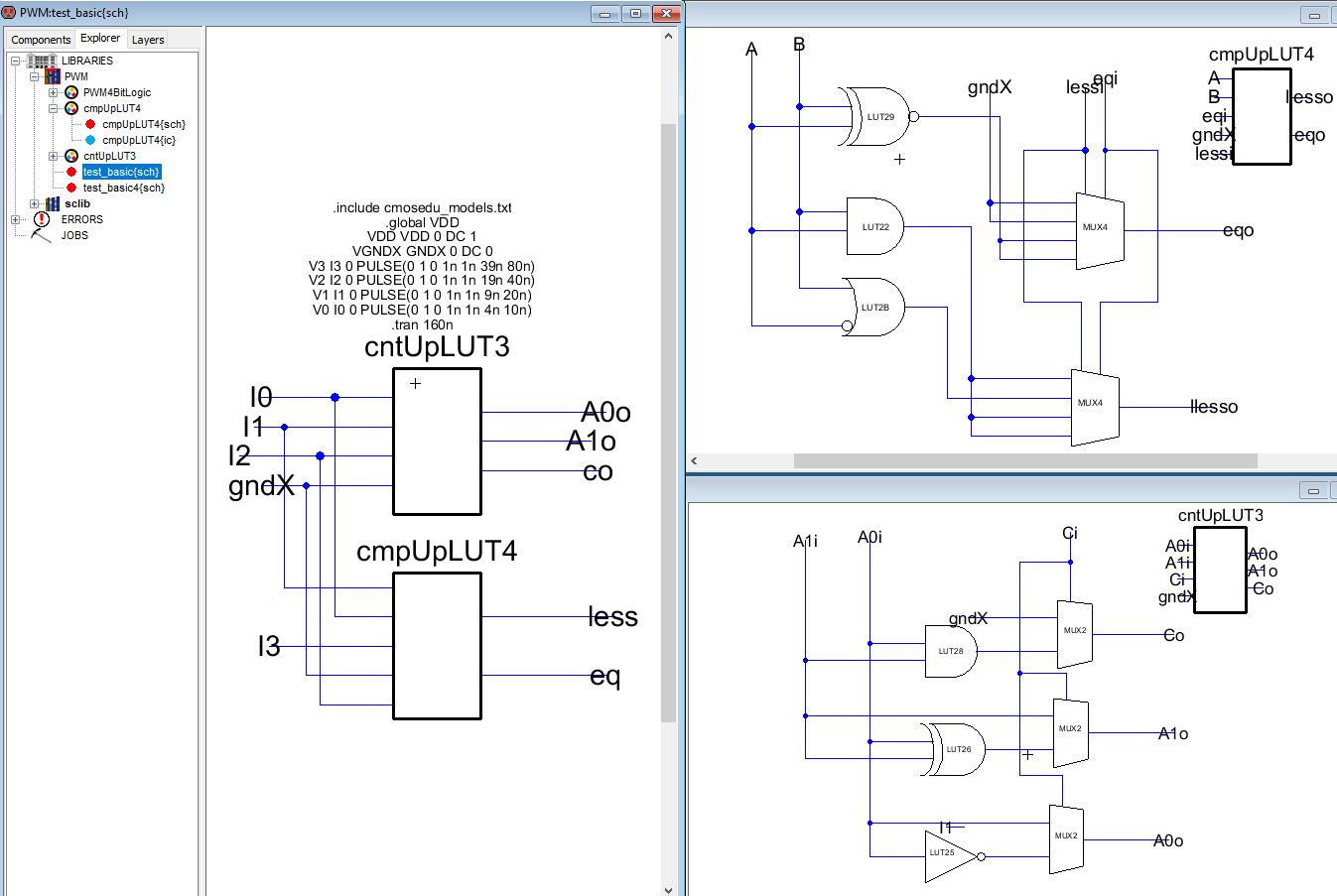

I0 is mapped to cntUpLUT3:A0i and cmpUpLUT3:B

I1 is mapped to cntUpLUT3:A1i and cmpUpLUT3:A

I2 is mapped to cntUpLUT3:Ci and cmpUpLUT3:lessi

I3 is mapped to cmpUpLUT3:eqi

The sequence is chosen according to the truth table columns

Create top level pwm

Create test top level pwm

Create variants

Create synthesis file:

After synthesis run Tcl console write_vhdl <filename>. This gives a structural post synthesis description.

Add Basys3_Master.xdc as Constraints

Add list_ch04_11_mod_m.vhd as counter

Add top_pwm.vhd as top file connecting to hardware

Add top_pwm_sim.vhd for simulation

I0 is mapped to cntUpLUT3:A0i and cmpUpLUT3:B

I1 is mapped to cntUpLUT3:A1i and cmpUpLUT3:A

I2 is mapped to cntUpLUT3:Ci and cmpUpLUT3:lessi

I3 is mapped to cmpUpLUT3:eqi

The sequence is chosen according to the truth table columns

Analysis of synthesis file PWM

Electric_mod_m_counter_synthesis.vhdThe modulo 10 counter has a structural description with primitives:

IBUF, OBUF, FDCE, LUT1, LUT6, LUT4, CARRY4

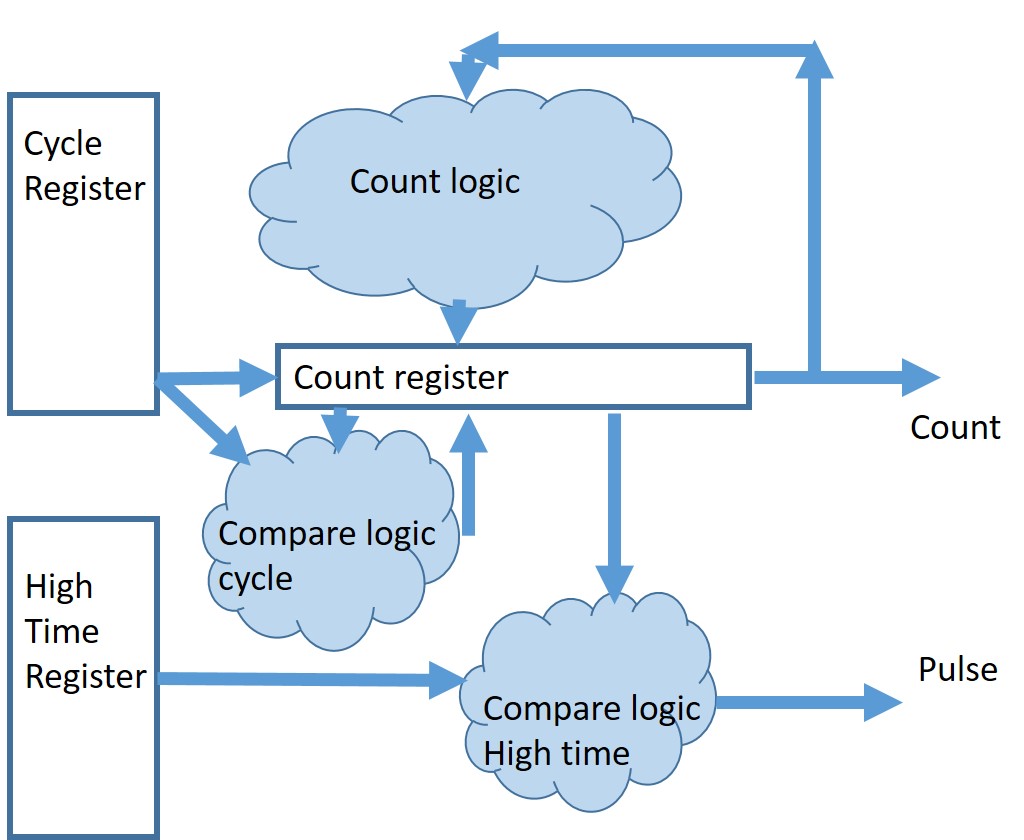

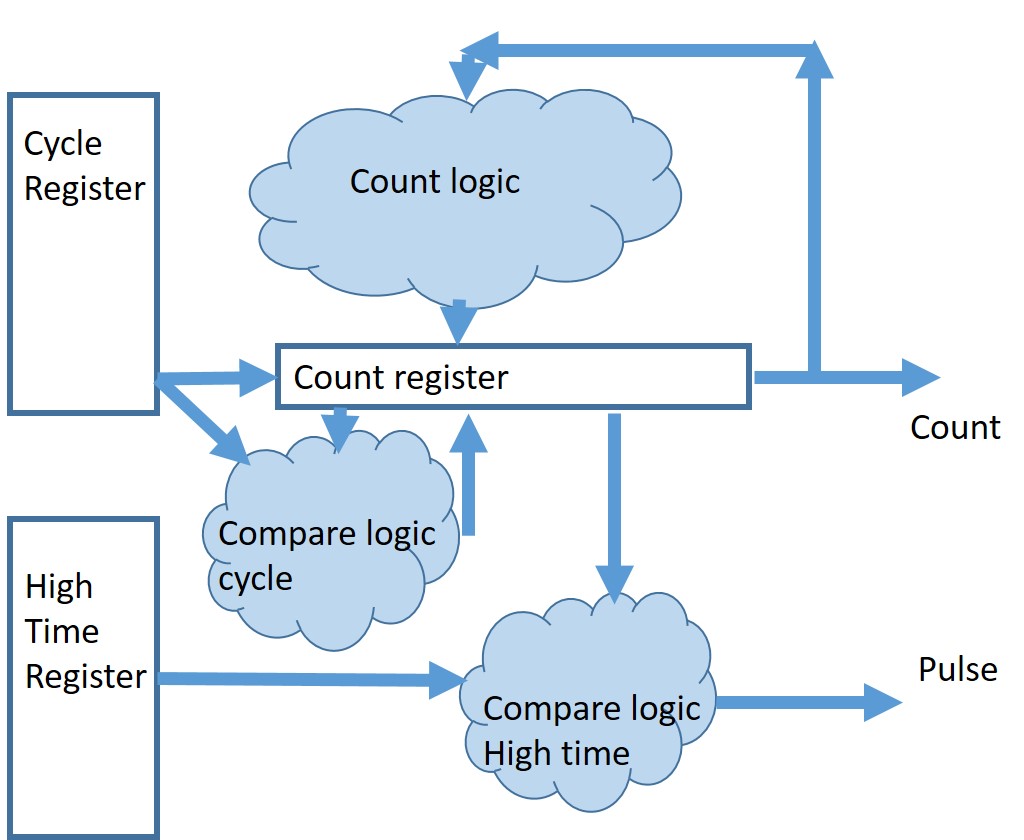

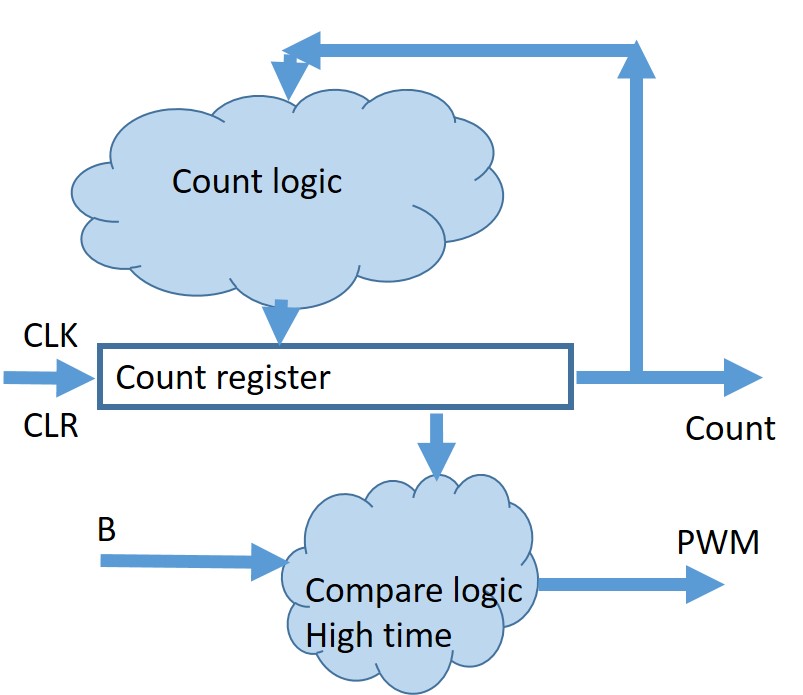

PWM Break down

Blocks:

|

|

PWM Break down

Variations:

|

|

PWM Task Reduction

4 Bit Variations:

|

|

Work plan

4-Bit PWM with fixed high time

|

|

Scalable 2 bit count LUT3 truth table

The name is chosen for a counter (cnt), counting up (Up), having 3 inputs Ci, A1, A0 needing a LUT3

cntUpLUT3

The counter could count down (Dn) or more inputs could be used with a bigger lookup table:

Ci, A2, A1, A0 needing a LUT4

Ci, A3, A2, A1, A0 needing a LUT5

Ci, A4, A3, A2, A1, A0 needing a LUT6

| countup LUT3 | ||||||

| Ci | A1i | A0i | Co | A1o | A0o | |

| 0 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 0 | 0 | 1 | |

| 0 | 1 | 0 | 0 | 1 | 0 | |

| 0 | 1 | 1 | 0 | 1 | 1 | |

| 1 | 0 | 0 | 0 | 0 | 1 | |

| 1 | 0 | 1 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 0 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 0 | 0 | |

Co = LUT3_08; A1o = LUT3_C6; A0o = LUT3_A5;

LUT2A = I0

LUT20 = gndX

LUT2C = I1

LUT2F = vddX

| I1 | I0 | LUT20 | LUT21 | LUT22 | LUT23 | LUT24 | LUT25 | LUT26 | LUT27 | LUT28 | LUT29 | LUT2A | LUT2B | LUT2C | LUT2D | LUT2E | LUT2F |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| gndX | NOR | NOT(I1) | NOT(I0) | I0 XOR I1 | I0 NAND I1 | I0 AND I1 | IO XNOR I1 | I0 | I1 | I0 NOR I1 | vddX |

Scalable 1 bit compare LUT4 truth table

The name is for a comparator (cmp), comparing starting from LSB and propagating eq and less to MSB (Up), resulting with 4 inputs eq, less, A, B in a LUT4.

cmpUpLUT4

Propagation of eq and less could also go from MSB to LSB (Dn).

More inputs could be used (eq, less, A1, A0, B1, B0) resulting in a LUT6.

| compare Up LSB to MSB LUT4 | |||||||

| eqi | lessi | A | B | eqo | lesso | comment | |

| 0 | 0 | 0 | 0 | 0 | 0 | lower bits A greater B, this bit A equals B, result A greater B | |

| 0 | 0 | 0 | 1 | 0 | 1 | lower bits A greater B, this bit A less B, result A less B | |

| 0 | 0 | 1 | 0 | 0 | 0 | lower bits A greater B, this bit A greater B, result A greater B | |

| 0 | 0 | 1 | 1 | 0 | 0 | lower bits A greater B, this bit A equals B, result A greater B | |

| 0 | 1 | 0 | 0 | 0 | 1 | lower bits A less B, this bit A equals B, result A less B | |

| 0 | 1 | 0 | 1 | 0 | 1 | lower bits A less B, this bit A less B, result A less B | |

| 0 | 1 | 1 | 0 | 0 | 0 | lower bits A less B, this bit A greater B, result A greater B | |

| 0 | 1 | 1 | 1 | 0 | 1 | lower bits A less B, this bit A equals B, result A less B | |

| 1 | 0 | 0 | 0 | 1 | 0 | lower bits A equals B, this bit A equals B, result A equals B | |

| 1 | 0 | 0 | 1 | 0 | 1 | lower bits A equals B, this bit A less B, result A less B | |

| 1 | 0 | 1 | 0 | 0 | 0 | lower bits A equals B, this bit A greater B, result A greater B | |

| 1 | 0 | 1 | 1 | 1 | 0 | lower bits A equals B, this bit A equals B, result A equals B | |

| 1 | 1 | 0 | 0 | 1 | 0 | lower bits not there, this bit A equals B, result A equals B | |

| 1 | 1 | 0 | 1 | 0 | 1 | lower bits not there, this bit A less B, result A less B | |

| 1 | 1 | 1 | 0 | 0 | 0 | lower bits not there, this bit A greater B, result A greater B | |

| 1 | 1 | 1 | 1 | 1 | 0 | lower bits not there, this bit A equals B, result A equals B | |

| eqi | lessi | comment |

| 0 | 0 | A greater B |

| 0 | 1 | A less B |

| 1 | 0 | A equals B |

| 1 | 1 | lower bits not present |

eqo (eqi, lessi, A, B) = LUT4_0099 = MUX4(LUT20;LUT20;LUT29;LUT29);

eqo (eq1, A, B) = MUX2(LUT20;LUT29);

lesso = LUT4_2B22;

LUT20 = gndX

LUT2A = I0

LUT2C = I1

LUT2F = vddX

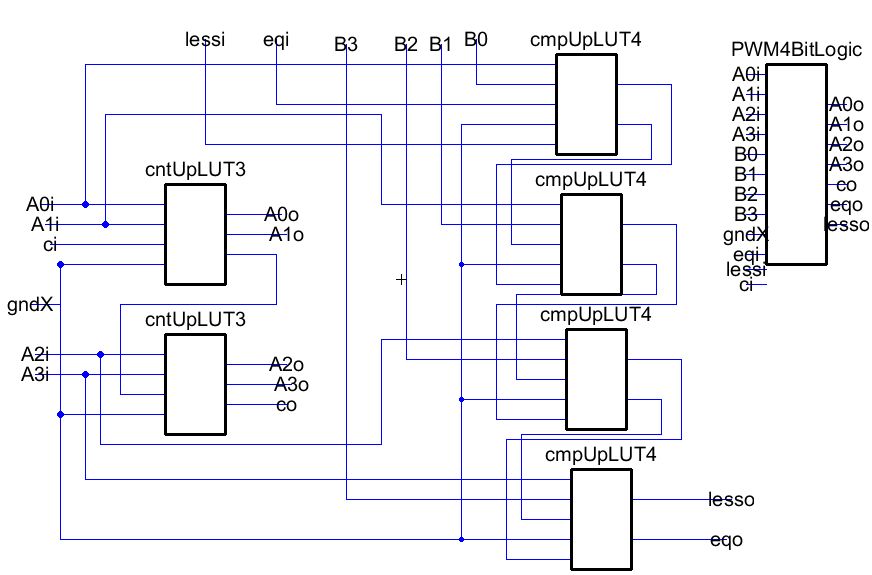

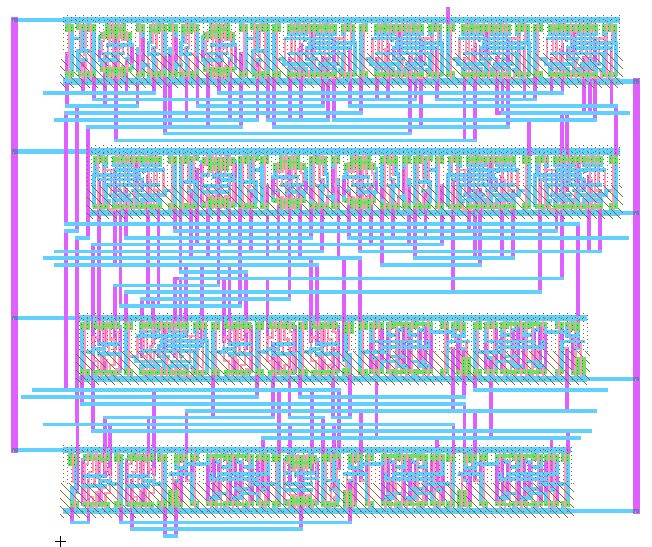

Count and compare schematic and layout

Load sclib

Silicon compiler LUT4_37E5

Do DRC check to make sure that there are no errors

Preferences, Technology, Technology, check Alternative active and poly contact rules

Create new library: PWM

Create cell schematic cntUpLUT3, cmpUpLUT4 and connect

Component, Misc, Library: sclib, MUX2{ic} New Instance

Use extra signal gndX and vddX for 0 and F

Create View Make icon

Create cell schematic test_basic for simulation with cntUpLUT3, cmpUpLUT4

Silicon compiler LUT4_37E5

Do DRC check to make sure that there are no errors

Preferences, Technology, Technology, check Alternative active and poly contact rules

Create new library: PWM

Create cell schematic cntUpLUT3, cmpUpLUT4 and connect

Component, Misc, Library: sclib, MUX2{ic} New Instance

Use extra signal gndX and vddX for 0 and F

Create View Make icon

Create cell schematic test_basic for simulation with cntUpLUT3, cmpUpLUT4

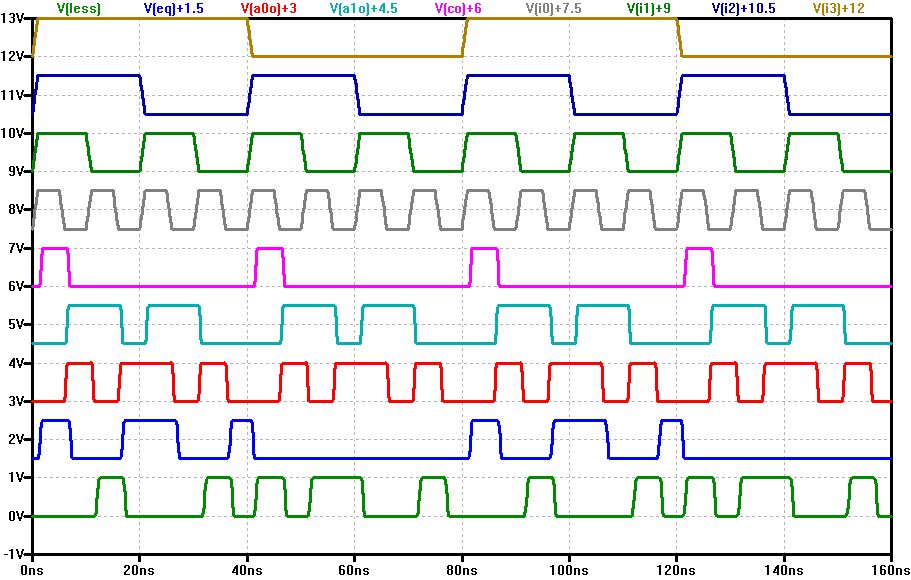

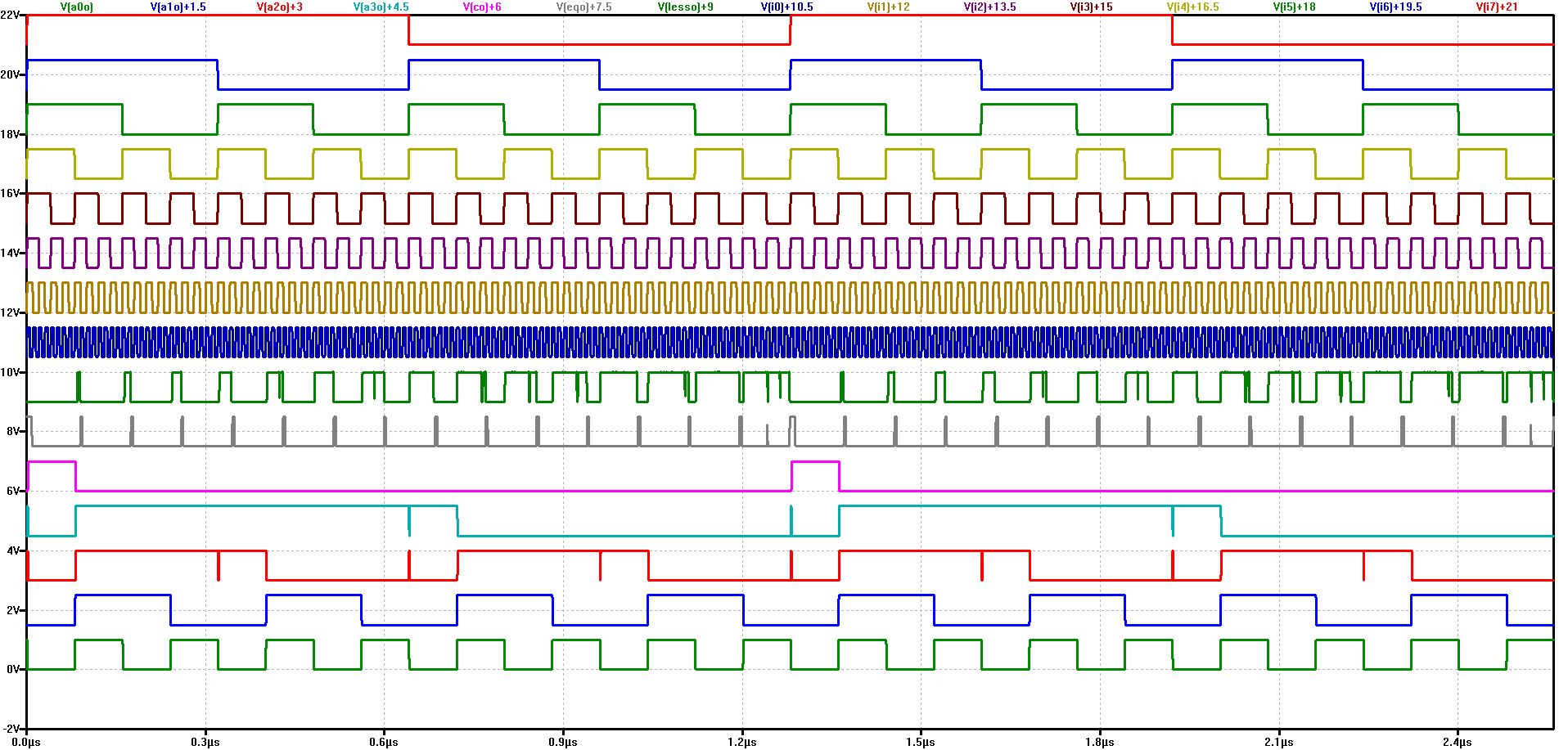

count and compare simulation

Each column in the simulation of a

combination I0..I3 is one row in the truth table.

The first column from 0..10ns is for the input "1111".

The first column from 0..10ns is for the input "1111".

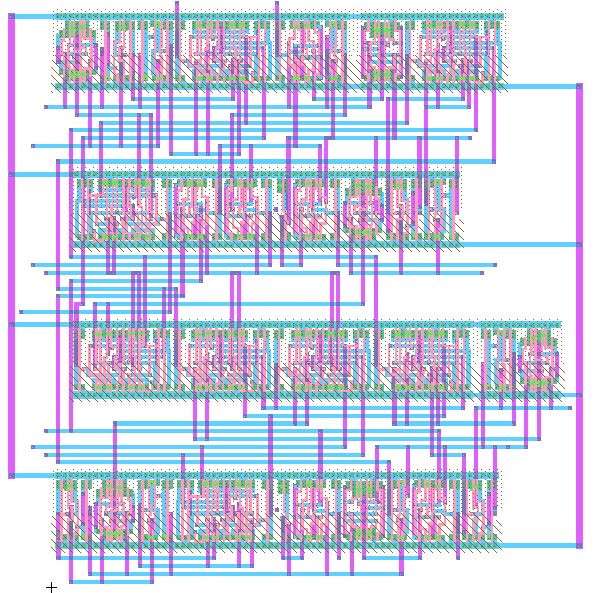

4 Bit count and compare schematic and layout

rows length width

4 737 x 747 = 550539

3 921 x 584 = 537864

2 1257 x 462 = 580734

4 737 x 747 = 550539

3 921 x 584 = 537864

2 1257 x 462 = 580734

4 Bit count and compare logic schematic and layout

rows length width

4 737 x 747 = 550539

3 921 x 584 = 537864

2 1257 x 462 = 580734

Bigger tables

4 841 x 857 = 720737

4 737 x 747 = 550539

3 921 x 584 = 537864

2 1257 x 462 = 580734

Bigger tables

4 841 x 857 = 720737

4 Bit count and compare logic simulation

.include cmosedu_models.txt .global VDD VDD VDD 0 DC 1 VGNDX GNDX 0 DC 0 VDDX VDDX 0 DC 1 V8 I8 0 PULSE(0 1 0 1n 1n 1279n 2560n) V7 I7 0 PULSE(0 1 0 1n 1n 639n 1280n) V6 I6 0 PULSE(0 1 0 1n 1n 319n 640n) V5 I5 0 PULSE(0 1 0 1n 1n 159n 320n) V4 I4 0 PULSE(0 1 0 1n 1n 79n 160n) V3 I3 0 PULSE(0 1 0 1n 1n 39n 80n) V2 I2 0 PULSE(0 1 0 1n 1n 19n 40n) V1 I1 0 PULSE(0 1 0 1n 1n 9n 20n) V0 I0 0 PULSE(0 1 0 1n 1n 4n 10n) .tran 2560n

The columns are compared with the truth table. The results match. Verification is successful.

Delay

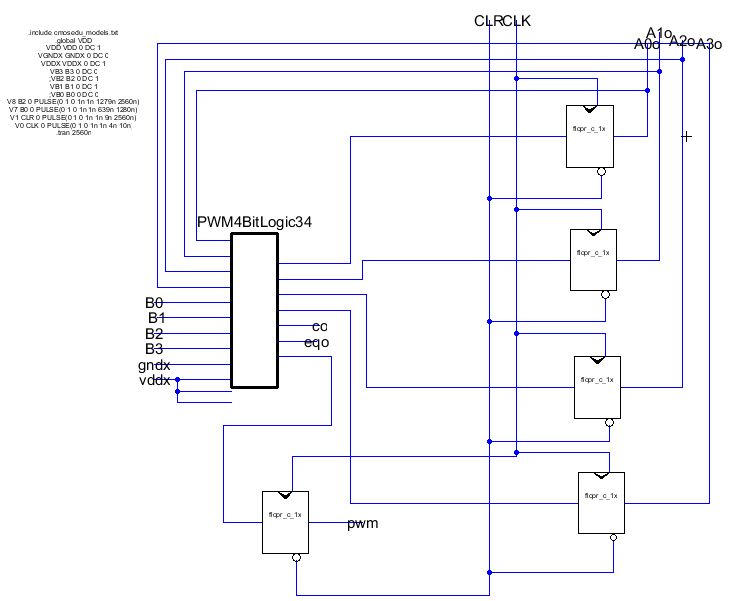

4 Bit PWM schematic

Adding FDC registers for counting and pwm buffer gives 'PWM4Bit'

Inputs: CLK, CLR, B3..B0, gndX, vddX

B3..B0 determines the width of the high pulse

Outputs: A3..A0, pwm (lesso), eqo, co

Adding Ci instead of connection to vddX and eqi, lessi instead of connection to vddX would make this module scalable.

B3..B0 determines the width of the high pulse

Outputs: A3..A0, pwm (lesso), eqo, co

Adding Ci instead of connection to vddX and eqi, lessi instead of connection to vddX would make this module scalable.

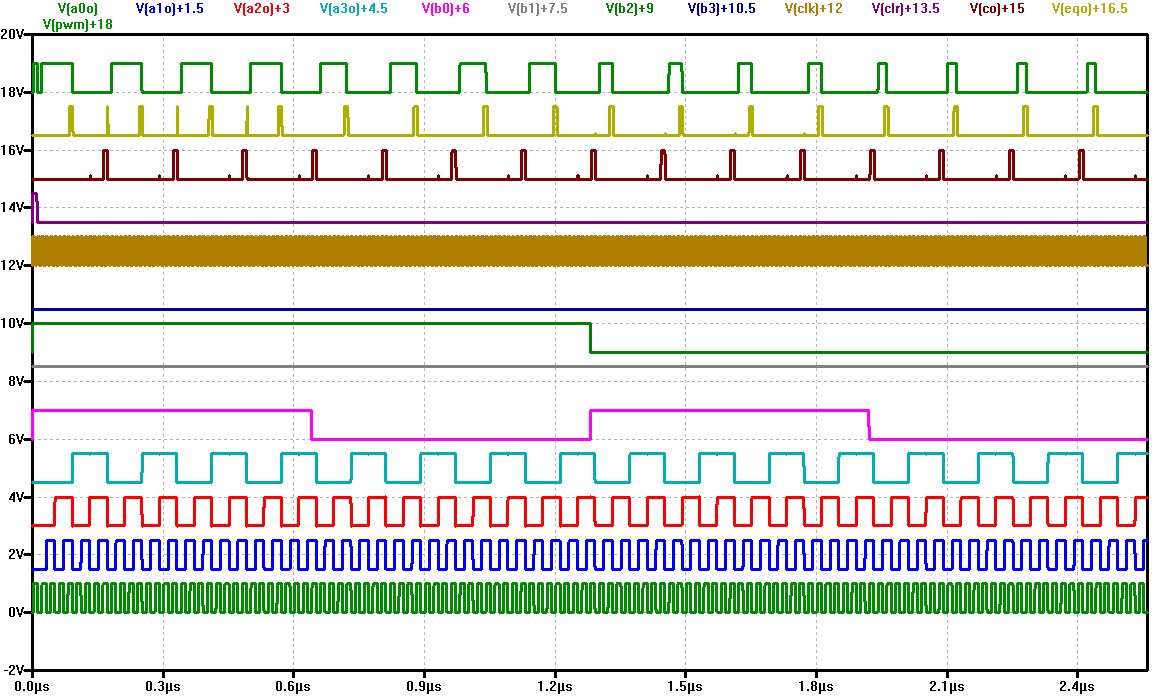

4 Bit PWM Simulation

The upper trace shows the PWM signal for different setting B0, B2

Simulation commands

.include cmosedu_models.txt .global VDD VDD VDD 0 DC 1 VGNDX GNDX 0 DC 0 VDDX VDDX 0 DC 1 VB3 B3 0 DC 0 ;VB2 B2 0 DC 1 VB1 B1 0 DC 1 ;VB0 B0 0 DC 0 V8 B2 0 PULSE(0 1 0 1n 1n 1279n 2560n) V7 B0 0 PULSE(0 1 0 1n 1n 639n 1280n) V1 CLR 0 PULSE(0 1 0 1n 1n 9n 2560n) V0 CLK 0 PULSE(0 1 0 1n 1n 4n 10n) .tran 2560n

4 Bit PWM layout

Area rows length width

Area 4 rows 921 x 779 = 717459

Area 5 rows 840 x 921 = 773640

Area 3 rows 1216 x 625 = 760000

Power: VDD, GND, vddX, gndX

Input: CLK, CLR, B3..B0

Output: A3..A0, co, eqo, pwm

Area 4 rows 921 x 779 = 717459

Area 5 rows 840 x 921 = 773640

Area 3 rows 1216 x 625 = 760000

Power: VDD, GND, vddX, gndX

Input: CLK, CLR, B3..B0

Output: A3..A0, co, eqo, pwm

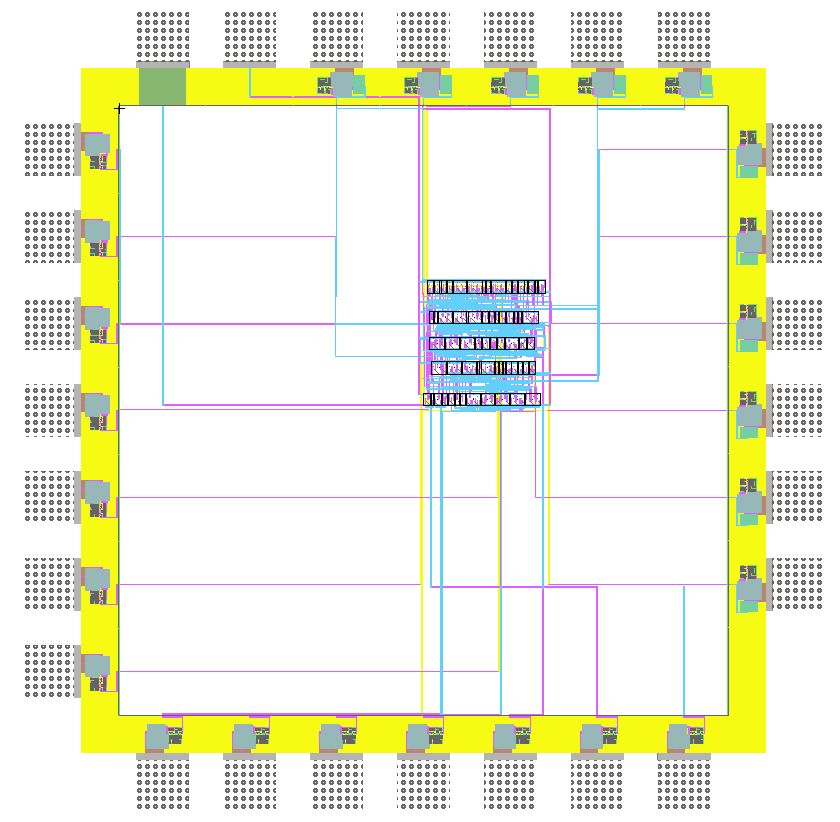

4 Bit PWM layout with Padframe

Adding Padframe to serial to gray code converter

Adding Pad Frame

Use and load the library Pads4u.jelib.

Keep multiplier as the "Current Library".

Download file padsMultiplier2x2.arr and save it to your local directory.

Modify the file according to the inputs and outputs.

Insert in the line core your top level circuit layout name.

Names are case sensitiv.

Try to make a square pad frame:

Tools - Generation - Pad Frame Generator: select file padsMultiplier2x2.arr

Tools - Routing - Sea of Gates Route

Conclusion and Outlook

Conclusion

- Truth tables where implemented with LUTs

- Verification for each subcircuit after each step and the final circuit was done with simulation

- Registers with clear signal (CLR) were implemented

- Successful synthesis for layout was done

Outlook: Your task

- Design, simulate and synthesize a 4-Bit PWM with

one different option per person:

cntUpLUT5, cntUpLUT6, cntDnLUT5, cntDnLUT6, cmpUpLut6, cmpDnLUT6, (cntDnLUT4, cmpDnLUT4)

Agree in the group (A, B, C, D, E) who is doing which option - Pick different settings for high time (position) and simulate your schematic and layout design

- Compare your design with the given design:

area, number of transistors, maximum delay - What is limiting a bigger PWM (6, 8, 10, 16 Bits)?

- Make a proposal what you would do to make a bigger PWM circuit

Discussion and Questions

Report 2..4 pages?

Submission time?

Research and Report Topics and Questions

Is it easier to write VHDL text than do a schematic?

Document challenges which were solved together.

Table of delay times and number of transistors, area per used sclib cell.

Delay comparison with source and load and without.

Would it be better to load register, count and compare to all0 or all1?

How does a register with option to preload a custom value look like?

How much area is transitors or cells and how much area is wiring?

Add preload count to count register and make modulo count with compare to 0, F.

Questions

- Which subcircuit are you doing?

cntUpLUT5, cntUpLUT6, cntDnLUT5, cntDnLUT6, cmpUpLut6, cmpDnLUT6, (cntDnLUT4, cmpDnLUT4) - With whom do you work together and compare your circuit?

- What is your plan for investigation?