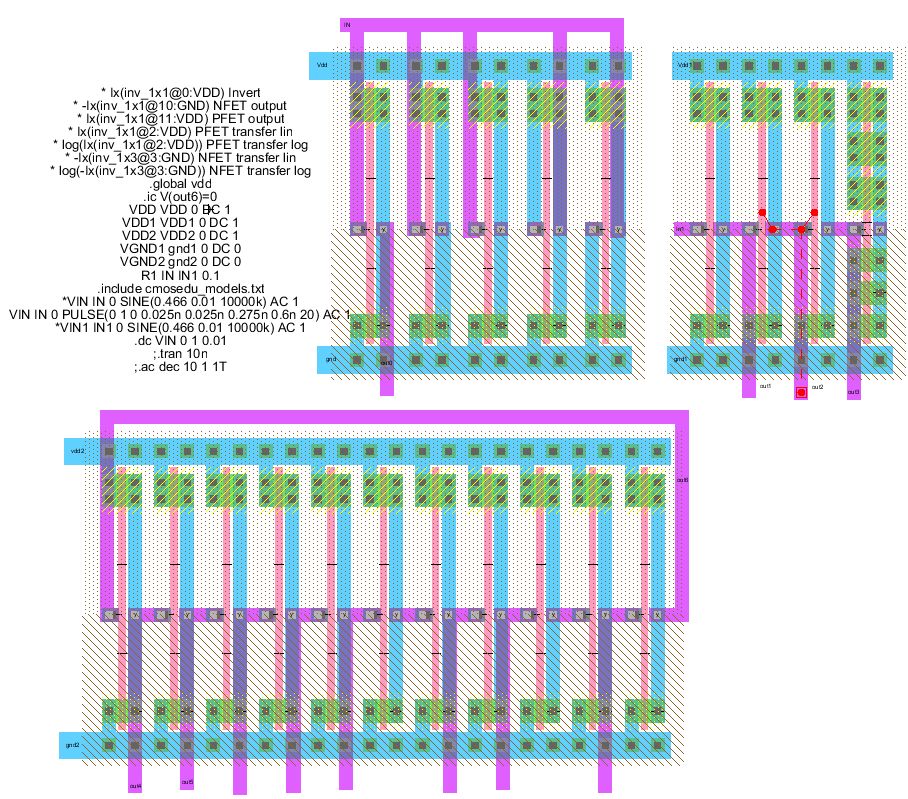

Performance Circuit: Inverter and Ring Oscillator

|

|

Library: Lab05_2024.jelib

Link: Lab05_2024.jelib

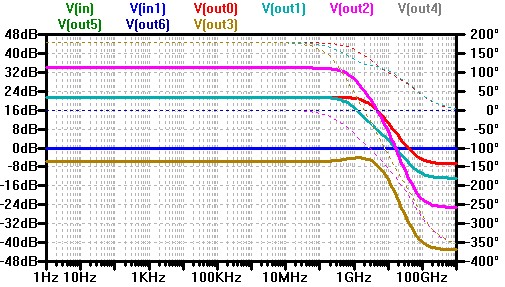

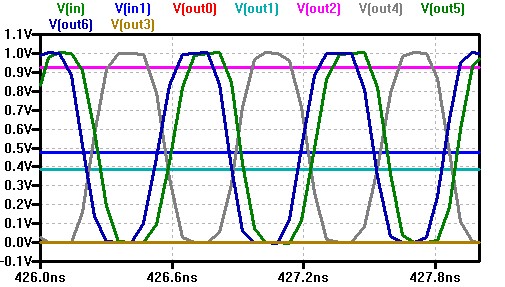

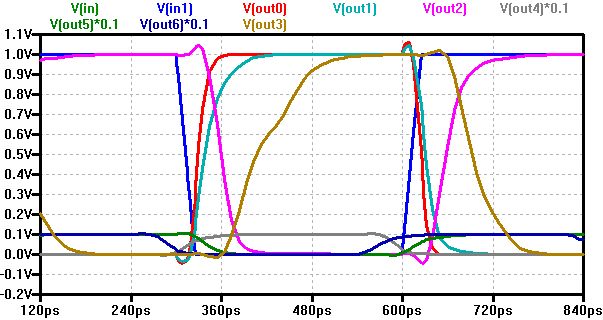

Cell: 'Performance' for .AC and .TRAN ring oscillator and delay simulation

Cell: 'PerformanceDC' for .DC simulation

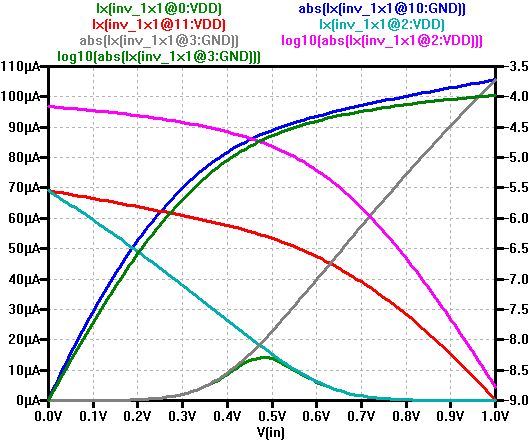

- Static IV output curves with an Inverter

VDDmax, IDSN, IDSP, λ - Inverter chain

- Ring oscillator

- Variation of number of unit transistor: mN, mP, sN, sP

m number of transistors in parallel (LTSPICE parameter)

s number of transistors in series - Simulate the circuits, extract parameters and modify WN, WP for optimum performance

Electrical parameters: VDDmax, (IDSmax), Ioff, Ron, Cox

Performance parameters: tdelay, fCLKmax, gain, ft

Most of the time MOSFETs are not available for measurement, therefore an inverter is used.

The input is fixed at VDD or gnd. With a load NFET or PFET current is measured for the output curve.

The inverter Vout, Iout versus Vin curve gives the threshold voltage Vthn, Vthp and the β (KP, KN).

An Inverter chain gives the propagation delay per stage.

t = 0.7 * R * C

The average power consumption for full charging should be:

Pavg = V * I = V * C * V * f

Changing the load 1,2,3 inverters, changes C while keeping R constant.