Microelectronics03 MOSFETProf. Dr. J—rg Vollrath02 History |

|

Video of lecture 03 MOSFET, SPICE models, propagation delay 31.03.2021

|

Lðnge: 01:26:05 |

0:0:0 0 0:3:9 Goals today 0:6:36 Output and transfer curve 0:9:48 50 nm technology voltage limit 0:14:58 Subthreshold characteristic 0:16:49 Bulk source voltage and threshold voltage 0:19:25 Design by selecting W or number of unit transistors 0:24:29 MOSFET typical layout and rules 0:30:37 SPICE models 1 um, 50 nm 0:35:39 Infineon 130 nm MOSFET transistor parameters 0:40:29 SPICE models details 0:48:31 MOSFET as switch 0:50:39 Transistor RC model 0:52:39 Transistor Capacitances 0:59:19 Propagation delay 1:1:39 Rising and falling output 1:8:49 equivalent capacitance, Miller capacitance 1:16:49 Timing closure |

Overview

- Moores Law

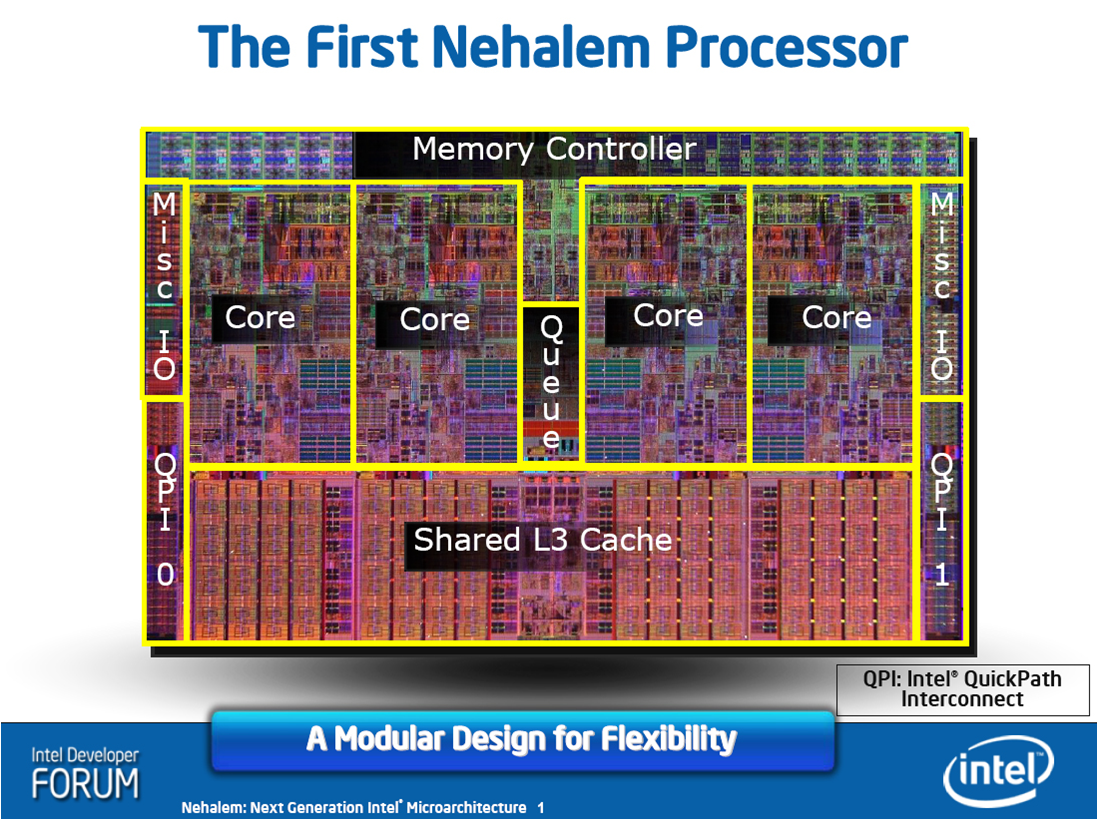

- Microelectronic products, complexity, hierarchy

- Technologies: ASIC, FPGA, Microcontroller

- You have a basic understanding of a MOSFET

- Gate, Source, Drain, Bulk/Well: VGS, VDS, VBS

- Threshold voltage Vth, Drain source current IDS

- Transfer and output IV curve

- Output resistance RDSon

- Layout: Width, Length

- Capacitance and RDSon,C delay

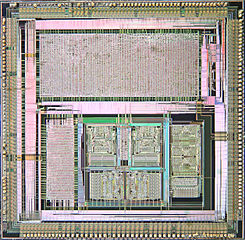

Microelectronic products

Computer |

mobile phone | ||||

Consumer |

Automotive |

Industrial | |||

Hierarchical Description

| Top Down | System Subsystemi, Subsystemj Subsystemk, Subsysteml |

Bottom up |

Find one solution and then optimize

Citations

Optimization

The First Rule of Program Optimization: Don't do it.

The Second Rule of Program Optimization (for experts only!): Don't do it yet.

- Michael A. Jackson

Find a solution first

Diagnose problems

We should forget about small efficiencies, say about 97% of the time:

premature optimization is the root of all evil.

Yet we should not pass up our opportunities in that critical 3%.

A good programmer will not be lulled into complacency by such reasoning,

he will be wise to look carefully at the critical code;

but only after that code has been identified

- Donald Knuth

Identify the problem through test first

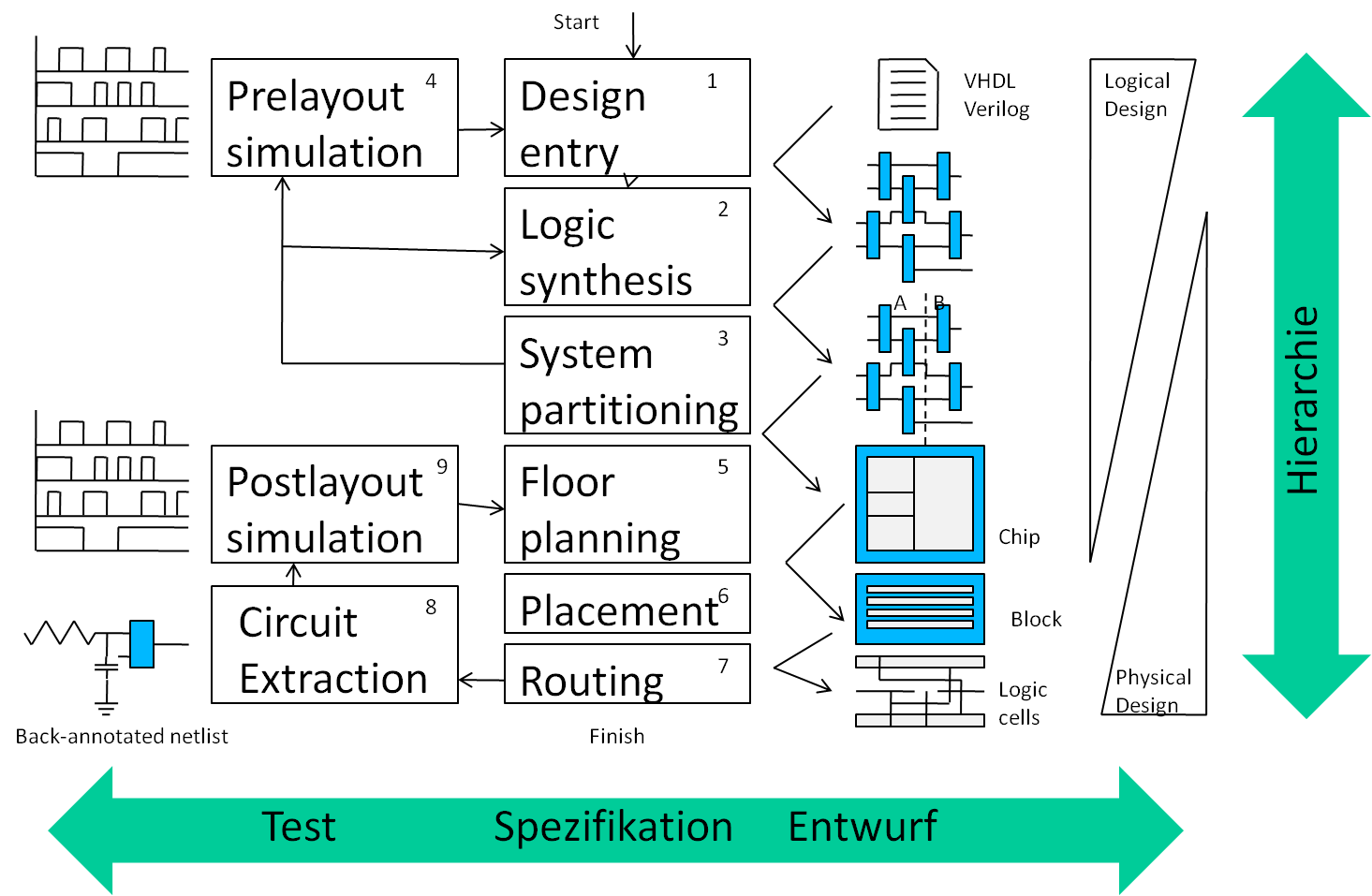

Design Flow

Technologies

ASIC: Application specific integrated circuit.

FPGA: File programmable gate array.

FPGA: File programmable gate array.

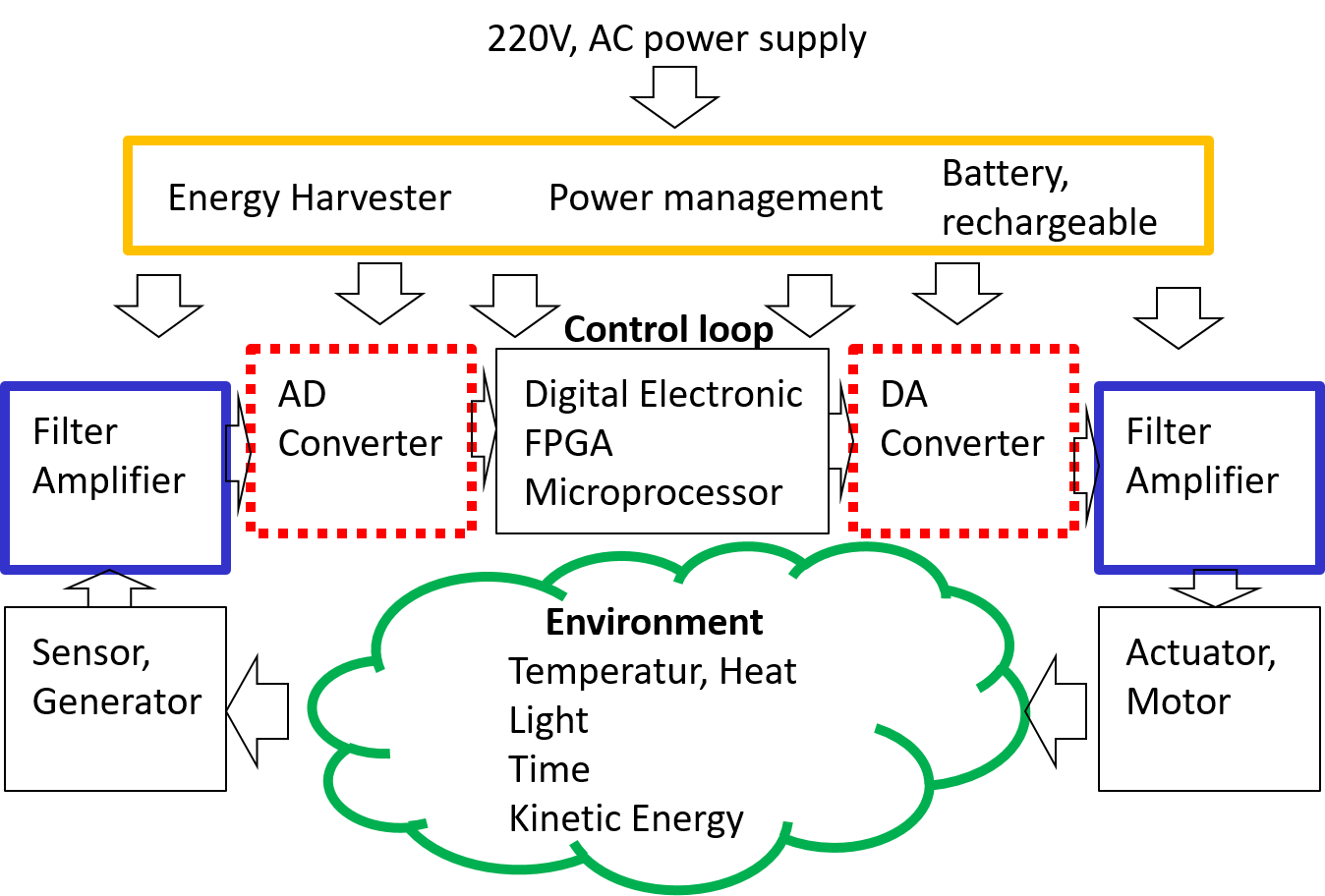

Systems (1)

Matlab, Labview can support some platforms.

Systems (2)

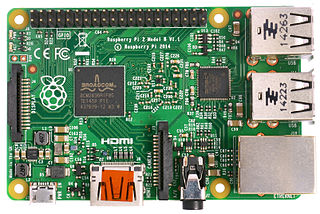

Zedboard: FPGA, µCField programmable gate array (FPGA)FPGA programming: VHDL, Verilog, IP Wizard Optional operating system: Linux Communication: Wifi, Webserver C(++), JavaScript Application: C(++), JavaScript |

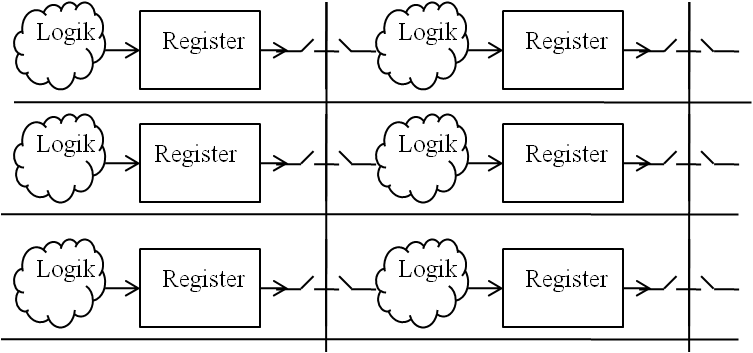

Switch matrix, logic and registers, programmable |

ASICProprietory software for design Electronic design automation (EDA) software tools: linux, perl, phyton, JavaScript |

Full custom ASIC Standard cell ASIC Gate Array Based Asic Foundries: TSMC, UMC Educational: MOSIS Europractice Zero To ASIC |

Matlab, Labview can support some platforms.

Microelectronics

Bottom up

MOSFET transistors, performance, layout and standard cells

NAND, AOI logic, scan flip flop

Place and route with VHDL

Make a chip with IOs, circuit and test structures

Electronic system

System Description

Modelling Simulation Structural Description Behavioral Description |

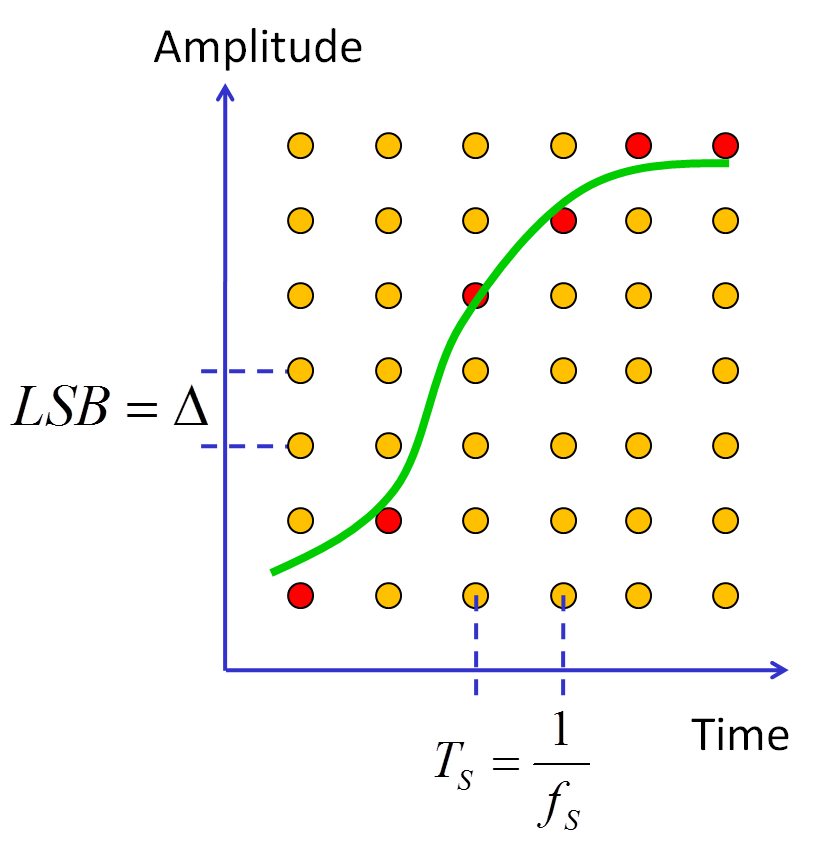

Analog and digital signals

|

MOSFET Transistor

- Equations:

- Technology versus electrical properties

- Electrical properties for circuit simulation (SPICE program)

- 4 Terminal device

- Gate, source, drain, bulk (well)

- Voltage: VGS gate source voltage, VDS drain source voltage, VBS bulk source voltage

- Current: Gate, Drain source, bulk or substrate

- Electrical Characteristics

- Transfer Curve:

- lin IDS versus VGS -> shows threshold voltage

- log IDS versus VGS -> shows weak inversion and off current

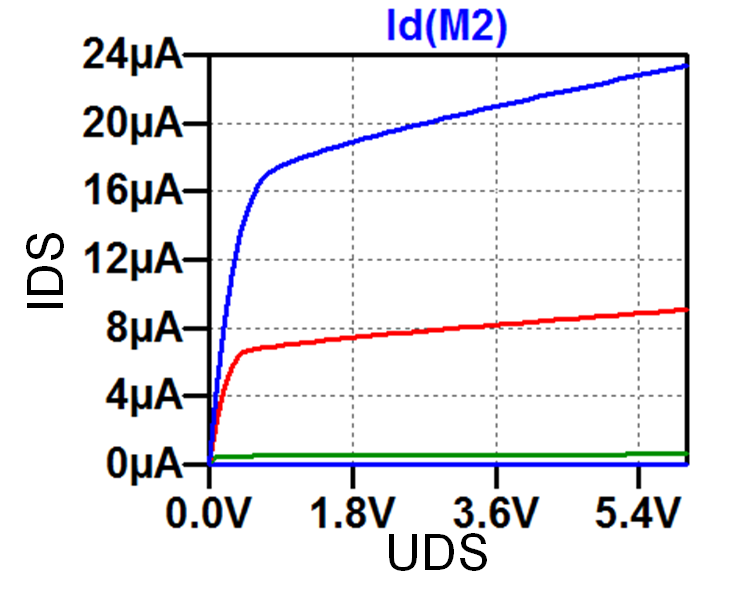

- Output Curve: IDS versus VDS with various VGS -> shows output conductance

- Technology versus Electrical Characteristics: Roll of curve -> Vth versus Leff

Transistor Evolution

Summary Transistor Evolution

MOSFET- transistorMoores law

Implications of reduced feature size:

30% Productivity gain per year

Power consumption, complexity/features, price

Hierarchical Design

Verification

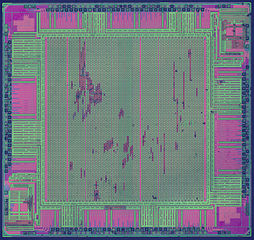

Microelectronics deals with small electronic components

Transistor, diode, resistor, capacitor, inductance

Microelectronic systems are getting cheaper

Complex systems can be realized

Functions are getting cheaper

Typical microelectronic components of interest are:

Microcontroller (Microprocessor, memory, digital and analog functions)

FPGA (Field programmable gate arrays)

ASIC (Application specific integrated circuits)

This class shows how to design digital and analog CMOS microelectronic components and systems

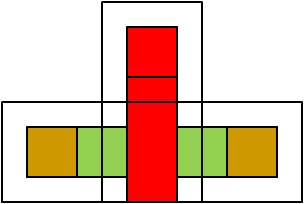

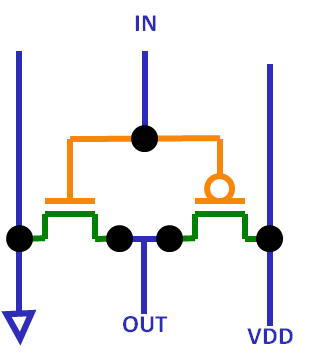

Inverter schematic and layout

|

|

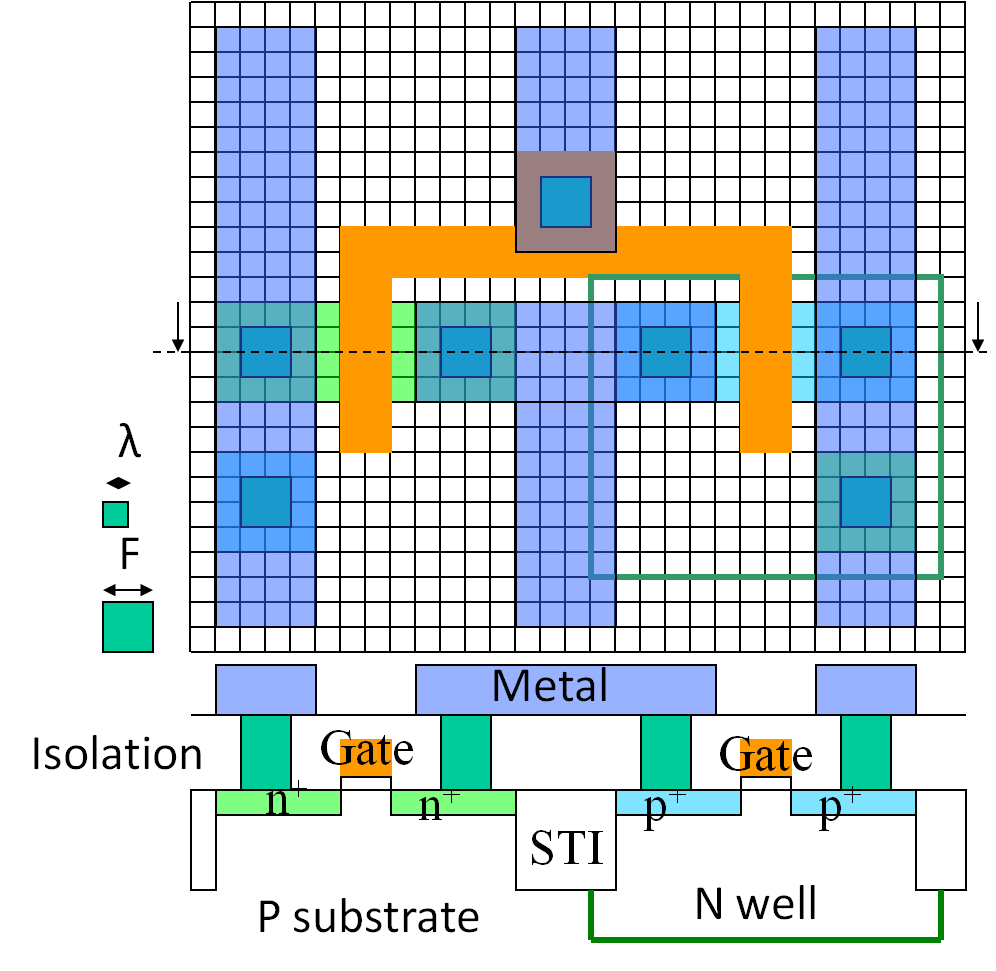

Schematic and layout are representing an inverter.

An inverter uses a NMOSFET and a PMOSFET.

The schematic shows the components and connections.

The layout has added different colors for different layers of the manufacturing process and each component.

These colors are transferred into the schematic showing the relationship between layout and schematic.

Wiring and transistor gates and diffusion have a minimum physical size of width and length of F.

There are also minimum distances required to prevent shorts.

It is difficult to automatically transform one view into the other.

A schematic is drawn to be able to easily understand the circuit. On the left is GND, on the right VDD, on the top inputs, on the bottom outputs.

In a schematic connection between 2 pins can be accomplished by labeling the pins with the same names. Lines can cross without resulting in short circuits.

A layout is drawn for symmetric and regular patterns, avoiding signal cross coupling and shape distortion, and having minimum size.

An inverter uses a NMOSFET and a PMOSFET.

The schematic shows the components and connections.

The layout has added different colors for different layers of the manufacturing process and each component.

These colors are transferred into the schematic showing the relationship between layout and schematic.

Wiring and transistor gates and diffusion have a minimum physical size of width and length of F.

There are also minimum distances required to prevent shorts.

It is difficult to automatically transform one view into the other.

A schematic is drawn to be able to easily understand the circuit. On the left is GND, on the right VDD, on the top inputs, on the bottom outputs.

In a schematic connection between 2 pins can be accomplished by labeling the pins with the same names. Lines can cross without resulting in short circuits.

A layout is drawn for symmetric and regular patterns, avoiding signal cross coupling and shape distortion, and having minimum size.

Equations of a n-channel MOSFET

|

\( I_{DS}= \cases{

\begin{matrix}

0 & \text{for} & V_{GS} \leq V_{th} & \text{Off}

\\

I_{on} exp^{\frac{ V_{GS}-V_{th} - \frac{kT}{e}}{\frac{kT}{e}}} \left( 1+\lambda V_{DS} \right)

& \text{for} & 0 \leq V_{GS} - V_{th} \lt \frac{kT}{e} & \text{Weak inversion}

\\

\beta \left( V_{GS}-V_{th} \right)^2 \left( 1+\lambda V_{DS} \right)

& \text{f■r} & \frac{kT}{e} \leq V_{GS} - V_{th} \lt V_{DS} & \text{Saturation}

\\

\beta \left( 2 \left( V_{GS}-V_{th} \right) V_{DS} - V_{DS}^2 \right)

& \text{for} & \frac{kT}{e} \leq V_{GS} - V_{th} \geq V_{DS} & \text{Linear}

\end{matrix}

}

\) \( \beta = \frac{\mu_n \epsilon_{ox}}{2d_{ox}} \frac{W}{L} = \frac{1}{2} \mu_n C_{ox}^{'} \frac{W}{L} = \frac{1}{2} K_{n}^{'} \frac{W}{L} = \frac{1}{2} K_{n} \) |

Quelle Vollrath

Quelle Vollrath |

Quelle Vollrath

Quelle Vollrath |

Draw a IDS(VGS) and IDS(VDS) curve with Vth = 1V (0.3V), Kn = 100 µAV-2 and λ = 0.02 V-1

Vth threshold voltage

λ Output conductance

W width, L length

µ mobility

Cox = e /dox Gate oxide capacitance

Vt = kT/q (300K) = 0.0259 V

Simulation verifies first correct Vth and maximum current IDS at maximum voltage Vdd.

Then the input capacitance Cox is confirmed with AC simulation of a RC circuit having the MOSFET gate as capacitance C.

Microelectronic has only transistors as elements.

Design is done using transistors with choosing W and L.

MOS transistors are also used as capacitances, resistors, diodes and lateral bipolar transistors.

In sub 50nm processes FINFETs are used having a fixed L and W. These transistors are called unit transistors. Circuits are designed combining transistors in series or parallel to get the desired W/L ratio. This makes automated design easier.

Elektronik 3, 08 MOSFET

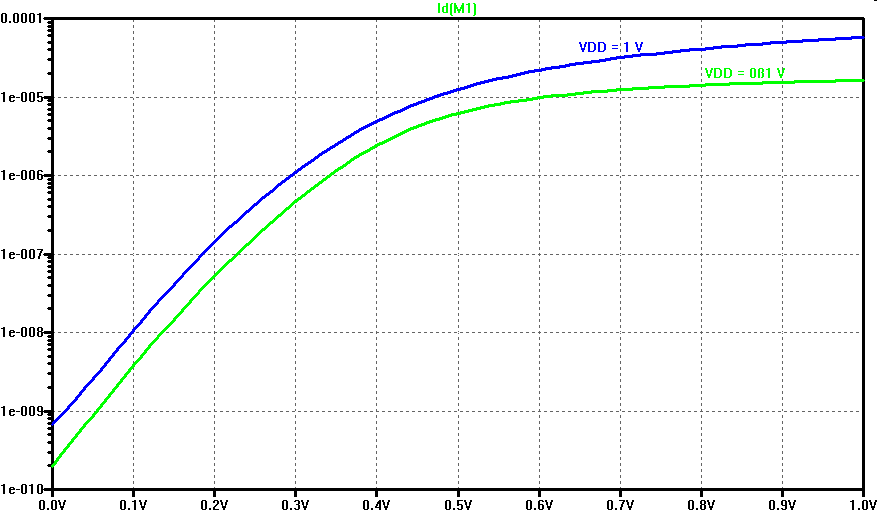

NFET Transistor subthreshold characteristic

|

MOSFET transistors can also be operated in the subthreshold region for low voltage power supply.

The graph shows an increase in current by a factor of 10 for 100 mV change in VGS.

Threshold voltage Vth

| \( V_{th}= V_{th0} + \left( \gamma \sqrt{V_{SB}+2\phi_F}-\sqrt{2\phi_F}\right) \) |

|

MOSFET Transistor design

- Choosing W and L for IDS

- L is fixed to minimum feature size

- W can be changed

- Unit transistors have a fixed W and L

Circuits are using unit transistors in parallel and series - Threshold voltage Vth

- Vth is fixed for a given process

- Vth can change with:

oxide thickness, doping, length and width - Modern processes have different devices:

High Vth, low Vth, thick and thin oxide devices

Check in simulation different Vth and W L variations

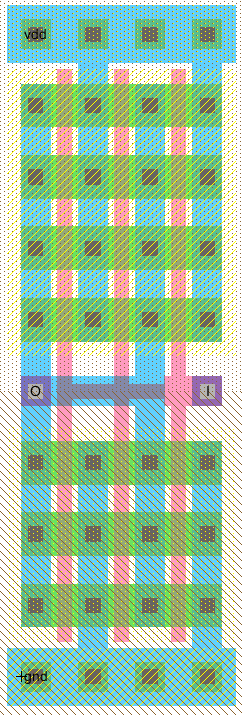

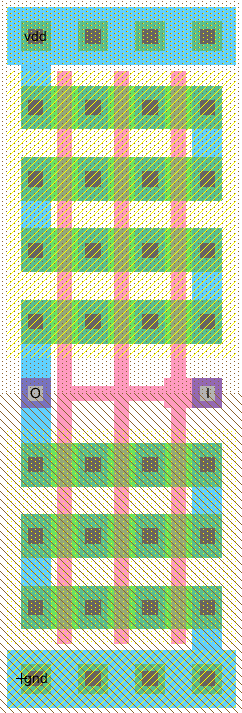

MOSFET layout

|

|

|

sclib.jelib: UNITExample{lay}, UNITLong{lay}

MOSFET SPICE models

| Long channel MOSFET F = 1 µm, VDD = 5 V | |||

| Parameter | NMOS | PMOS | Comment |

| VTh | 0.8 V | 0.9 V | Typical |

| KP | 120 µA/V2 | 40 µA/V2 | dox = 20 nm |

| C'ox | 1.75 fF/µm2 | 1.75 fF/µm2 | Cox = C'ox W L |

| λ | 0.01 V-1 | 0.0125 V-1 | L = 2 |

| R | 15 kΩ L/W | 45 kΩ L/W | |

| Short channel MOSFET F = 50 nm, VDD = 1 V | |||

| Parameter | NMOS | PMOS | Comment |

| VTh | 0.28 V | 0.28 V | Typical |

| KP | 60 µA/V2 | 30 µA/V2 | dox = 1.4 nm |

| C'ox | 25 fF/µm2 | 25 fF/µm2 | Cox = C'ox WL |

| λ | 0.6 V-1 | 0.3 V-1 | L = 2 |

| R | 34 kΩ/W | 68 kΩ/W | |

Propagation delay can be calculated with tPD = 0.7 · R · C

R is the resistance of NFET or PFET. C is the sum of the output capacitance (Coxn) and input capacitance (3/2 Cox).

C = (3/2 + 1 ) (Coxn + Coxp)

A 1 µm unit transistor has a Cox of 1.75 fF/µm2 and R of 15 kΩ (45 kΩ).

tPD = 0.7 · 2 · 1.75 fF · 0.5 · ( 15 kΩ + 45 kΩ) = 73.5 ps

A 50 nm unit transistor has a Cox of 25 fF/µm2 · 50nm · 50 nm = 62.5 aF and R of 34 kΩ (68 kΩ).

tPD = 0.7 · 2 · 25 fF/µm2 · 50 nm · 50 nm · 0.5 · ( 34 kΩ + 68 kΩ) = 2.23 ps

Simulated inverter 24..32 ps

More models:

Baker: 1 µm MOSFET model, 50 nm MOSFET model, cmosedu_models.txt

Sedra Smith Level=1 5 µm, 0.5 µm: sedra_lib.lib

Allen, Holberg Level=3 0.8 µm: Holberg.txt

TSMC 0.25um CMOS MOSFETs (level 3) t14y_tsmc_025_level3.lib from MOSIS .

TSMC 0.18um CMOS MOSFETs (level 3) t92y_mm_non_epi_thk_mtl-params_TSMC_018.txt from MOSIS .

180nm CMOS Model

130nm CMOS Model

Archived PTM CMOS models 7nm, 10nm, 14nm, 16nm, 20nm, 22nm, 32nm, 45nm, 65nm, 90nm, 130nm, 180nm

.model CD4007P PMOS(LEVEL=1 KP=500u VT0=-1 LAMBDA=0.002 CGSO=45n CGBO=2n CGDO=45n)

.model ALD1107P PMOS(LEVEL=1 KP=0.2m VT0=-0.7 LAMBDA=0.018 CGDO=100n CGSO=100n)

R is the resistance of NFET or PFET. C is the sum of the output capacitance (Coxn) and input capacitance (3/2 Cox).

C = (3/2 + 1 ) (Coxn + Coxp)

A 1 µm unit transistor has a Cox of 1.75 fF/µm2 and R of 15 kΩ (45 kΩ).

tPD = 0.7 · 2 · 1.75 fF · 0.5 · ( 15 kΩ + 45 kΩ) = 73.5 ps

A 50 nm unit transistor has a Cox of 25 fF/µm2 · 50nm · 50 nm = 62.5 aF and R of 34 kΩ (68 kΩ).

tPD = 0.7 · 2 · 25 fF/µm2 · 50 nm · 50 nm · 0.5 · ( 34 kΩ + 68 kΩ) = 2.23 ps

Simulated inverter 24..32 ps

More models:

Baker: 1 µm MOSFET model, 50 nm MOSFET model, cmosedu_models.txt

Sedra Smith Level=1 5 µm, 0.5 µm: sedra_lib.lib

Allen, Holberg Level=3 0.8 µm: Holberg.txt

TSMC 0.25um CMOS MOSFETs (level 3) t14y_tsmc_025_level3.lib from MOSIS .

TSMC 0.18um CMOS MOSFETs (level 3) t92y_mm_non_epi_thk_mtl-params_TSMC_018.txt from MOSIS .

180nm CMOS Model

130nm CMOS Model

Archived PTM CMOS models 7nm, 10nm, 14nm, 16nm, 20nm, 22nm, 32nm, 45nm, 65nm, 90nm, 130nm, 180nm

CD4007

.model CD4007N NMOS(LEVEL=1 KP=500u VT0=1 LAMBDA=0.002 CGSO=45n CGBO=2n CGDO=45n).model CD4007P PMOS(LEVEL=1 KP=500u VT0=-1 LAMBDA=0.002 CGSO=45n CGBO=2n CGDO=45n)

ALD1106, ALD1107

.model ALD1106N NMOS(LEVEL=1 KP=0.48m VT0=0.7 LAMBDA=0.018 CGDO=100n CGSO=100n).model ALD1107P PMOS(LEVEL=1 KP=0.2m VT0=-0.7 LAMBDA=0.018 CGDO=100n CGSO=100n)

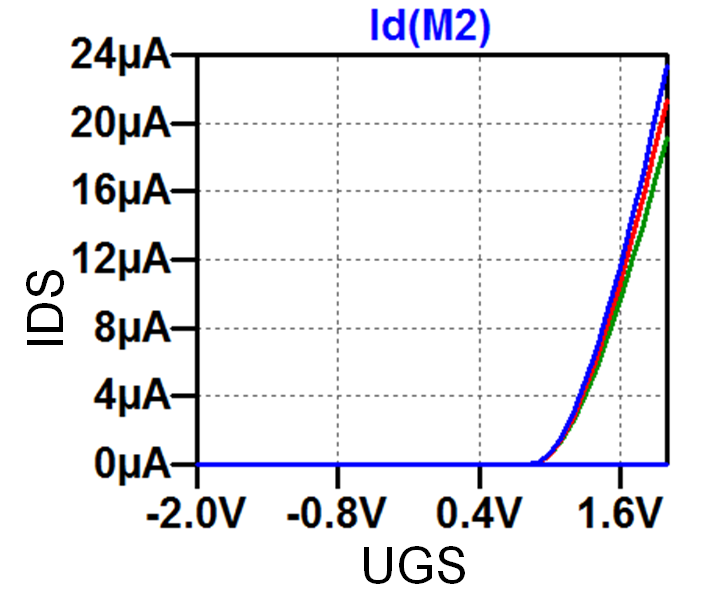

Detailed Transistor measurement

|

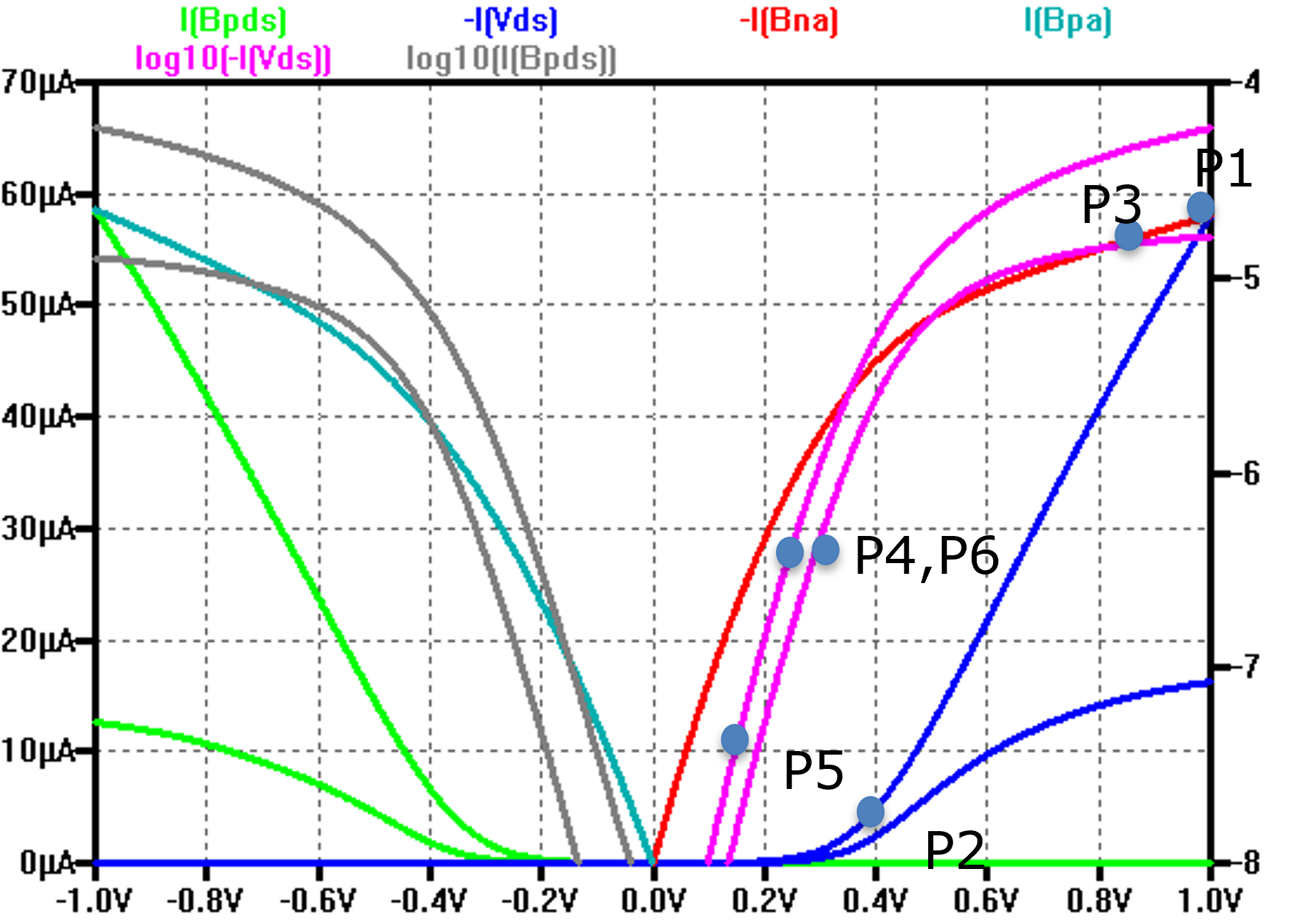

VDD LN=LP=F, WN = 2F, WP = 4F P1: Ion = IDSmax P1, P2: Vth, Rdson (KP) P1, P3: λ P4, P5: SS(mV/dec), Ioff P4, P6: DIBL(mV/V) |

|

The graph combines PFET and NFET characteristic in linear and logarithmic y scale.

Minimum dimensions are used as stated above.

Transistor parameters can be extracted using the points P1..P6.

For subthreshold slope (SS), drain induced barrier lowering (DIBL) and Ioff the logarithmic curves are analyzed. Logarithmic behaviour can be seen starting below Vth/2.

Ix = Ids(Vgs=Vthn*0.5/Vthp*0.7)

SS = V(Ix) - V(Ix/10)

DIBL = (V(Ix;VDSmin) - V(Ix;0.1*VDSmax))/0.9/VDSmax

Ioff = Ix * 10^(-Vth/2/SS)

An example simulation with measurement statements for 50nm technology (Baker) is given in CMOS_IV_50n.spi

Minimum dimensions are used as stated above.

Transistor parameters can be extracted using the points P1..P6.

For subthreshold slope (SS), drain induced barrier lowering (DIBL) and Ioff the logarithmic curves are analyzed. Logarithmic behaviour can be seen starting below Vth/2.

Ix = Ids(Vgs=Vthn*0.5/Vthp*0.7)

SS = V(Ix) - V(Ix/10)

DIBL = (V(Ix;VDSmin) - V(Ix;0.1*VDSmax))/0.9/VDSmax

Ioff = Ix * 10^(-Vth/2/SS)

An example simulation with measurement statements for 50nm technology (Baker) is given in CMOS_IV_50n.spi

*** SPICE deck for cell CMOS_IV{lay} from library Lab01_1u_Perf

** Microelectronics/LTSPICE/CMOS_IV_50n.spi

*** SUBCIRCUIT NFET_1u_IV FROM CELL NFET_1u_IV{lay}

.SUBCKT NFET_1u_IV VD VG VS VW

Mnmos@0 VS VG VD gnd N_50n L={F} W={Wx}

.ENDS NFET_1u_IV

*** WARNING: no power connection for P-transistor wells in cell

*'PFET_1u_IV{lay}'

*** SUBCIRCUIT PFET_1u_IV FROM CELL PFET_1u_IV{lay}

.SUBCKT PFET_1u_IV VD VG VN VS

Mpmos@0 VD VG VS VN P_50n L={F} W={Wxp}

.ENDS PFET_1u_IV

*** TOP LEVEL CELL: CMOS_IV{lay}

XNFET_1u_@0 VDS VNG GND GND NFET_1u_IV

XNFET_1u_@1 VNA VMAX GND GND NFET_1u_IV

XPFET_1u_@0 VPDS VPG VP VP PFET_1u_IV

XPFET_1u_@1 VPA VMIN VP VP PFET_1u_IV

* Spice Code nodes in cell cell 'CMOS_IV{lay}'

* I(Bpds) 0.0-I(Vds) 0.0-I(Bna) I(Bpa) log10(- I(Vds)) log10( I(Bpds))

.param F = 50n Wx = 100n Wxp = 200n

.param Vmax = 1 Vmin=-1.0*Vmax V10=0.1*Vmax V90=0.9*Vmax

VG VG 0 DC 0

VP VP 0 DC 0

VDS VDS 0 DC 0

VDD VDD 0 DC {Vmax}

BPDS VPDS 0 V=-V(VDS)

BPGS VPG 0 V=MIN(V(VG),0)

BNGS VNG 0 V=MAx(V(VG),0)

BNA VNA 0 V=MAX(V(VG),0)

VNB VMAX 0 DC {VMAX}

VPB VMIN 0 DC {VMin}

BPA VPA 0 V=MIN(V(VG),0)

.include cmosedu_models.txt

.dc VG {VMin} {VMAX} 1m VDS {V10} {VMAX} {V90}

* Extract transistor parameters Vtn Rnon lambdan

.measure DC INmax MAX -I(Vds)

.measure DC Vnx when -I(Vds)=Inmax/10

.measure DC Vtn PARAM Vnx-0.1/0.9*(Vmax-Vnx)

.measure DC Rnon PARAM (Vmax-Vtn)/INmax

.measure DC Vnx2 when -I(Bna) = 0.9*Inmax

.measure DC lambdan PARAM 0.1/0.9/(Vmax-Vnx2)

* Extract transistor parameters DIBL SS

.measure DC Ix FIND -I(Vds) WHEN V(VG)=Vtn*0.8

.measure DC Vnx3 when -I(Vds) = Ix/10

.measure DC SSn PARAM Vtn/2-Vnx3

* DIBL (Vnx3(step1) - Vnx3(step2))/0.9/Vmax

.measure DC Vnx4 when -I(Vds) = 10n

.measure DC Inoff PARAM Ix*(10**(-Vtn*0.8/SSn))

** PFET Parameter

.measure DC IPmax MAX I(Bpds)

.measure DC Vpx when I(Bpds)=IPmax/10

.measure DC Vtp PARAM Vpx+0.1/0.9*(Vmax-Vpx)

.measure DC Rpon PARAM (Vmax+Vtp)/IPmax

.measure DC Vpx2 when I(Bpa) = 0.9*IPmax

.measure DC lambdap PARAM 0.1/0.9/(Vmax+Vpx2)

* Extract transistor parameters DIBL SS

.measure DC Ipx FIND I(Bpds) WHEN V(VG)=Vtp*0.8

.measure DC Vpx3 when I(Bpds) = Ipx/10

.measure DC SSp PARAM Vtp/2+Vpx3

* DIBL (Vnx3(step1) - Vnx3(step2))/0.9/Vmax

.measure DC Vpx4 when I(Bpds) = 10n

.measure DC Ipoff PARAM Ipx*(10**(-Vtp*0.8/SSp))

.END

| NFET | L=F, WN=2F | L=F, WN=4F | L=2F, WN=4F |

| inmax = inon | 58uA | 121uA | 44uA |

| vtn | 0.35V | 0.35V | 0.39V |

| rnon | 11kOhm | 5.4kOhm | 13.8kOhm |

| lambdan | 0.308/V | 0.308/V | 0.231/V |

| ssn | 86mV/dec | 86mV/dec | 87mV/dec |

| DIBLn | 37mV/V | 37mV/V | 27mV/V |

| ioffn | 713pA | 1.5nA | 234pA |

| PFET | L=F, WP=4F | L=F, WP=8F | L=2F, WP=8F |

| Ipmax = Ipon | 53.6uA | 115uA | 38uA |

| Vtp | -0.25V | -0.25V | -0.29V |

| rpon | 14kOhm | 6.5kOhm | 18kOhm |

| lambdap | 0.437/V | 0.428/V | 0.242/V |

| ssp | 248mV/dec | 253mV/dec | 279mV/dec |

| DIBLp | 68mV/V | 79mV/V | 29mV/V |

| ipoff | 20.5nA | 44nA | 9.7nA |

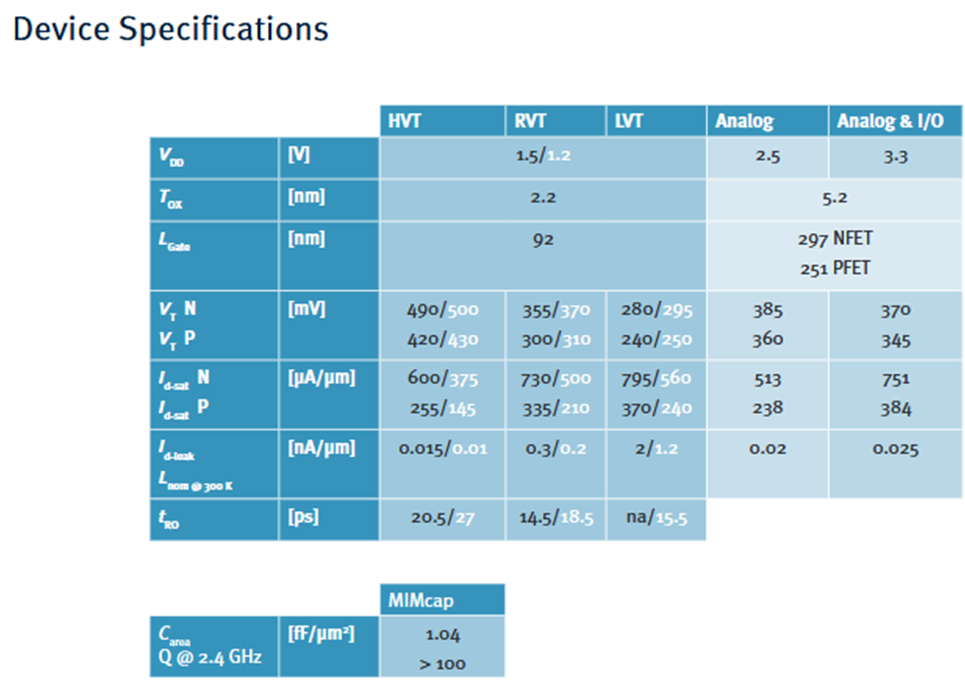

130 nm Infineon MOSFET transistors

Infineon 130 nm platform