Low cost serial DAC simulation, realization, error correction and characterization

Prof. Joerg Vollrath, 06.02.2022, University of Applied Science, Kempten, Germany, 2022Abstract

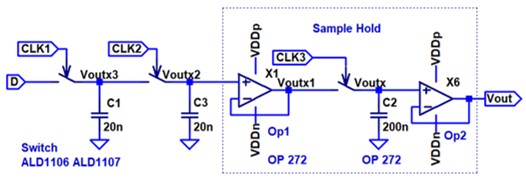

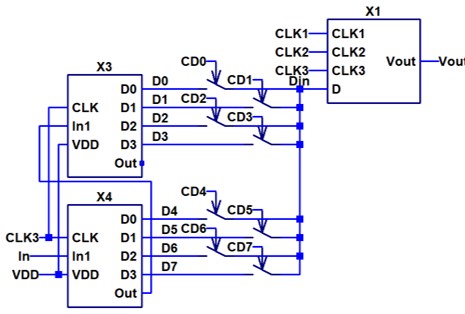

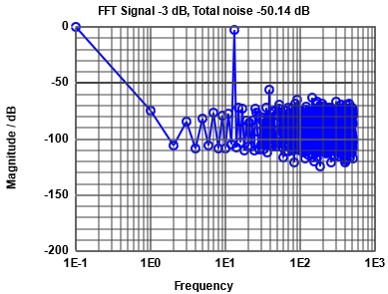

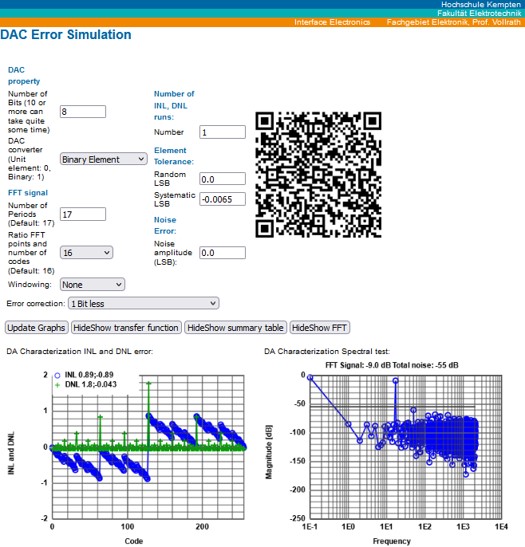

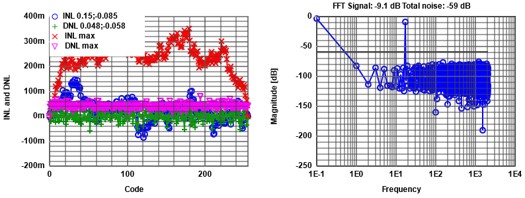

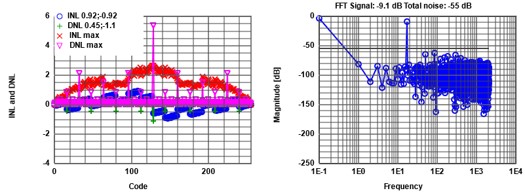

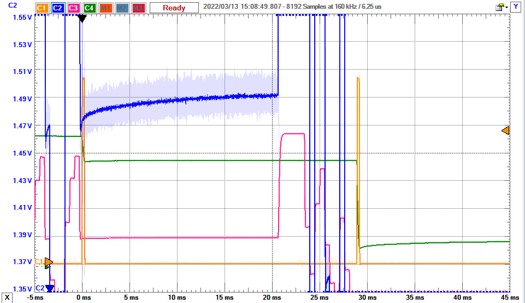

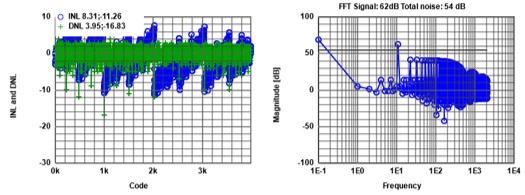

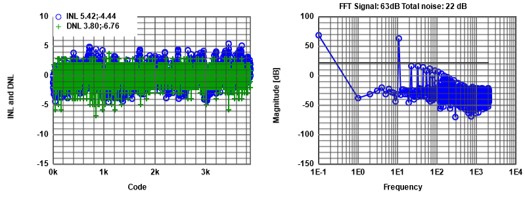

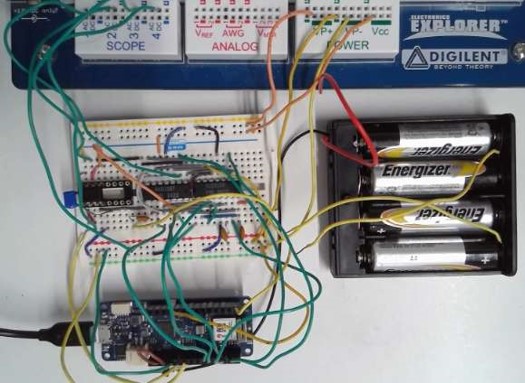

A serial C DAC has a minimum number of components. This structure makes it easy to simulate, realize, characterize and to study error correction. This paper presents a discrete 12 bit serial C DAC with digital error correction. Theory, high level (JavaScript), low level (LTSPICE) simulations, a real circuit and low cost measurements and error correction using an Arduino board are presented. Comparison of theory, simulation and measurement gives deeper understanding of DAC leading to better circuits and improved characterization methods. The measurements show INL, DNL below 4 and FFT with 46.5 dB SNQR which gives 6.5 ENOB at 33 Hz sampling frequency of a 12 bit DAC. Hardware cost are below 100 Euro without an oscilloscope for detailed signal measurements.Keywords - serial DAC, circuit simulation, characterization, INL, DNL, SNR, error correction