Digitaltechnik03 TransistorrealisierungProf. Dr.J÷rg Vollrath02 Logische Verkn³pfungen |

|

Ein kurze Videozusammenfassung der Vorlesung

|

Lõnge: 5:54 min |

0:00 Transistorrealisierung 0:13 CMOS Transistoren 1:30 Schaltererklõrung 2:16 Inverter 4:15 Physikalische Realisierung |

▄bungsaufgabe: Erstellung einer Wahrheitstabelle aus einer Transistorschaltung

|

Lõnge: 3:22 min |

0:00 Schaltungserlõuterung 0:38 Eingõnge, Ausgang 0:48 Wahrheitstabelle 1:19 A=0, B=0 1:40 A=0, B=1 02:04 A=1, B=0 2:23 A=1, B=1 2:45 Schaltfunktion |

Wiederholung und Heute

- Darstellungsarten

- Gleichung, Schaltsymbol, Wahrheitstabelle, VHDL (Textuell)

- Boolsche Algebra und Grundverkn³pfungen

- UND, ODER, NICHT, NAND, NOR

- Schaltungstechnische Darstellung von Signalen:

CMOS Technologie, MOS-Transistoren, Schalter - Inverter

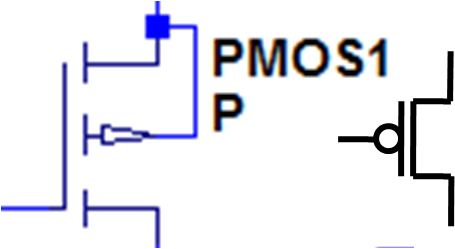

CMOS Transistoren als Schalter

| Symbol | Eingang: Gate | |||

PFET Transistor:

|

| 0

| 1

| |

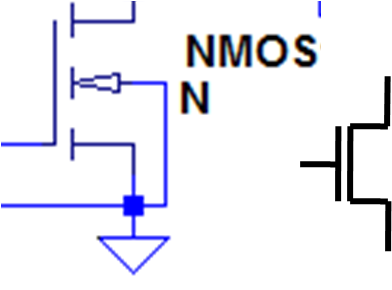

NFET Transistor:

|

| 0

| 1

| |

Zur Realisierung von booleschen Funktionen werden MOSFET (metal oxide semiconductor field effect transistor)

Transistoren eingesetzt.

Dabei werden Halbleiter (semiconductor, Silizium) verwendet, bei denen man durch Einbringen von Femdatomen (Dotierung) die Leitfõhigkeit (Elektronen, L÷cher) verõndern kann.

Der MOS Transistor hat drei Anschl³sse Gate, Drain und Source.

Das Gate ist der Eingang. An der Drain ist der Ausgang und an der Source ist VDD (Betriebsspannnung, PFET) oder GND (0 V, NFET).

FET Feldeffekttransistor ist der ▄berbegriff f³r Halbleiterbaulemente, bei denen das elektrische Feld zwischen Gate und Kanal den Kanalwiderstand steuert bzw die Verbindung zwischen Drain und Source trennt oder schliesst.

Es gibt PFETs (PMOSFETs, L÷cherleitung, positive Ladungstrõger, L÷cher) und NFETs (NMOSFETs, negative Ladungstrõger, Elektronen) deren Verhalten komplementõr sind (complementary metal oxide semiconductors, CMOS).

Ist die Gatesourcespannung beim NFET positiv, gr÷▀er als eine Schwellspannung (threshold voltage), wird die Verbindung zwischen Drain und Source leitend (Ein Schalter wird geschlossen).

Ist die Gatesourcespannung beim PFET negativ, kleiner als eine Schwellspannung, wird die Verbindung zwischen Drain und Source leitend (Ein Schalter wird geschlossen).

Durch geschicktes Kombinieren der Transistoren k÷nnen Logikfunktionen technisch realisiert werden.

Fast alle modernen Mikroprozessoren und digitalen Schaltungen werden mit CMOS Transistoren realisiert.

Dabei werden Halbleiter (semiconductor, Silizium) verwendet, bei denen man durch Einbringen von Femdatomen (Dotierung) die Leitfõhigkeit (Elektronen, L÷cher) verõndern kann.

Der MOS Transistor hat drei Anschl³sse Gate, Drain und Source.

Das Gate ist der Eingang. An der Drain ist der Ausgang und an der Source ist VDD (Betriebsspannnung, PFET) oder GND (0 V, NFET).

FET Feldeffekttransistor ist der ▄berbegriff f³r Halbleiterbaulemente, bei denen das elektrische Feld zwischen Gate und Kanal den Kanalwiderstand steuert bzw die Verbindung zwischen Drain und Source trennt oder schliesst.

Es gibt PFETs (PMOSFETs, L÷cherleitung, positive Ladungstrõger, L÷cher) und NFETs (NMOSFETs, negative Ladungstrõger, Elektronen) deren Verhalten komplementõr sind (complementary metal oxide semiconductors, CMOS).

Ist die Gatesourcespannung beim NFET positiv, gr÷▀er als eine Schwellspannung (threshold voltage), wird die Verbindung zwischen Drain und Source leitend (Ein Schalter wird geschlossen).

Ist die Gatesourcespannung beim PFET negativ, kleiner als eine Schwellspannung, wird die Verbindung zwischen Drain und Source leitend (Ein Schalter wird geschlossen).

Durch geschicktes Kombinieren der Transistoren k÷nnen Logikfunktionen technisch realisiert werden.

Fast alle modernen Mikroprozessoren und digitalen Schaltungen werden mit CMOS Transistoren realisiert.

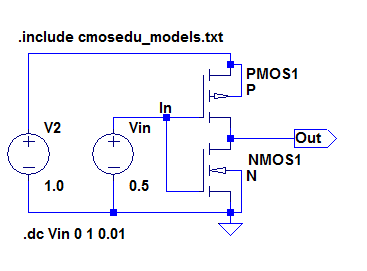

CMOS Inverter (NOT) als Transistorschaltung

Der Schaltplan zeigt einen Inverter, eine Nicht (NOT) Funktion.

Nach der Wahrheitstabelle soll bei einer '1' am Eingang eine '0' am Ausgang erscheinen.

Das Signal wird invertiert.

Jeder Logikschaltkreis ben÷tigt eine Spannungsversorgung (VDD).

Fr³her wurde f³r die Darstellung der '1' 5 V verwendet. Mit der Verkleinerung der Transistoren wurde die Geometrie kleiner. Damit die auftretenden elektrischen Feldstõrken gleich blieben, wurde auch die Versorgungsspannung verkleinert.

2018 arbeitet man mit Versorgungsspannungen um die 1 V.

Dieser Pegel wird auch f³r die Logiksimulation verwendet. Im Praktikum sind Bausteine im Einsatz, die eine Versorgungsspannung zwischen 2.5 V und 5 V ben÷tigen.

Nach der Wahrheitstabelle soll bei einer '1' am Eingang eine '0' am Ausgang erscheinen.

Das Signal wird invertiert.

Jeder Logikschaltkreis ben÷tigt eine Spannungsversorgung (VDD).

Fr³her wurde f³r die Darstellung der '1' 5 V verwendet. Mit der Verkleinerung der Transistoren wurde die Geometrie kleiner. Damit die auftretenden elektrischen Feldstõrken gleich blieben, wurde auch die Versorgungsspannung verkleinert.

2018 arbeitet man mit Versorgungsspannungen um die 1 V.

Dieser Pegel wird auch f³r die Logiksimulation verwendet. Im Praktikum sind Bausteine im Einsatz, die eine Versorgungsspannung zwischen 2.5 V und 5 V ben÷tigen.

CMOS Inverter (NOT) Funktionalitõt

|

|

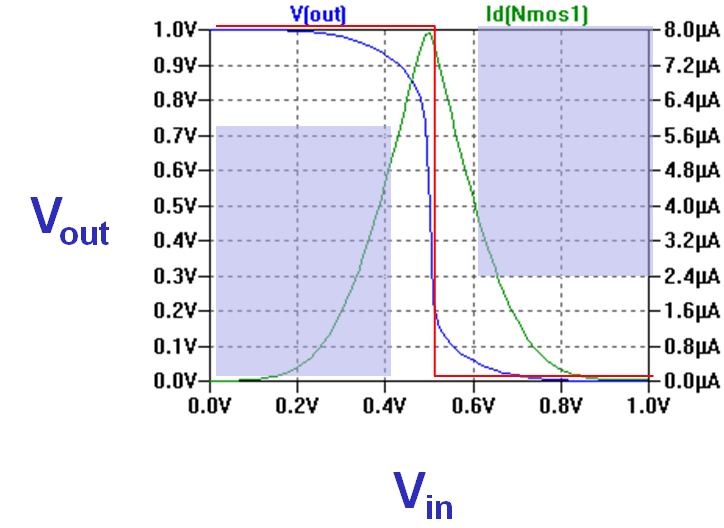

In der Simulation wird die Kennlinie eines Inverters dargestellt.

Bei der Simulation wird am Eingang die Spannung Vin von 0 auf 1 V verõndert und

die Ausgangsspannung beobachtet.

Die Ausgangsspannung Vout õndert sich um Vin = 0.5 V von 1 V auf 0 V.

Man sieht in Gr³n, dass der Strom bei 0.5 V maximal ist. Bei 0 V und 1 V Eingangsspannung flie▀t fast kein Strom.

In Rot ist noch die Idealkennlinie eines Inverters dargestellt. Die reale Kennlinie ist sehr nah an der idealen Kennlinie.

Da um 0.5 V ein digitales Ergebnis nicht klar definiert ist, spezifiziert man mindest Eingangspegel VI und Ausgangspegel VO (output) f³r '0' low (L) und '1' high (H), mit denen das digitale System korrekt arbeitet.

Die Ausgangsspannung Vout õndert sich um Vin = 0.5 V von 1 V auf 0 V.

Man sieht in Gr³n, dass der Strom bei 0.5 V maximal ist. Bei 0 V und 1 V Eingangsspannung flie▀t fast kein Strom.

In Rot ist noch die Idealkennlinie eines Inverters dargestellt. Die reale Kennlinie ist sehr nah an der idealen Kennlinie.

Da um 0.5 V ein digitales Ergebnis nicht klar definiert ist, spezifiziert man mindest Eingangspegel VI und Ausgangspegel VO (output) f³r '0' low (L) und '1' high (H), mit denen das digitale System korrekt arbeitet.

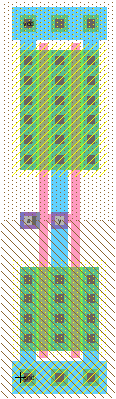

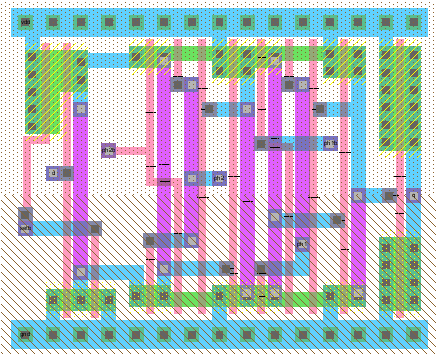

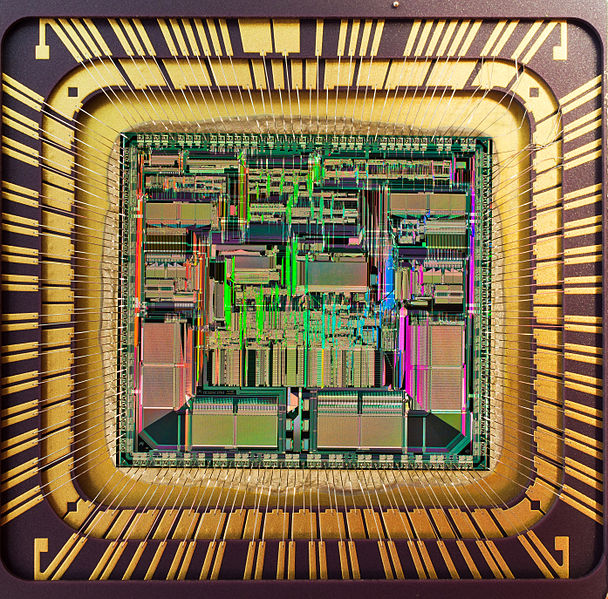

Physikalische Realisierung: CMOS Layout

In integrierten Schaltungen werden Transistoren durch Strukturierung

von verschiedenen Lagen von Materialien durch phototechnische Schritte erzeugt.

Die Strukturen f³r die Realisierung werden dabei in einem Layout festgelegt.

Unterschiedlich farbige Flõchen stehen f³r unterschiedliche Materialien in unterschiedlichen ³bereinanderliegenden Ebenen.

Im Beispiel sind blaue und violette Flõchen Metallverbindungen meist aus Aluminium.

Schwarze und graue Punkte sind Verbindungen (Kontakte) zwischen verschiedenen Ebenen.

Kreuzungen zwischen gr³nen Flõchen und orangenen Linien erzeugen Transistoren.

Ist der Hintergrund punktiert entsteht ein PFET, ist der Hintergrund liniert ein NFET.

Einfache Strukturen werden nebeneinander gelegt und ergeben komplexere Funktionen, bis hin zum rechts gezeigten Mikroprozessor.

Typische Strukturgr÷▀en reichen von fr³her einigen µm bis 2018 einigen nm.

Die Strukturen f³r die Realisierung werden dabei in einem Layout festgelegt.

Unterschiedlich farbige Flõchen stehen f³r unterschiedliche Materialien in unterschiedlichen ³bereinanderliegenden Ebenen.

Im Beispiel sind blaue und violette Flõchen Metallverbindungen meist aus Aluminium.

Schwarze und graue Punkte sind Verbindungen (Kontakte) zwischen verschiedenen Ebenen.

Kreuzungen zwischen gr³nen Flõchen und orangenen Linien erzeugen Transistoren.

Ist der Hintergrund punktiert entsteht ein PFET, ist der Hintergrund liniert ein NFET.

Einfache Strukturen werden nebeneinander gelegt und ergeben komplexere Funktionen, bis hin zum rechts gezeigten Mikroprozessor.

Typische Strukturgr÷▀en reichen von fr³her einigen µm bis 2018 einigen nm.

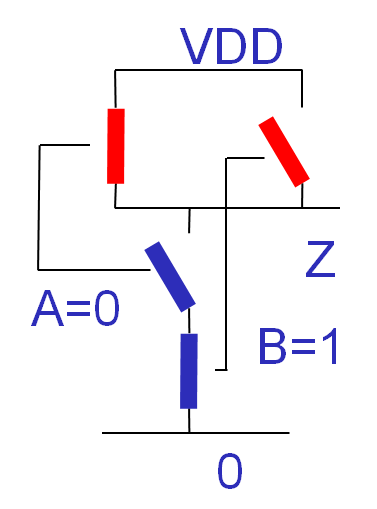

Bsp: Bestimmung einer Schaltfunktion

|

|

Die Transistoren werden im ersten Schritt durch Schalter ersetzt.

Bei einer gewõhlten Eingangssignalkombination wird dann verfolgt, ob der Ausgang mit VDD oder GND (0 V) verbunden ist, und sich so eine '1' oder '0' ergibt.

Daraus ergibt sich dann eine Wahrheitstabelle.

Bei einer gewõhlten Eingangssignalkombination wird dann verfolgt, ob der Ausgang mit VDD oder GND (0 V) verbunden ist, und sich so eine '1' oder '0' ergibt.

Daraus ergibt sich dann eine Wahrheitstabelle.

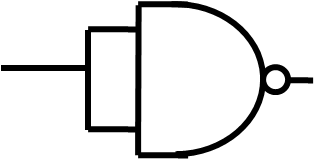

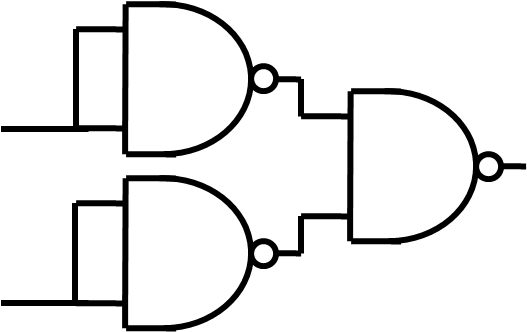

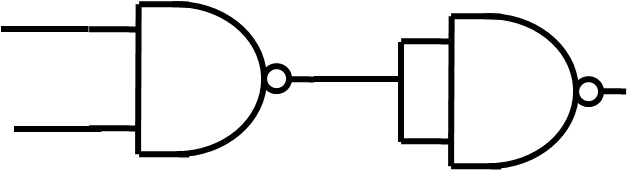

Darstellung von NICHT, UND, ODER durch NAND Funktionen

NICHT: Inverter

|

ODER

|

UND

|

Der Beweis der ─quivalenz ergibt sich entweder durch Vergleich der Wahrheitstabellen

oder durch Umformung der Gleichung mit der booleschen Algebra.

NAND: y = /(x1 · x2)

NICHT: /x = /(x · x)

UND: x1 · x2 = /(/(x1 · x2))

ODER: x1 + x2 = /(/x1 · /x2)

NAND: y = /(x1 · x2)

NICHT: /x = /(x · x)

UND: x1 · x2 = /(/(x1 · x2))

ODER: x1 + x2 = /(/x1 · /x2)

| x1 | x2 | NICHT(X1) /x1 | NICHT(X2) /x2 |

NAND / (x1 · x2) | UND x1 · x2 | ODER x1 + x2 |

NOR /x1 · /x2 |

| 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

Fragen

- Was ist das einfachste Modell f³r einen MOSFET?

- Was ist der Unterschied zwischen einem NMOS und PMOS Transistor?

- Wie sieht der Schaltplan f³r einen CMOS Inverter aus?

- Wie sieht die Kennlinie f³r einen CMOS Inverter aus?

- Was ist ein Layout?

- Wie bestimmt man eine Schaltfunktion aus einem Schaltplan?

- Welche logischen Grundfunktionen ben÷tigt man, um alle booleschen Funktionen darzustellen?

Begriffe

| Begriff/Bauteil | Kenn ich nicht | Kenne ich | Verstehe ich | Kann ich erklõren | Kann ich anwenden |

| Mikroprozessor |

Submit

Thank You!

Hochschule für angewandte Wissenschaften Kempten, Jörg Vollrath, Bahnhofstraße 61 · 87435 Kempten

Tel. 0831/25 23-0 · Fax 0831/25 23-104 · E-Mail: joerg.vollrath(at)fh-kempten.de

Impressum