Digitaltechnik04 Verzögerungszeiten, NormalformProf. Dr.Jörg Vollrath03 Transistorrealisierung und Gatter |

|

Ein kurze Videozusammenfassung der Vorlesung

Länge: 5:54 min

Übungsaufgabe: Zeitverhalten und Verzögerungszeiten

Länge: 3:22 min

Wiederholung und Heute

- Schaltungstechnische Darstellung von Signalen:

CMOS Technologie, MOS-Transistoren, Schalter - Inverter

Heute:

- Verzögerungszeiten

- Multiplexer

- Normalform

CMOS Transistor Array 4007

Praktikum:

Versuch 1

Bedienung Electronic Explorer

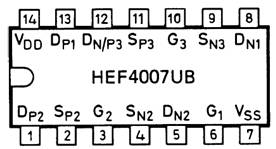

Hier wird ein CD4007 Transistorarray in einem 14 pin DIL (dual in line) Gehäuse gezeigt.

Neben dem realen Bauteil ist auch ein schematische Zeichnung des Gehäuses mit einer Kerbe zur Markierung der Orientierung und der Pinnummerierung und Pinbelegung gezeigt.

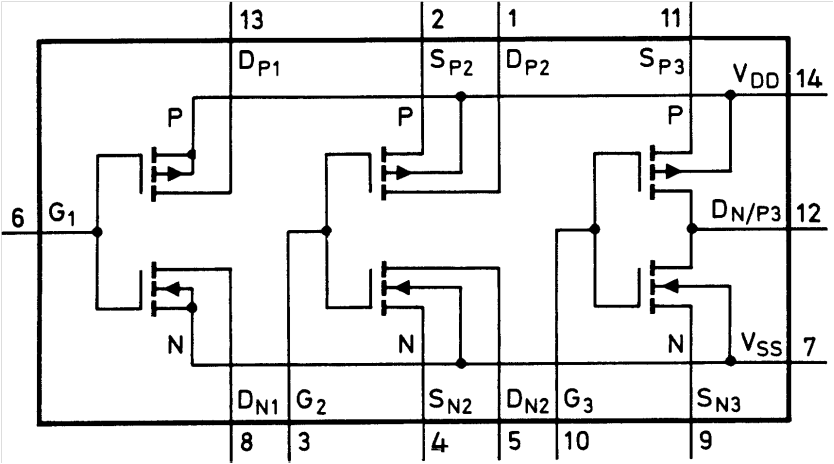

Ausserdem ist noch einen Schaltplan des Innenlebens der integrierten Schaltung abgebildet.

Neben dem realen Bauteil ist auch ein schematische Zeichnung des Gehäuses mit einer Kerbe zur Markierung der Orientierung und der Pinnummerierung und Pinbelegung gezeigt.

Ausserdem ist noch einen Schaltplan des Innenlebens der integrierten Schaltung abgebildet.

Verzögerungszeit

Propagation delay|

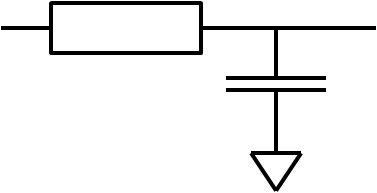

Vorstellung in der Elektrotechnik: Aufladung eines Kondensators (RC Delay) |

|

|

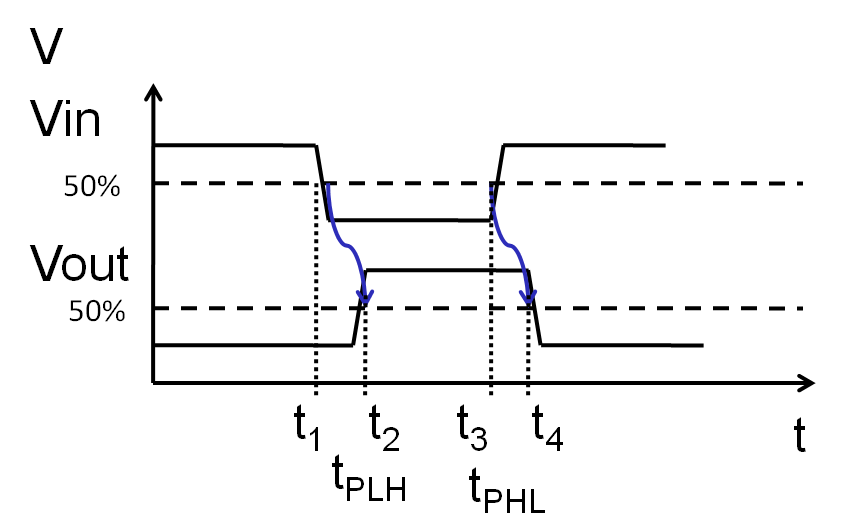

Propagation Delay tP: Blaue Pfeile Unterschiedlich für fallende und steigende Signale (Flanken) Unterschiedliche Transistoren sind aktiv. |

|

Definition

Die Zeit wird von der Änderung des Eingangssignals zur Änderung des Ausgangssignals gemessen.Eine Lastkapazität (Eingangskapazität C der nächsten Logikschaltung) wird durch einen Transitor mit einem Kanalwiderstand RDSon aufgeladen.

Bezugspegel zur Messung der Zeit sind 50% der Versorgungsspannung (Logisch '1').

Die Verzögerungszeit kann je nach steigender oder fallender Flanke des Signals am Ausgang variieren.

Die Verzögerungszeit kann bei verschiedenen Musterwechseln am Eingang unterschiedlich sein.

tpdLH= t2 - t1; Der Ausgang geht von Low (0) auf High (1)

tpdHL= t4 - t3; Der Ausgang geht von High (1) auf Low (0)

Ursache

Jeder CMOS Transistor hat eine Eingangskapazität am isolierten Gate und einen Widerstand zwischen Drain und Source.Über den Widerstand wird die Eingangskapazität des nächsten Gatters aufgeladen oder entladen.

Dies benötigt etwas Zeit.

Aufgabe: Wahrheitstabelle, Verzögerungszeit, Zeitfunktion

|

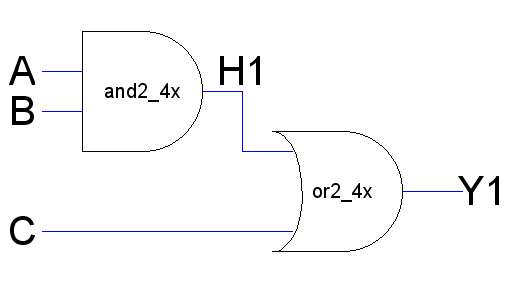

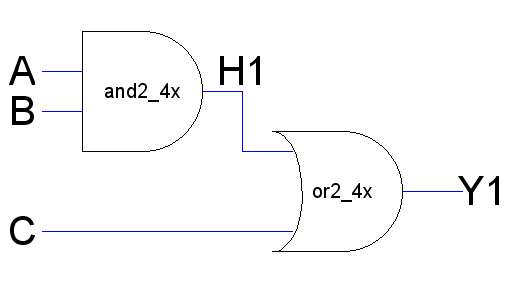

Geben Sie die boolesche Funktion an. Geben Sie die Wahrheitstabelle an.

Y1 = H1 + C = (A * B) + C

|

|

Aufgabe: Wahrheitstabelle, Verzögerungszeit, Zeitfunktion

|

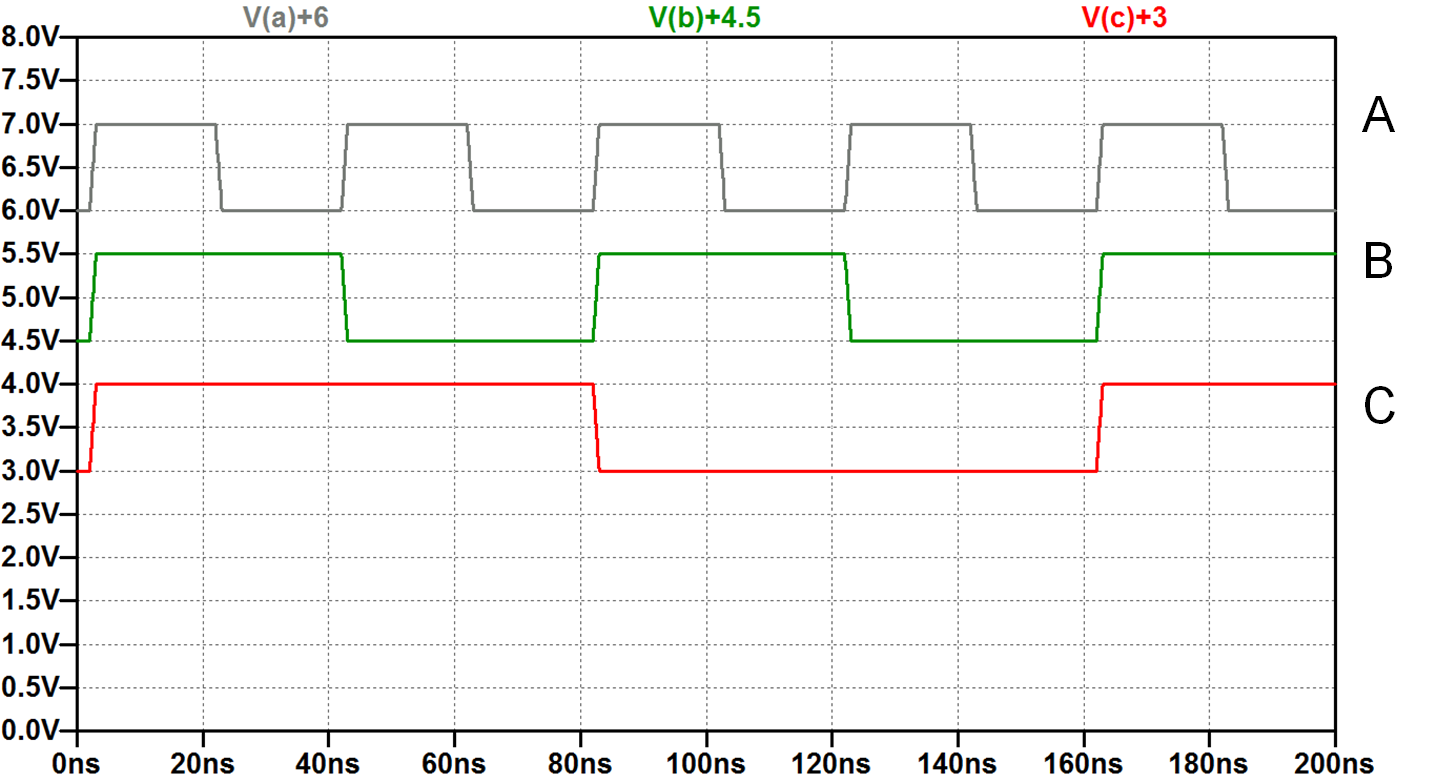

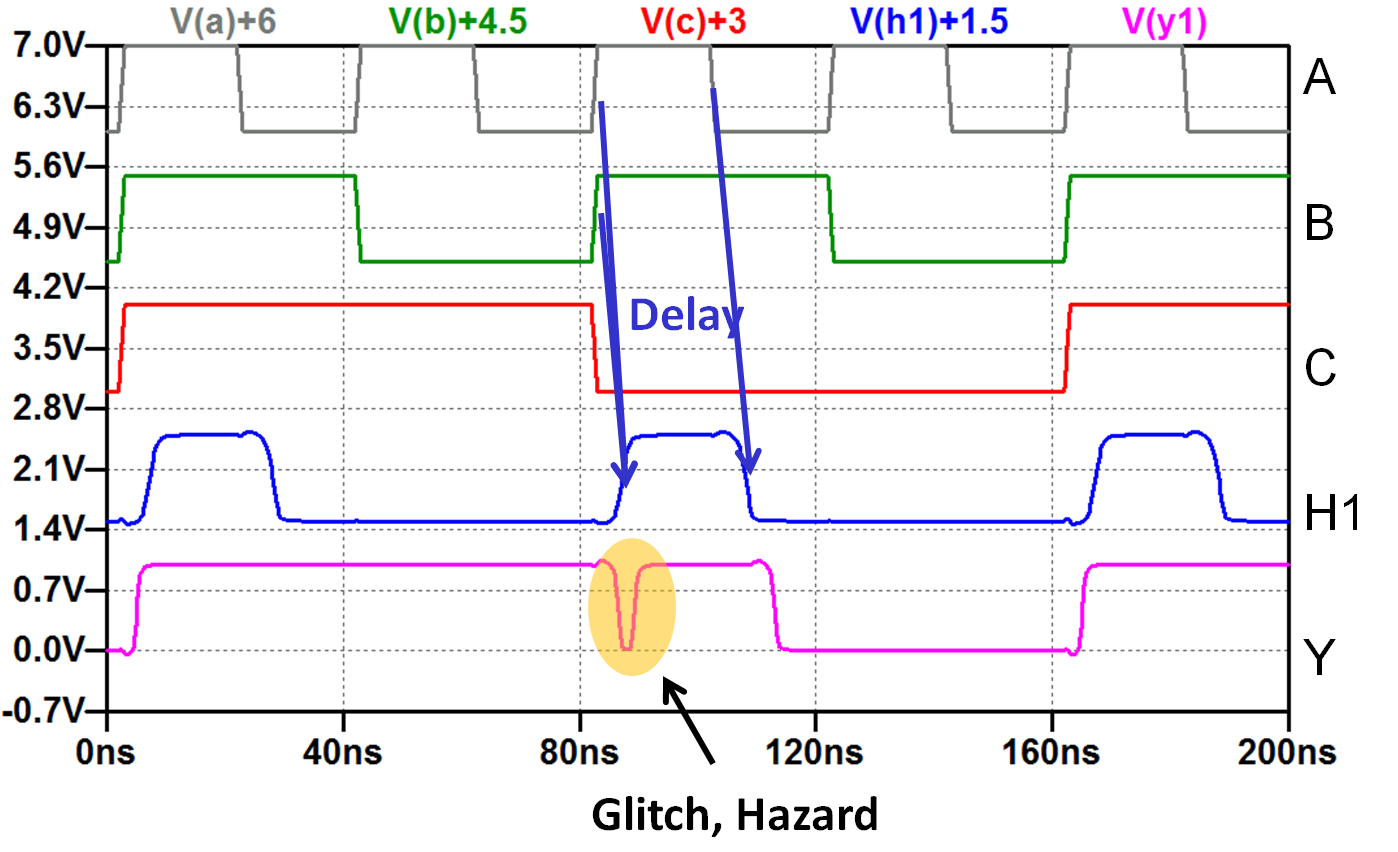

Zeichnen Sie die Zeitfunktion mit einer Verzögerungszeit von 5ns. Folgender Zeitverlauf der Eingangssignale ist gegeben. |

|

Jedes Gatter trägt 5ns Verzögerungszeit bei.

In der Grafik ist die Verzögerungszeit von H1 mit blauen Pfeilen für eine Änderung der Eingangssignale bei 80 ns und 100 ns eingezeichnet.

Der Ausgang ändert sich bei einer Eingangsänderung nicht sofort, sondern erst 5 ns später.

Das Ausgangssignal wird entsprechend nach rechts verschoben.

Bei H1 kann man die Verzögerungszeit von 5 ns bei allen Änderungen sehen.

Das Ausgangssignal kann dann nochmal 5ns verzögert sein, so dass die Gesamtverzögerung von y 10 ns sein kann.

Ein Glitch entsteht, wenn die Laufzeiten der Eingangssignale unterschiedlich sind.

Im gezeigten Fall geht das Signal c bei 80 ns von 1 auf 0. Das Signal H1 ändert sich erst bei 85 ns von 0 auf 1.

Somit erscheint zwischen 85 ns und 90 ns kurz eine 0 am Ausgang.

LTSPICE Simulation

Theorie, Simulation, Messung

Sum of products

Eine Wahrheitstabelle kann durch ODER Verknüpfungen von UND Verknüpfungen dargestellt werden.Beispiel einer gegebenen Wahrheitstabelle mit x1, x2, x3 und Y:

| x1 | x2 | x3 | Y | H1 | H2 |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 |

Eine UND Funktion hat nur eine 1, wenn alle Eingänge 1 sind.

Es werden die Hilfsfunktionen H1 und H2 gebildet, die jeweils eine 1 der Y Spalte abbilden.

H1 = /x1 /x2 x3

H2 = x1 /x2 /x3

Eine ODER Funktion ist 1, wenn einer der Eingänge 1 ist.

Y = H1 + H2.

Y = (/x1 /x2 x3) + (x1 /x2 /x3)

Die UND Verknüpfung von n Variablen, die invertiert und nicht invertiert nur einmal auftreten, nennt man Minterm.

Die ODER Verknüpfung von n Variablen, die invertiert und nicht invertiert nur einmal auftreten, nennt man Maxterm.

Die Gleichung nennt man disjunktive Normalform (DNF) oder sum of products (SOP).

Für eine 1 am Ausgang bildet man einen Minterm der Eingangsvariablen.

Ist die Eingangsvariable in der Zeile der Wahrheitstabelle 0 wird sie invertiert.

Die Funktion H1 ist in der 2. Zeile der Wahrheitstabelle 1.

In dieser Zeile sind x1 und x2 0, müssen also invertiert werden.

H1 = /x1 /x2 x3

Durch die UND Verknüpfung wird H1 nur dann 1, wenn alle Operanden 1 sind.

/x1 = 1; x1 = 0

/x2 = 1; x2 = 0

x3 = 1

Es werden die Hilfsfunktionen H1 und H2 gebildet, die jeweils eine 1 der Y Spalte abbilden.

H1 = /x1 /x2 x3

H2 = x1 /x2 /x3

Eine ODER Funktion ist 1, wenn einer der Eingänge 1 ist.

Y = H1 + H2.

Y = (/x1 /x2 x3) + (x1 /x2 /x3)

Die UND Verknüpfung von n Variablen, die invertiert und nicht invertiert nur einmal auftreten, nennt man Minterm.

Die ODER Verknüpfung von n Variablen, die invertiert und nicht invertiert nur einmal auftreten, nennt man Maxterm.

Die Gleichung nennt man disjunktive Normalform (DNF) oder sum of products (SOP).

Für eine 1 am Ausgang bildet man einen Minterm der Eingangsvariablen.

Ist die Eingangsvariable in der Zeile der Wahrheitstabelle 0 wird sie invertiert.

Die Funktion H1 ist in der 2. Zeile der Wahrheitstabelle 1.

In dieser Zeile sind x1 und x2 0, müssen also invertiert werden.

H1 = /x1 /x2 x3

Durch die UND Verknüpfung wird H1 nur dann 1, wenn alle Operanden 1 sind.

/x1 = 1; x1 = 0

/x2 = 1; x2 = 0

x3 = 1

Fragen und Diskussion

|

Begriffe

| Begriff/Bauteil | Kenn ich nicht | Kenne ich | Verstehe ich | Kann ich erklären | Kann ich anwenden |

| Mikroprozessor |

Submit

Thank You!