Digitaltechnik05 MUX, VHDLProf. Dr.J—rg Vollrath04 Verz—gerungszeiten und Normalform |

|

Ein kurze Videozusammenfassung der Vorlesung

Lðnge: 5:01 min

Ébungsaufgabe: Realisierung einer NAND Verkn■pfung mit einem Multiplexer

Lðnge: 3:23 min

Wiederholung und Heute

- CD4007 und das Praktikum

- Verz—gerungszeiten

- Normalform und sum of products (SOP)

- Schaltung zur Normalform

- Multiplexer

- VHDL

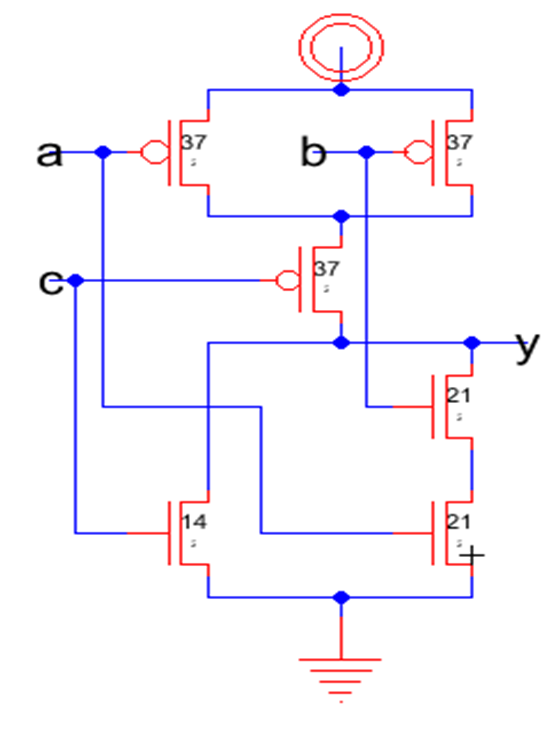

Implementierung von Logikfunktionen

|

CMOS Technik NAND Gatter AOI (AND, OR, INVERT) Logik Dynamische Logik Multiplexer |

|

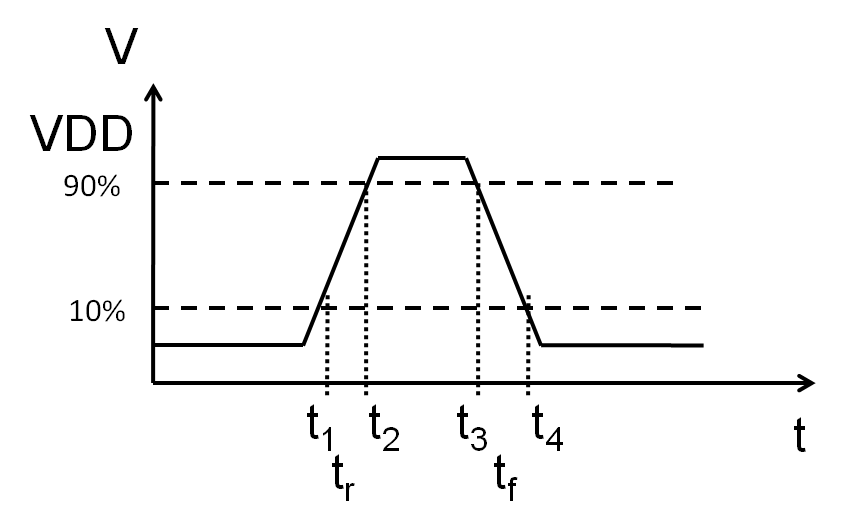

Anstiegszeit und Abfallszeit

Die Definition f■r die Anstiegszeit lautet: man nimmt die Zeiten bei denen

10% und 90% des Pegels VDD (Versorgungsspannung) erreicht wird.

Die Differenz der Zeiten ergibt die Anstiegszeit (Rise time) tr=t2-t1.

Die Abfallzeit (Fall time) ist analog definiert tf = t4-t3.

Dieses Bild gibt es auch bei Wikipedia.

Es ergibt sich durch diese spezifische Definition eine wiederholbare Messung.

Die Differenz der Zeiten ergibt die Anstiegszeit (Rise time) tr=t2-t1.

Die Abfallzeit (Fall time) ist analog definiert tf = t4-t3.

Dieses Bild gibt es auch bei Wikipedia.

Es ergibt sich durch diese spezifische Definition eine wiederholbare Messung.

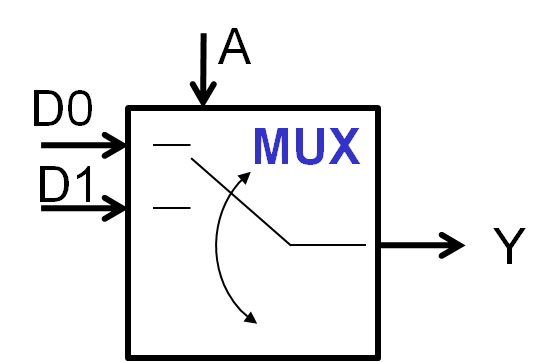

Multiplexer und Demultiplexer

Funktion:- Die Konzentration von n Leitungen auf eine Leitung: Multiplexer

- Die Verteilung von einer Leitung auf n Leitungen: Demultiplexer

Eingðnge:

n Signale: D0..Dn-1

i = ld(n) Auswahlsignale: A0..Ai

Ausgang: Y

Anwendung

- Vermittlung von Telefongesprðchen, Internetverbindungen

- Parallel-Serien- und Serien-Parallel-Umsetzung

- Mikroprozessor zur Auswahl der Verarbeitungsoperation

- Speicherglieder

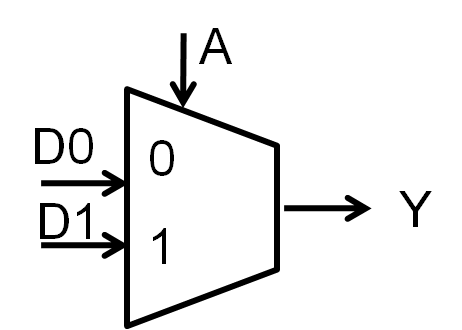

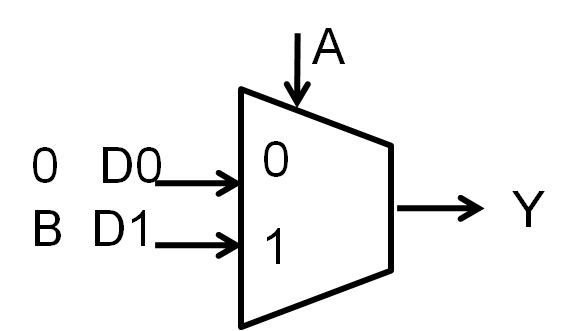

2-1 Multiplexer

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

UND Funktion mit Multiplexern

Kann man eine UND Funktion mit 2 Eingðngen mit einem Multiplexer realisieren?

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

UND Funktion

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

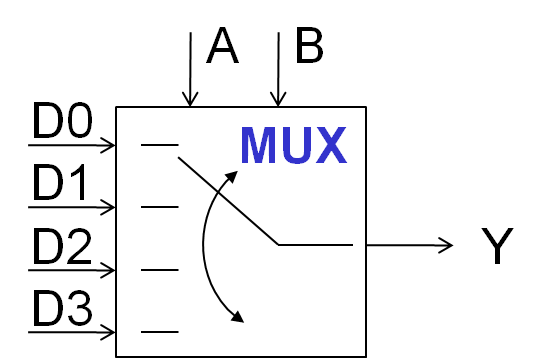

Beispiel: 4-1 Multiplexer

Wie sieht ein 4-1 Multiplexer aus?

|

|

|||||||||||||||||||

|

DEMUX

Ein Eingang D wird auf die Ausgðnge Y0, Y1 in Abhðngigkeit von A verteilt.

Erweiterung der Zustðnde:

|

|

||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||

VHDL

VHDL: Wikipedia: Very High Speed Integrated Circuit Hardware Description LanguageTextuelle Beschreibung, Programmiersprache, Nebenlðufigkeit

Verilog: Hardwarebeschreibungssprache

In dieser Vorlesung wird versucht mit minimalen Kenntnissen in begrenzter Zeit Hardware zu beschreiben und zu realisieren (FPGA).

Strategie

Kopieren, Modifizieren, TestenWas erwarten Sie von einer Programmiersprache?

Schl■sselw—rter

Variablen, Typen

Zuweisungen

Struktur: Strichpunkte, Funktionen, Bl—cke

Verzweigungen und Schleifen

Variablen, Typen

Zuweisungen

Struktur: Strichpunkte, Funktionen, Bl—cke

Verzweigungen und Schleifen

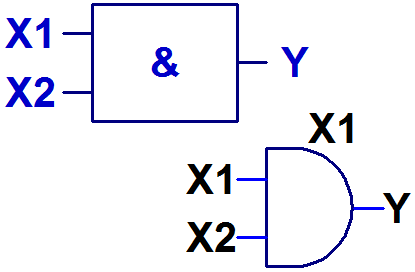

Darstellung boolescher Verkn■pfungen

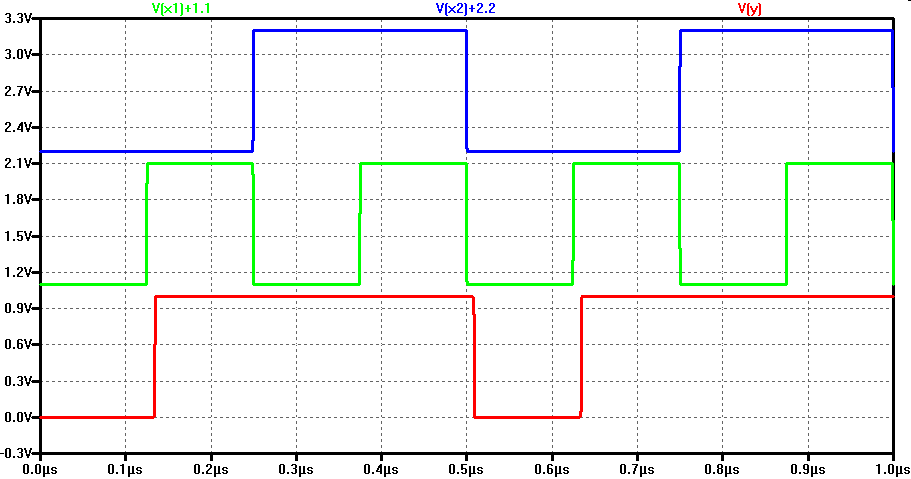

Schaltfunktion UNDY = f(x1,x2) = x1 ^ x2 = x1 ñ x2 Wahrheitstabelle

|

Schaltsymbol, Schaltverhalten

VHDL Beschreibung

|

VHDL Beschreibung

|

VHDL Beschreibung

|

Fragen und Diskussion

|

Begriffe

| Begriff/Bauteil | Kenn ich nicht | Kenne ich | Verstehe ich | Kann ich erklðren | Kann ich anwenden |

| Mikroprozessor |

Submit

Thank You!