Digitaltechnik08 MinimalformProf. Dr.J÷rg Vollrath07 Zeichen und Codes |

|

Ein kurze Videozusammenfassung der Vorlesung

Lõnge: 9:33 min

Wiederholung und Heute

Wiederholung:

- Ganze Zahlen

- Festkommazahlen, Gleitkommazahlen

- Rechnen mit Zahlen

- Codes: ASCII, UTF, Gray Code, Thermometer Code

Heute:

- Praktikum

- Fehlersuche, Feedback

- Von der Problemstellung zur digitalen Schaltung

- Minimierung und Karnaugh Veitch Diagramm

- Informationen und Programme zur Minimierung

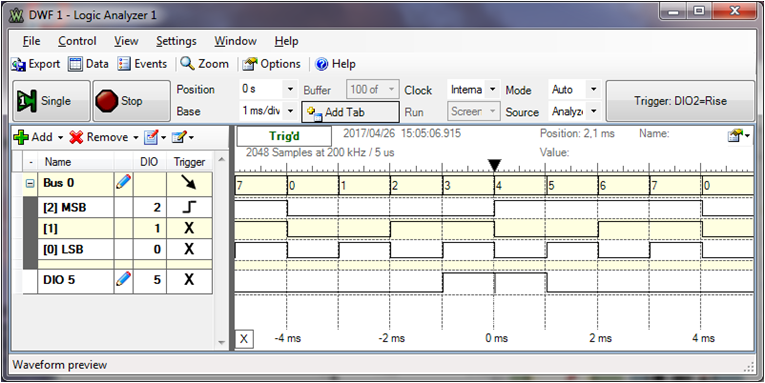

Fehlersuche in einem Schaltungsaufbau

- Versorgungsspanung:

- Einschalten, keine Strombegrenzung

- Strom ist zu hoch: Abtrennen von Teilschaltungen

- Signalgeneratoren:

- Einschalten, ▄berpr³fen der Signalform mit dem Oszilloskop

- ▄berpr³fung der Signale von der Quelle bis zum Ziel (Ausgang) oder vom Ziel bis zur Quelle mit dem Oszilloskop (Signalverfolgung).

- Signalpegel zu niedrig oder Zwischenwerte

- Fehlt die Masseverbindung? (Verbindung hinzuf³gen)

- Fehlt die Spannungsversorgung? (Verbindung hinzuf³gen)

- Gibt es einen Kurzschluss? (Verbindungen trennen)

- Zu viele oder zu wenig '1'er am Ausgang

- Signalverfolgung

- Langsame Schaltung: Verz÷gerungszeit von Eingang zu Ausgang ist gro▀.

- Fehlt die Masseverbindung?

Bei einem Schaltungsaufbau wird es immer Fehler geben.

Die Fehler k÷nnen durch falsche Verdrahtung des Benutzers, aber auch durch fehlerhafte Kontakte oder defekte Bauteile auftreten.

Man muss einen Fehler feststellen und dann diagnostizieren woher der Fehler kommt.

Bei der Herstellung von integrierten Schaltungen k÷nnen die Testkosten genauso hoch sein, wie die Fertigungskosten.

Im Praktikum Schaltungen aufgebaut, um die Theorie zu verifizieren und Schwierigkeiten beim praktischen Aufbau aufzu zeigen.

Man gewinnt auch eine Vorstellung davon, wie viel Zeit eine bestimmte Realisierung und Messung ben÷tigt.

Das Praktikum ist so aufgebaut, dass man, bei gr³ndlicher Vorbereitung durch lesen der Versuchsanleitung, das Praktikum in 90 Minuten durchf³hren kann.

Es ist normal, dass die erste Durchf³hrung viel mehr Zeit in Anspruch nimmt, als eine Wiederholung.

Fehlersuche kann man lernen und systematisch durchf³hren.

Zu jeden Fehler geh÷rt auch eine Ursache.

Durch sorgfõltiges und systemtische Arbeit k÷nnen Fehler vermieden werden.

Die Automatisierung elimiert die Fehler, die durch manuelle Tõtigkeiten und Variationen auftreten.

Ein Arbeiter kann m³de oder wach und deshalb konzentriert oder unkonzentriert arbeiten.

Die Fehler k÷nnen durch falsche Verdrahtung des Benutzers, aber auch durch fehlerhafte Kontakte oder defekte Bauteile auftreten.

Man muss einen Fehler feststellen und dann diagnostizieren woher der Fehler kommt.

Bei der Herstellung von integrierten Schaltungen k÷nnen die Testkosten genauso hoch sein, wie die Fertigungskosten.

Im Praktikum Schaltungen aufgebaut, um die Theorie zu verifizieren und Schwierigkeiten beim praktischen Aufbau aufzu zeigen.

Man gewinnt auch eine Vorstellung davon, wie viel Zeit eine bestimmte Realisierung und Messung ben÷tigt.

Das Praktikum ist so aufgebaut, dass man, bei gr³ndlicher Vorbereitung durch lesen der Versuchsanleitung, das Praktikum in 90 Minuten durchf³hren kann.

Es ist normal, dass die erste Durchf³hrung viel mehr Zeit in Anspruch nimmt, als eine Wiederholung.

Fehlersuche kann man lernen und systematisch durchf³hren.

Zu jeden Fehler geh÷rt auch eine Ursache.

Durch sorgfõltiges und systemtische Arbeit k÷nnen Fehler vermieden werden.

Die Automatisierung elimiert die Fehler, die durch manuelle Tõtigkeiten und Variationen auftreten.

Ein Arbeiter kann m³de oder wach und deshalb konzentriert oder unkonzentriert arbeiten.

Allgemeines Feedback und studentische Verantwortung

|

|

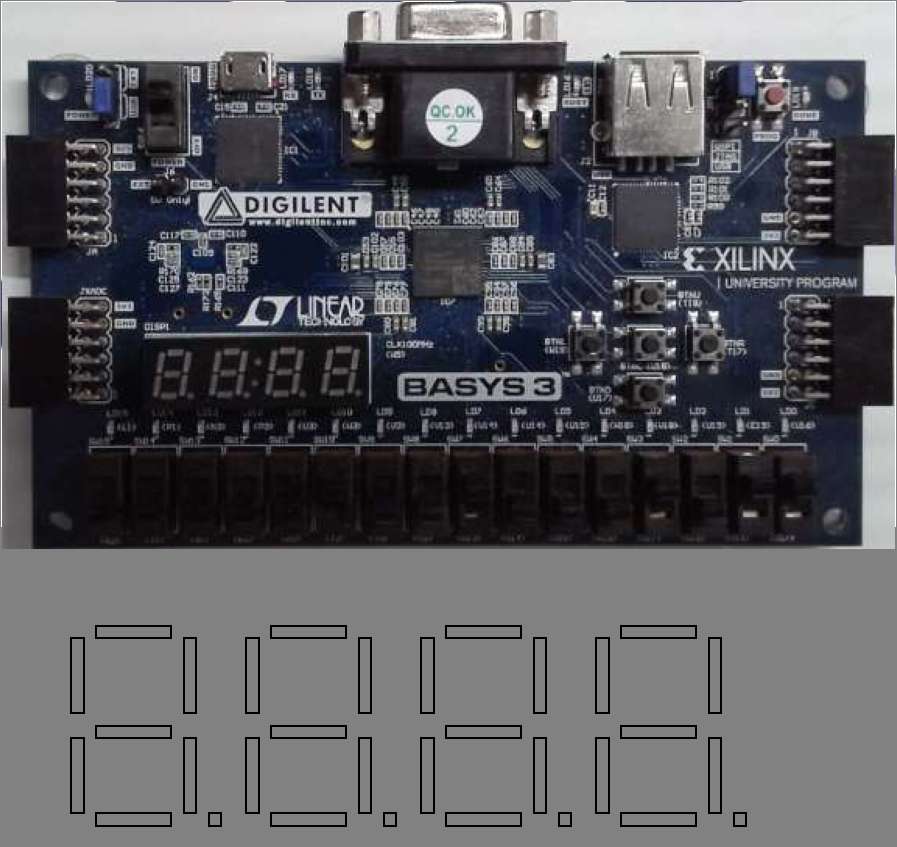

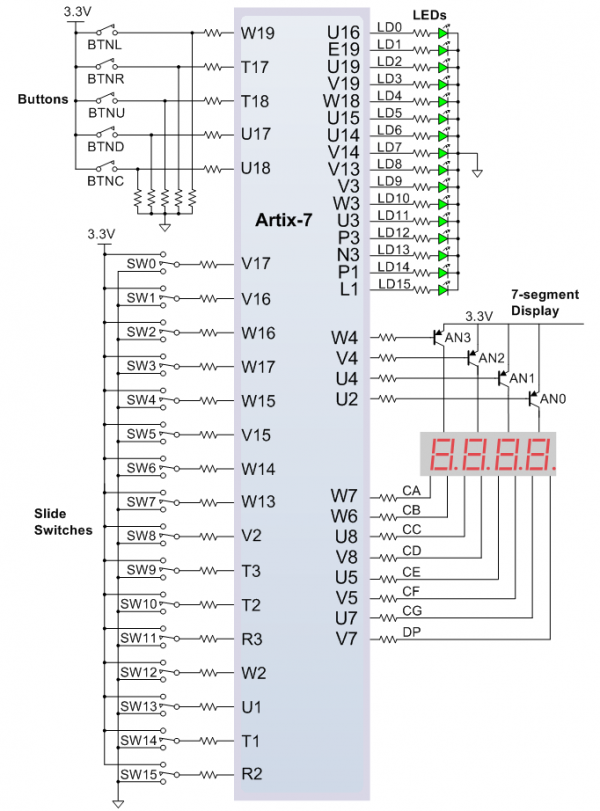

Versuch 3: Ansteuerung einer 7 Segment Anzeige

|

Im Projekt werden die Schiebeschalter SW0 bis SW3 als Dualzahl interpretiert

und die entsprechende Hexadezimalzahl mit der Siebensegmentanzeige angezeigt. 1. Erstellung eines Projekts 2. Simulation der Schaltung 3. Transfer der Schaltung in das FPGA auf dem Board und Test. Eine xdc (xilinx constraint file) Datei legt die Verbindung von physikalischem Pin am Baustein zu einem VHDL STD_LOGIC Signal fest. |

|

NET "clk" LOC = "B8"; # Bank = 0, Signal name = MCLK

Syntax der xdc Datei

Kommentar: # Hash

# clock pin for Basys2 Board

NET "clk" LOC = "B8"; # Bank = 0, Signal name = MCLK

Das Signal CLK STD_LOGIC wird mit pin B8 (verbunden).

Eine xdc Datei geh÷rt zu einer bestimmten Platine.

Versuch 3

Schaltplan der 7 Segment Anzeige

|

|

Um Verbindungen (Leitungen und Pins) zu sparen wird die 7 Segment Anzeige gemultiplext.

Nacheinander werden die einzelnen Stellen angezeigt. Da dies sehr schnell passiert (50 mal in der Sekunde) kann das menschliche Auge dies nicht wahrnehmen.

Wenn einer der Pins (F12, J12, M13, K14) 0 V ist verbindet ein bipolar Transistor die ausgewõhlte Stelle mit 3.3 V.

Alle Segmente die an der Ansteuerleitung (L14, H12, N14, N11, P12, L13, M12, N13) 0V haben leuchten.

Im Praktikum wird immer nur eine Stelle angesteuert, um die Multiplexerschaltung zu sparen.

Nacheinander werden die einzelnen Stellen angezeigt. Da dies sehr schnell passiert (50 mal in der Sekunde) kann das menschliche Auge dies nicht wahrnehmen.

Wenn einer der Pins (F12, J12, M13, K14) 0 V ist verbindet ein bipolar Transistor die ausgewõhlte Stelle mit 3.3 V.

Alle Segmente die an der Ansteuerleitung (L14, H12, N14, N11, P12, L13, M12, N13) 0V haben leuchten.

Im Praktikum wird immer nur eine Stelle angesteuert, um die Multiplexerschaltung zu sparen.

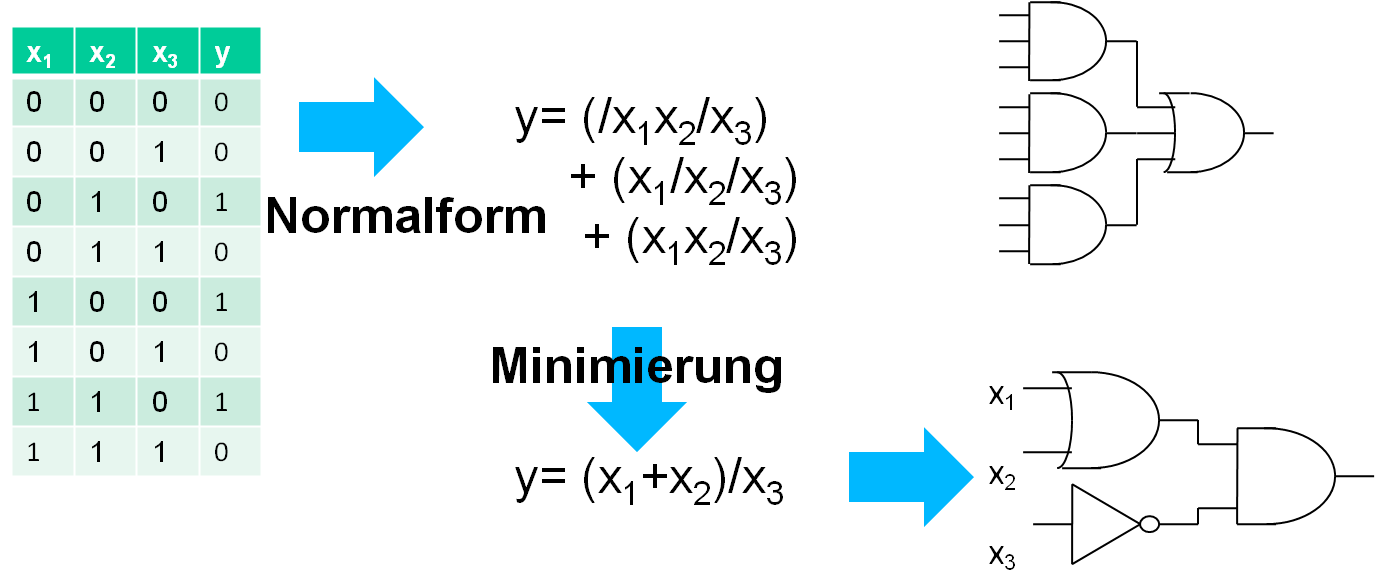

Von einer Problemstellung zu einer logischen Schaltung

Problemstellung: Eingõnge und AusgõngeWahrheitstabelle

Ziel:

Realisierung der logischen Funktion mit m÷glichst wenig logischen Verkn³pfungen: Normalform, Minimierung

Logische Gleichung f³r eine Wahrheitstabelle

Normalform, disjunktive NormalformMinimierung:

- Boolesche Algebra

- Karnaugh Veitch Diagramm

- Algorithmisch (FPGA, VHDL Compilier)

Karnaugh Veitch Diagramm

Eine andere Darstellung einer Wahrheitstabelle

| |||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||

- Zusammenfassung von horizontalen oder vertikalen Gruppen von 2,4 oder 8 '1'

- Dabei kann man von rechts nach links ³ber die Begrenzung des Kastens gehen.

- Dabei kann man von oben nach unten ³ber die Begrenzung des Kastens gehen.

In der linken Darstellung sind die Zeilen der Wahrheitstabelle angegeben in der man nach dem

Ausgangssignal suchen muss.

Karnaugh Veitch Diagramm: 4 Eingõnge

|

|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Unvollstõndige Wahrheitstabelle: Don't Care

In der Realitõt kann es vorkommen, dass bestimmte Eingangssignalkombinationen

eigentlich nicht auftreten k÷nnen.Beispiel AufzugEin Aufzug hat einen Sensor O f³r 'oben' und einen Sensor U f³r 'unten' (Eingõnge). Der Aufzugsmotor M soll abgeschaltet werden '0', wenn der Aufzug die Position oben oder unten erreicht (Ausgang). Eigentlich sollten nicht beide Sensoren aktiv '1' sein k÷nnen. Deshalb wird in diese Zeile d eingetragen Bei der Minimierung kann das d als '1' oder '0' verwendet werden. Nach der Minimierung wird der Wert den man erwendet in die Wahrheitstabelle eingetragen und durch Test verifiziert. |

|

Informationen und Programme zur Minimierung

Algorithmus zur Minimierung:

Quine und McCluskey

Wikipedia: Quine und McCluskey

Javascript: Universitõt Marburg

Karnaugh-Veitch Map

Javascript: Karnaugh-Veitch, Universitõt Marburg

VHDL und Synthese Werkzeuge

Der Programmcode wird in eine Minimalform ³berf³hrt, egal wie die tatsõchliche textuelle Beschreibung (if, Case, when) ist.

Codeumsetzer: Binõrcode zu Gray Code

|

|

Fragen und Diskussion

|

09 Schaltwerke und Speicherglieder

Board, Test, FPGA, STD_LOGIC, UCF Datei, Pin, 7 Segment Anzeige, Schaltungsaufbau, Minterm, Karnaugh Veitch Diagramm, Synthese