Digitaltechnik10 ZustandsmaschinenProf. Dr.J÷rg Vollrath09 Schaltwerke |

|

Ein kurze Videozusammenfassung der Vorlesung

Lõnge: 6:03 min

Eine Zustandstabelle einer VHDL-Beschreibung

Lõnge: 6:03 min

R³ckblick und Heute

R³ckblick:

- Schaltnetz und Schaltwerk

- Synchrone und asynchrone Schaltungen

- Taktflankensteuerung

- D-Flip-Flop

- Setup und Hold Zeit

Heute:

- VHDL Beschreibung eines Schaltwerkes

- Abfrage eines Tasters

- Hierarchie in VHDL

- Zustandsmaschinen

Synchrone Schaltungen

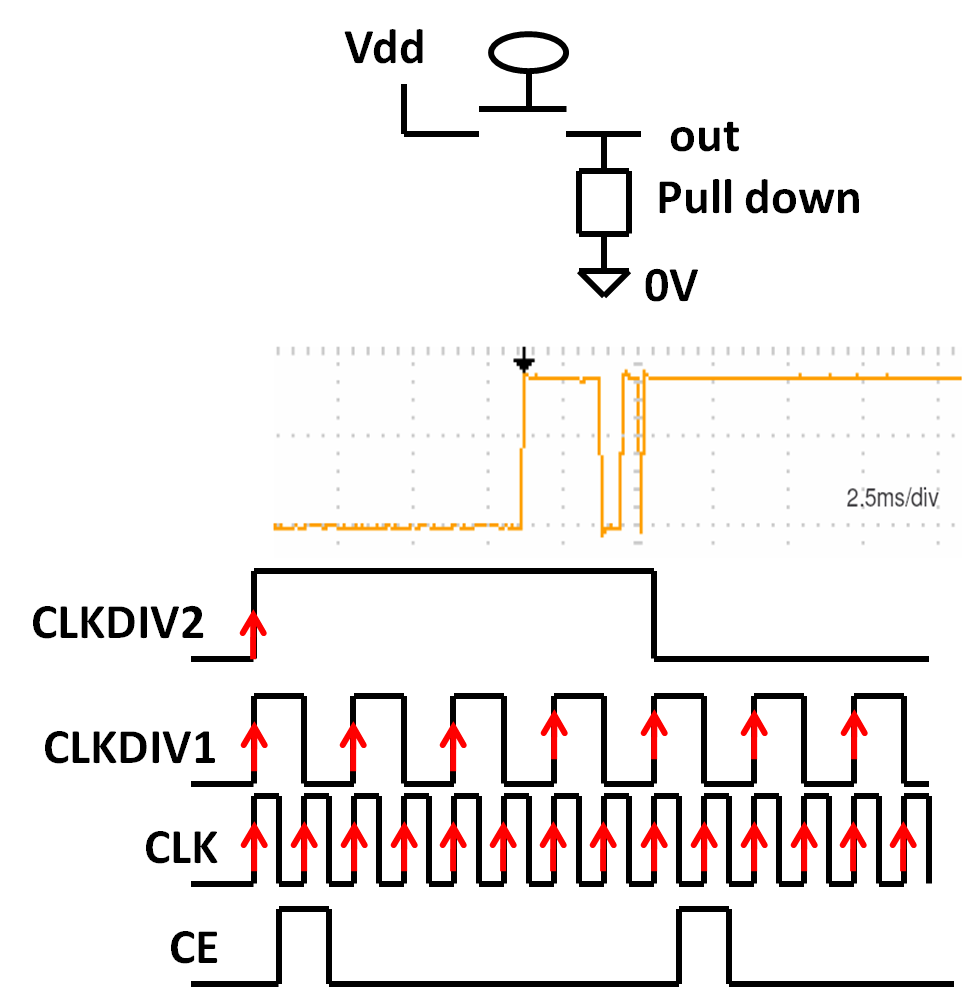

Es gibt einen globalen Takt CLK f³r alle positiv flankengesteuerte Speicherglieder (positive edge triggered). Langsamere Ablõufe werden mit der Kombination aus CLK und CE (clock enable) realisiert.

Das CE Signal wird mit der gew³nschten Frequenz immer f³r einen Zyklus '1'.

Praktische Realisierung von Speicherglieder: Baustein

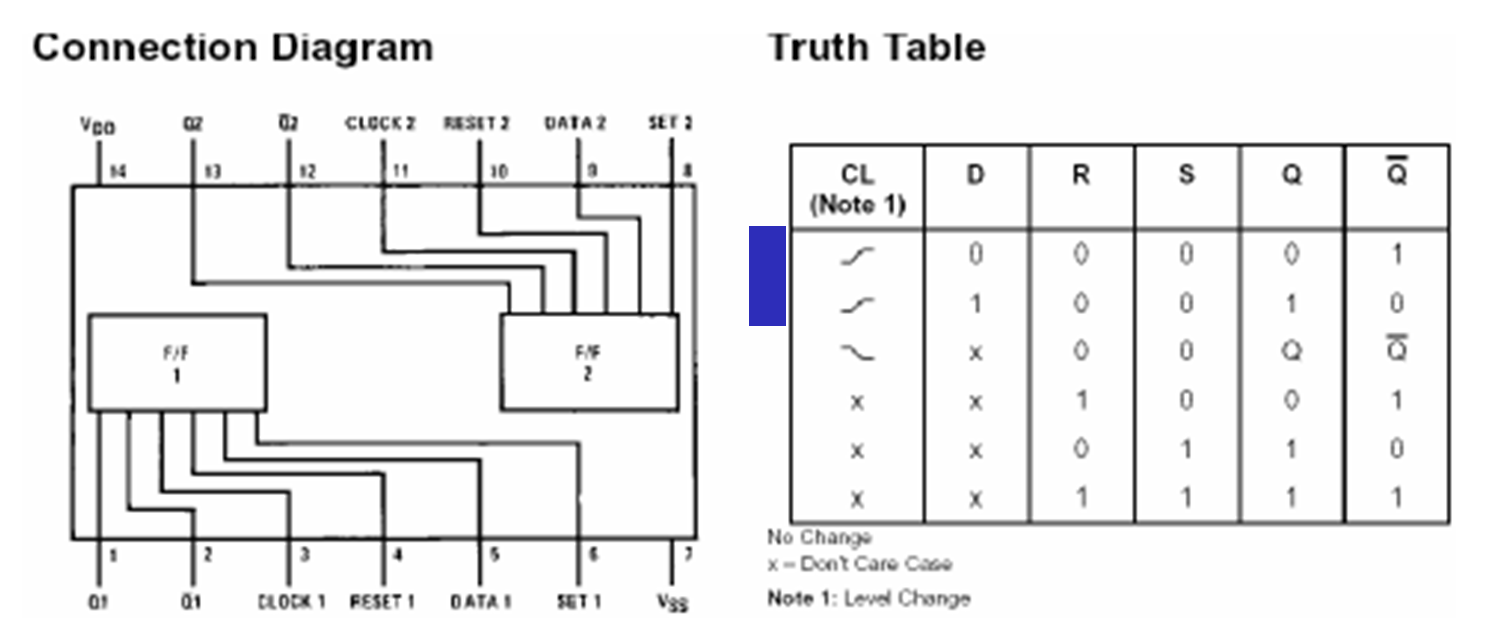

D-Flip-Flop CD4013

Positiv flankengesteuert

Asynchroner Reset, Set

CD4013 Texas Instruments

Praktische Realisierung von Speichergliedern: Schaltung

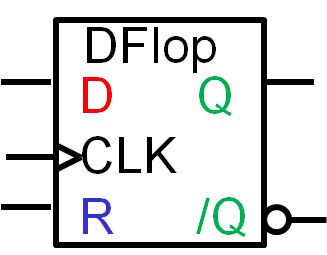

Im Schaltsymbol kann man das Dreieck f³r die Taktflankensteuerung erkennen.

Es werden 2 Takteingangssignale verwendet.

Diese sind nicht ³berlappend, damit eine korrekte Funktion sichergestellt wird.

Beim Resetb Eingang sieht man einen Kreis. Das Signal wird invertiert. Wenn das Signal '0' ist, wird das D-Flip-Flop zur³ck gesetzt.

Im Zweifelsfall sollte man die Funktion m÷glichst fr³h verifizieren.

Wenn man nicht selbsterstellte Schaltungsbl÷cke verwendet, sollte immer ein Test dabei sein, der die Funktion verifiziert.

Weiterhin sieht man in der Abbildung den Schaltplan mit Transistoren. Der Schaltplan enthõlt 2 Latches. Der Reset ist synchron, da das Signal alternativ zu den Daten anliegt wird. Unten sieht man noch lokale Treiber f³r die CLOCK Signale, um auch invertierte Signale zu erzeugen.

Insgesamt hat die Schaltung 30 Transistoren.

Im Layout sieht man, wie gross ein typisches D-Flip-Flop ist. Transistoren ergeben sich an den kreuzungen der orangen und gr³nen Flõchen.

Die Gesamtflõche wird dabei weniger durch die Transistoren, als durch die Anschl³sse und die Verdrahtung bestimmt.

Beim Resetb Eingang sieht man einen Kreis. Das Signal wird invertiert. Wenn das Signal '0' ist, wird das D-Flip-Flop zur³ck gesetzt.

Im Zweifelsfall sollte man die Funktion m÷glichst fr³h verifizieren.

Wenn man nicht selbsterstellte Schaltungsbl÷cke verwendet, sollte immer ein Test dabei sein, der die Funktion verifiziert.

Weiterhin sieht man in der Abbildung den Schaltplan mit Transistoren. Der Schaltplan enthõlt 2 Latches. Der Reset ist synchron, da das Signal alternativ zu den Daten anliegt wird. Unten sieht man noch lokale Treiber f³r die CLOCK Signale, um auch invertierte Signale zu erzeugen.

Insgesamt hat die Schaltung 30 Transistoren.

Im Layout sieht man, wie gross ein typisches D-Flip-Flop ist. Transistoren ergeben sich an den kreuzungen der orangen und gr³nen Flõchen.

Die Gesamtflõche wird dabei weniger durch die Transistoren, als durch die Anschl³sse und die Verdrahtung bestimmt.

VHDL code eines Speichergliedes

entity: Name, Eingõnge, Ausgõnge

|

|

F³r ein Speicherglied ben÷tigt man in VHDL einen 'process' Block und eine unvollstõndige 'if' Anweisung.

Im Beispiel oben wird nur das Verhalten f³r eine steigende CLK Flanke definiert.

Alle anderen Fõlle f³r das CLK Signal werden nicht spezifiziert.

Dies stellt eine unvollstõndige 'if' Abfrage dar und der VHDL Compiler erstellt ein Speicherglied.

Es ist nicht klar, ob der Compiler ein Speicherglied mit Inverter f³r q und bq synthetisiert, oder 2 Speicherglieder eins f³r q und eins f³r nicht q.

In der Log Datei werden diese Informationen aufgef³hrt.

Man sollte rising_edge(clk) statt (clk'event) and (clk='1') verwenden.

Es ist nicht klar, ob der Compiler ein Speicherglied mit Inverter f³r q und bq synthetisiert, oder 2 Speicherglieder eins f³r q und eins f³r nicht q.

In der Log Datei werden diese Informationen aufgef³hrt.

Man sollte rising_edge(clk) statt (clk'event) and (clk='1') verwenden.

Verifikation mit Simulation

Hierarchische Bl÷ckeComponent, Instanz

Abfrage eines Tasters

|

Pull down und/oder pull up Widerstand Clock: 10 MHz, 100ns Dr³cken: 100ms 10 mal pro Sekunde. Prellen Jeder Wechsel von 0 auf 1 kann eine Aktion ausl÷sen. Beim einmaligen Dr³cken wird der Taster mehrmals von der Clock abgefragt und der Zõhler wird mehrmals hochgezõhlt. Ein langsamer Takt, der durch einen Zõhler erzeugt werden kann, oder besser ein CE Signal wird zur Abfrage verwendet. Das Abfrageintervall darf nicht zu kurz oder lang sein. Ist das Intervall zu lang hat der Benutzer das Gef³hl es passiert nichts. |

|

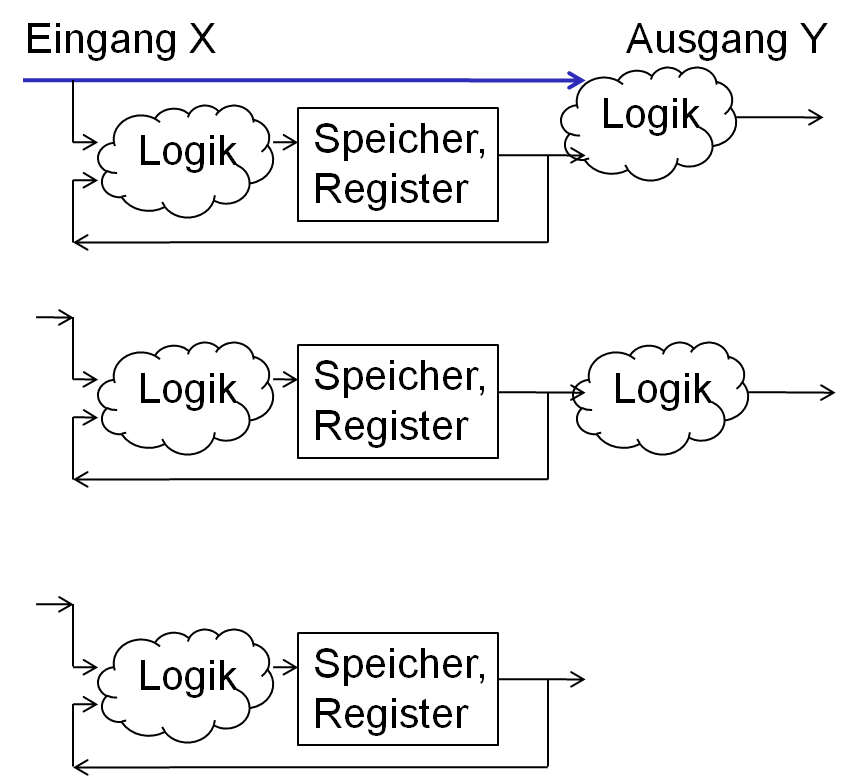

Zustandsmaschinen

Automaten: zeitgesteuerter Ablauf mit einem TaktZõhler, Uhr, Waschmaschine, Aufzug, MP3 Player

Mealey, Moore, Medwedew

|

Mealey: Y = g( x, S(f(x))) Der Ausgang Y ist vom Eingang X und Zustand S abhõngig. Moore: Y = g( S(f(X))) Der Ausgang Y vom Zustand S abhõngig. Medwedew: Y = S(f(X)) Der Ausgang Y ist der Zustand S. |

|

Aufgrund der Testbarkeit werden nur noch Medwedew

Automaten verwendet.

Fragen und Diskussion

|

11 Zustandsdiagramm und Zõhler

Truth table, Pull up Widerstand, Prellen, Automat, Zustandsmaschine, Mealey Automat,

Moore Autmat, Medwedew Automat