Elektronik 315 RegisterProf. Dr.Jörg Vollrath14 Verknuepfungen |

|

Video der 15. Vorlesung (24.11.2021)

|

Länge: 1:11:00 |

0:0:0 Willkommen 0:0:3 Schaltung Normalform LTSPICE Simulation 0:3:11 Eingangssignalerzeugung 0:4:31 Verzögerungszeit 50% LowHigh tPDLH 0:5:31 tPDLH, 0:7:36 tPDLH, tPDHL 0:8:11 Gesamtverzögerungszeit 0:10:6 Glitch 0:12:31 NAND Verzögerungszeit 0:13:24 Normalform, CPL, FPGA 0:14:6 Wahrheitstabelle und Simulation 0:16:24 Schaltnetz und Schaltwerk 0:18:34 Digitaltechnik Beschreibungsarten 0:18:54 Schaltnetz und Schaltwerk 0:20:34 Speicherelement, Oszillator mit Invertern 0:24:7 Ein Schalter mit CLK zum Schreiben und Halten von Daten 0:29:34 Synchron und asynchrone Schaltung 0:31:34 Pegelgesteuert 0:32:57 Wahrheitstabelle, Flankensteuerung, Zustandstabelle 0:36:2 Bisherige Notizen und Speicherglieder 0:37:17 Zustandstabelle 0:37:47 2-Bit Zähler 0:40:12 Start Zustandstabelle 0:44:2 Zustandstabelle und Reihenfolge der Zeilen 0:45:22 Typisches Zählbeispiel 0:48:22 Zeitverhalten entwickeln 0:53:40 Warum ändert sich DOWN zwischen 2 CLK Flanken 0:57:32 Zeichnen des Zeitverhaltens 1:0:38 D-Flip-Flop flankengesteuert 1:3:38 Qm und CLK low 1:6:38 Qs 1:8:44 Master Slave Flip-Flop 1:9:55 Flip Flop mit CE, R (CLR), TE, TDI, TDO |

Rückblick und Heute

Rückblick:

Heute:

- Schaltnetz und Schaltwerk

- Synchrone und asynchrone Schaltungen

- Taktflankensteuerung

- D-Flip-Flop

- Setup und Hold Zeit

Schaltnetz und Schaltwerk

Schaltnetz:

- Der Ausgang hängt nur vom Zustand der Eingangssignale ab.

- Die Funktion wird durch kombinatorische Elemente (z.B. NAND) dargestellt.

- Es gibt keine Rückkopplung.

Schaltwerk:

- Der Ausgang hängt nicht nur vom gegenwärtigen Zustand der Eingangssignale ab, sondern auch von vorherigen Zuständen.

- Die Verknüpfung wird durch Speicherelemente (Latch, Flip-Flop) und kombinatorische Elemente (z.B. NAND) dargestellt.

- Es wird Rückkopplung benötigt.

Schaltnetz und Schaltwerk: Darstellungsarten

- Gleichung (Text)

- Blöcke, Schaltplan (schematic)

- Wahrheitstabelle, Zustandstabelle

- Zustandsdiagramm

- Zeitverhalten

- Textuelle Beschreibung: VHDL

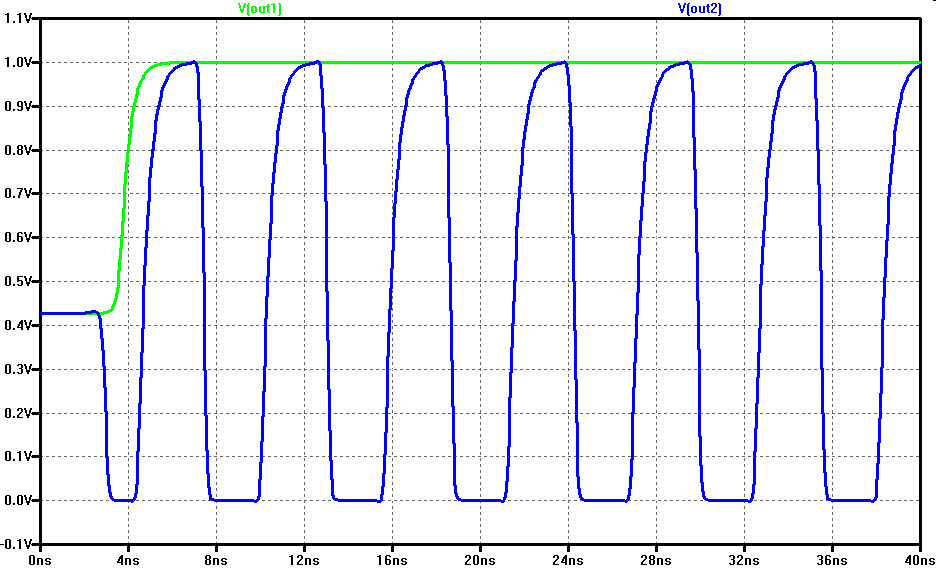

Schaltnetz und Schaltwerk: Zeitverhalten

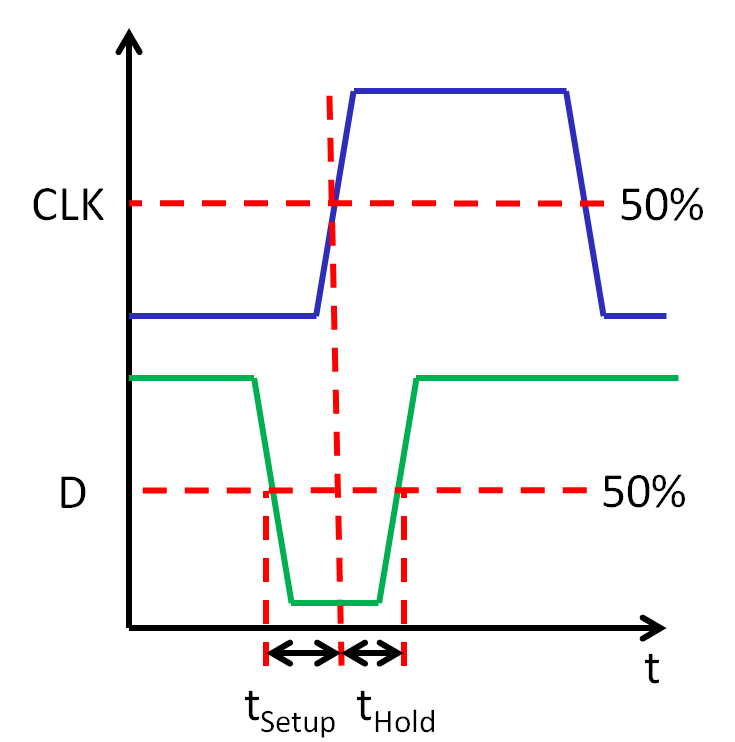

Schaltnetz:

Schaltwerk:

Ein Schaltwerk hat einen Zustand, der durch Eingangssignale verändert wird.

Fernbedienung Beamer: Einmal drücken bewirkt ein Einschalten des Beamers. Der gleiche Schalter wird wieder gedrückt und schaltet den Beamer aus.

Bei Schaltnetzen stellt dt die Verzögerungszeit (propagation delay) zwischen Ausgangssignal und Eingangssignal dar.

Bei Schaltwerken können die Zeiten tn Verzögerungszeiten oder Speicherglieder darstellen.

Bei Schaltwerken können die Zeiten tn Verzögerungszeiten oder Speicherglieder darstellen.

Schaltnetz und Schaltwerk: Beispiele

Schaltnetz

- Lichtschalter für eine Beleuchtung

- Joystick, Lenkrad, Bremse

- Lautstärkeregler

- Addierer, Komparator, Multiplizierer, Multiplexer

Schaltwerk

- Mehr als 2 Lichtschalter für eine Beleuchtung (Treppenhaus)

- Waschmaschinensteuerung

- Taschenrechner

- Uhr, Zähler

- Mikroprozessor, Speicher, Schieberegister, Seriell-Parallel-Wandler

Das einfachste Schaltwerk ein Speicherglied

Minimal Spezifikation:

Eine "0" oder eine "1" kann gespeichert, gelesen und gesetzt werden.

Übliche Spezifikation:

- Ein Takt (Clock, CLK) kontrolliert das Setzen ("1") oder Rücksetzen ("0") des Speichergliedes mit dem Eingang D.

- Das Speicherglied kann initialisiert werden (SET, RESET, CLR). Es gibt beim Einschalten einen sicheren Zustand.

- Ein Aktivierungssignal (enable) kontrolliert die Wirksamkeit des Taktsignals (CE enable).

Testspezifikation:

- Man kann ein Speicherglied in einen Testmodus versetzen (Test enable, TE).

- Es gibt eine separaten Testdaten Eingang (Test data in, TDI).

- Es gibt eine separaten Testdaten Ausgang (Test data out, TDO).

Grundschaltungen

|

Die Verbindung 2er Inverter mit einer Rückkopplung. Bei der Rückkopplung wird ein Ausgang als ein Eingangssignal verwendet. Je nach Rückkopplung können Speicher oder Oszillatoren entstehen. |

|

Grundschaltung eines Speichergliedes

|

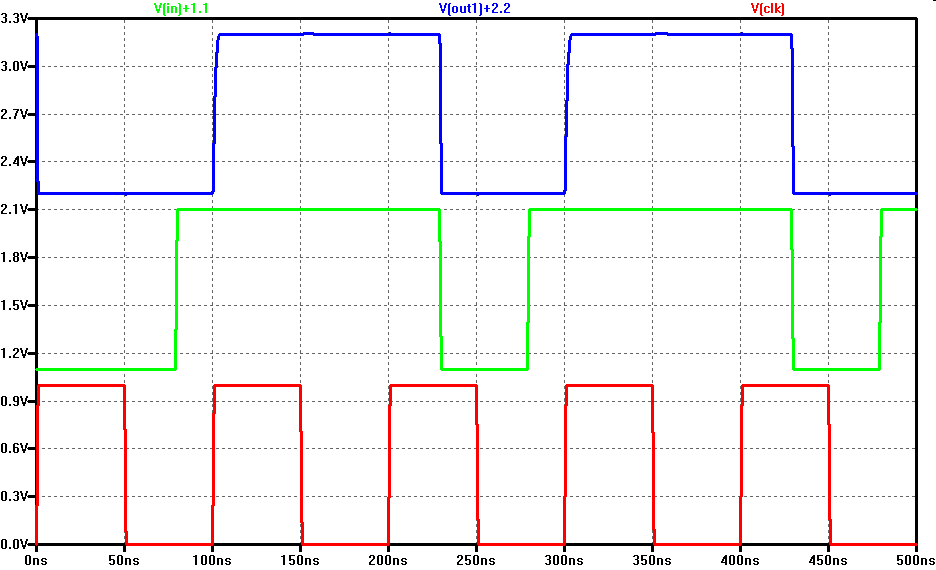

Speicherglied: Latch Ein Taktsignal (clock, CLK) steuert die Datenübernahme |

|

Wenn das CLK Signal "0" ist wird der Zustand des Speichergliedes gehalten.

Synchrone und Asynchrone Schaltungen

Es ist wünschenswert alle Speicherglieder mit einem Takt zu synchronisieren, um komplexe Schaltungen zu realisieren.Takt (Clock: C, CLK)

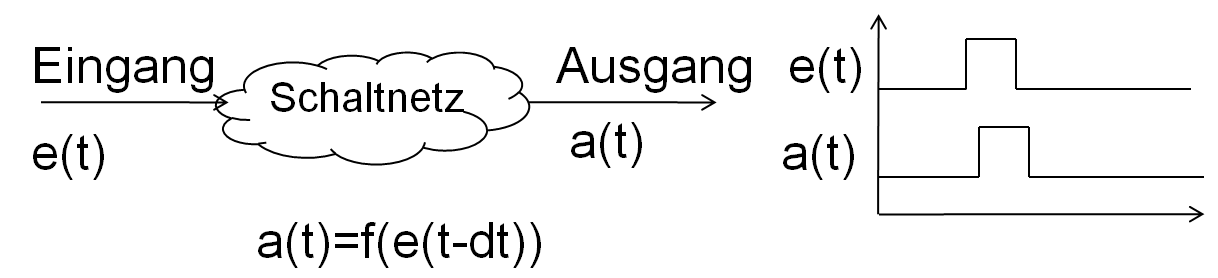

Positive Taktzustandssteuerung:

Während der Takt "1" ist kann der Zustand geändert werden.

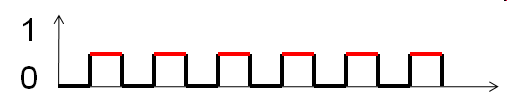

Positive Taktflankensteuerung:

Nur wenn der Takt von "0" auf "1" wechselt, kann der Zustand geändert werden.

Um unnötiges Schalten zu vermeiden, wird die Taktflankensteuerung eingesetzt.

Wahrheitstabelle der Flankensteuerung

Erweiterung durch X: Kann entweder 0 oder 1 sein. |

Zustandstabelle

Die Zustandstabelle ist erkennbar am Index: n+1 |

Die Zustandstabelle hat neben den Eingangs- und Ausgangssignalen auch Zustände.

Links stehen die Eingangssignale und die Zustände zum Taktzykuls n, Rechts stehen die Ausgangszustände zum Taktzyklus n+1.

Links stehen die Eingangssignale und die Zustände zum Taktzykuls n, Rechts stehen die Ausgangszustände zum Taktzyklus n+1.

Zustandstabelle eines 2-Bit Zählers

Der Zähler zählt hoch, wenn DOWN Null ist. Beim Hochzählen folgt der "11" eine "00", beim Runterzählen folgt der "00" eine "11". D-Flip-Flop

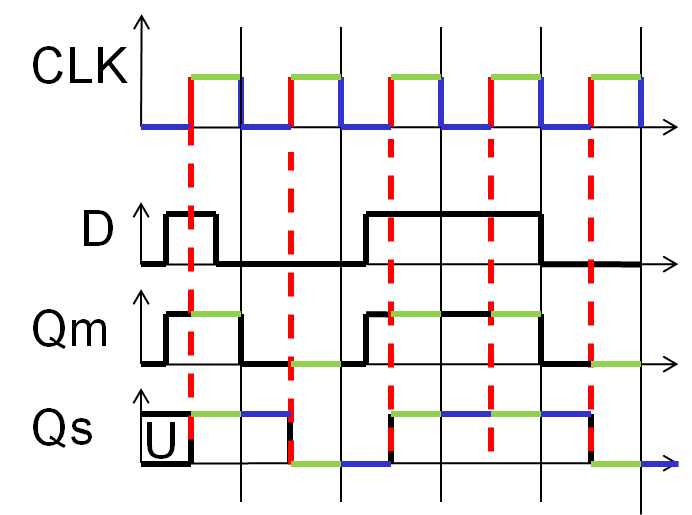

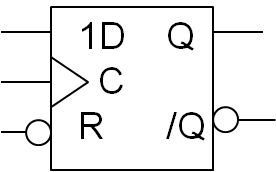

Realisierung der Flankensteuerung: Master Slave Flip Flop, D Flip Flop

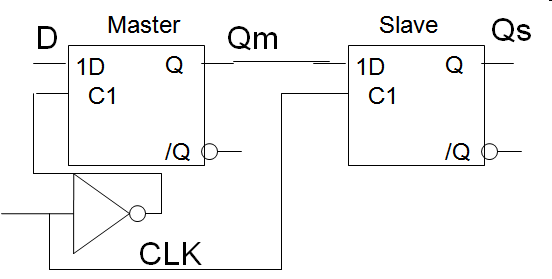

Ein Dreick am Eingang des Symbols bezeichnet eine Flankensteuerung. Setup und Hold Zeiten

\[ f_{max} = \frac{1}{T_{min}} \lt \frac{1}{t_{setup} + t_{DSpeicher} + t_{DLogik}} \] Praktische Realisierung eines Scan Flip Flops

In integrierten Schaltungen werden zur Testbarkeit D-Flip-Flops durch Scan Flip Flops ersetzt.

Alle Scan Flip-Flops werden zu einem Schieberegister verschaltet. Dabei wird der TDO-Ausgang eines Scan Flip Flops mit dem TDI Eingang des nächsten Flip Flops verschaltet. Damit ist es möglich alle Speicherelemente in einen beliebigen Zustand zu setzen (TE="1" und serielle Dateneingabe), eine logische Verknüpfung durchzuführen (TE="0", CLK rising) und dann das Ergebnis seriell auszulesen (TE="1").

Zusammenfassung und nächste Vorlesung

Nächstes Mal

Hochschule für angewandte Wissenschaften Kempten, Jörg Vollrath, Bahnhofstraße 61 · 87435 Kempten

Tel. 0831/25 23-0 · Fax 0831/25 23-104 · E-Mail: joerg.vollrath(at)fh-kempten.de Impressum

|