Elektronik16 MOSFETProf. Dr. J÷rg Vollrath15 Diode |

|

Video der 23. Vorlesung 11.1.2021

|

Lõnge: 00:00:00 |

0:0:0 Diode 0:5:0 Leuchtdioden, Gleichrichter, 0:6:15 MOSFET 4 Anschl³sse Gate, Drain, Source 0:7:40 Heute MOSFET 0:11:40 MOSFET Anschl³sse, NFET, PFET 0:15:45 CMOS Transistoren als Schalter 0:17:45 Gleichungen des NFET 0:22:45 Wichtige Kenngr÷▀en 0:28:0 Kennlinien 0:33:21 Parameterextraktion MOSFET 0:36:12 Bestimmung der Transistorparameter 0:40:10 Wurzel IDS, Steigung Wurzel beta, Achsenabschnitt Uth 0:44:28 MOSFET Transistor als Diode 0:46:50 Beispiel NMOSFET Transistor 0:52:43 Kapazitõten elektronischer Bauelemente 0:55:9 LTSPICE MOSFET Modell 0:57:3 LTSPICE Modellkarte 0:58:30 Transistorentwicklung 1:3:10 MOSFET als Verstõrker 1:11:8 Kleinere ─nderungen, Linearisierung 1:12:12 Gro▀signalverhalten und Kleinsignalverhalten 1:16:45 Kleinsignalersatzschaltbild 1:19:50 Kleinsignalverhalten: Ausgangsleitwert 1:21:50 Warum habe ich einen Verstõrker? |

Heute

|

|

|

2N7000, FDG6320C, 3N1637 |

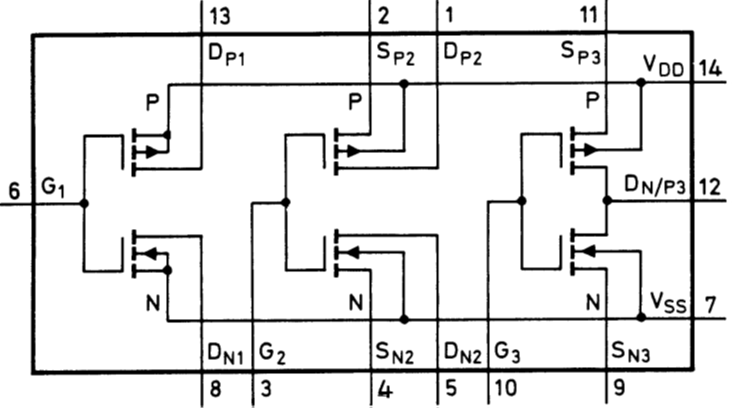

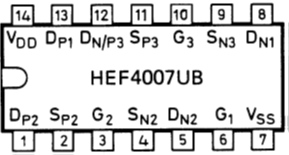

CD4007, ALD110 |

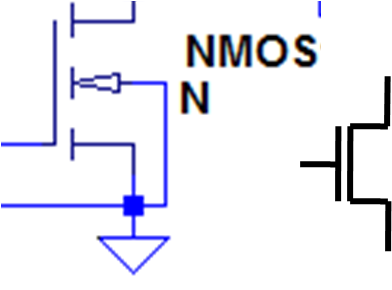

MOSFET

|

CMOS Transistoren als Schalter

| Symbol | Eingang: Gate | |||

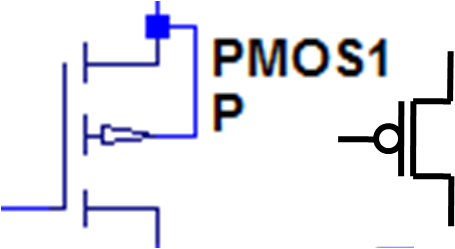

PFET Transistor:

|

| 0

| 1

| |

NFET Transistor:

|

| 0

| 1

| |

Zur Realisierung von booleschen Funktionen werden MOSFET (metal oxide semiconductor field effect transistor)

Transistoren eingesetzt.

Dabei werden Halbleiter (semiconductor, Silizium) verwendet, bei denen man durch Einbringen von Femdatomen (Dotierung) die Leitfõhigkeit (Elektronen, L÷cher) verõndern kann.

Der MOS Transistor hat drei Anschl³sse Gate, Drain und Source.

Das Gate ist der Eingang. An der Drain ist der Ausgang und an der Source ist VDD (Betriebsspannnung, PFET) oder GND (0 V, NFET).

FET Feldeffekttransistor ist der ▄berbegriff f³r Halbleiterbaulemente, bei denen das elektrische Feld zwischen Gate und Kanal den Kanalwiderstand steuert bzw die Verbindung zwischen Drain und Source trennt oder schliesst.

Es gibt PFETs (PMOSFETs, L÷cherleitung, positive Ladungstrõger, L÷cher) und NFETs (NMOSFETs, negative Ladungstrõger, Elektronen) deren Verhalten komplementõr sind (complementary metal oxide semiconductors, CMOS).

Ist die Gatesourcespannung beim NFET positiv, gr÷▀er als eine Schwellspannung (threshold voltage), wird die Verbindung zwischen Drain und Source leitend (Ein Schalter wird geschlossen).

Ist die Gatesourcespannung beim PFET negativ, kleiner als eine Schwellspannung, wird die Verbindung zwischen Drain und Source leitend (Ein Schalter wird geschlossen).

Durch geschicktes Kombinieren der Transistoren k÷nnen Logikfunktionen technisch realisiert werden.

Fast alle modernen Mikroprozessoren und digitalen Schaltungen werden mit CMOS Transistoren realisiert.

Dabei werden Halbleiter (semiconductor, Silizium) verwendet, bei denen man durch Einbringen von Femdatomen (Dotierung) die Leitfõhigkeit (Elektronen, L÷cher) verõndern kann.

Der MOS Transistor hat drei Anschl³sse Gate, Drain und Source.

Das Gate ist der Eingang. An der Drain ist der Ausgang und an der Source ist VDD (Betriebsspannnung, PFET) oder GND (0 V, NFET).

FET Feldeffekttransistor ist der ▄berbegriff f³r Halbleiterbaulemente, bei denen das elektrische Feld zwischen Gate und Kanal den Kanalwiderstand steuert bzw die Verbindung zwischen Drain und Source trennt oder schliesst.

Es gibt PFETs (PMOSFETs, L÷cherleitung, positive Ladungstrõger, L÷cher) und NFETs (NMOSFETs, negative Ladungstrõger, Elektronen) deren Verhalten komplementõr sind (complementary metal oxide semiconductors, CMOS).

Ist die Gatesourcespannung beim NFET positiv, gr÷▀er als eine Schwellspannung (threshold voltage), wird die Verbindung zwischen Drain und Source leitend (Ein Schalter wird geschlossen).

Ist die Gatesourcespannung beim PFET negativ, kleiner als eine Schwellspannung, wird die Verbindung zwischen Drain und Source leitend (Ein Schalter wird geschlossen).

Durch geschicktes Kombinieren der Transistoren k÷nnen Logikfunktionen technisch realisiert werden.

Fast alle modernen Mikroprozessoren und digitalen Schaltungen werden mit CMOS Transistoren realisiert.

Typen des Feldeffekttransistors

- Isolation

- Dielektrisch: MOSFET, MISFET, IGFET

- Gesperrter pn-▄bergang: Sperrschicht-FET, JFET, MESFET

- Die Schwellspannung des Gate

- Selbstleitender FET: Depletion FET

- Bei der Gatespannung UGS=0V ist ein leitender Kanal vorhanden

- Selbstsperrender FET: Enhancement FET

- Bei der Gatespannung UGS=0V ist kein leitender Kanal vorhanden

- Kanalart

- p-leitender Kanal PFET

- n-leitender Kanal: NFET

Die Gleichung des n-Kanal MOSFETs

|

\( I_{DS} = \cases{ 0 & \text{ Sperrbereich } \cr \text{ f³r } U_{GS} \leq U_{th} \cr \cr

\beta \left( U_{GS}-U_{th} \right)^2 \left( 1+\lambda U_{DS} \right) & \text{ Sõttigung}

\cr \text{ f³r } 0 \leq U_{GS} - U_{th} \lt U_{DS} \cr \cr

\beta \left( 2 \left( U_{GS}-U_{th} \right) U_{DS} - U_{DS}^2 \right) & \text{ Triodenbereich}

\cr \text{ f³r } 0\leq U_{GS} - U_{th} \geq U_{DS}

}

\) \( \beta = \frac{\mu_n \epsilon_{ox}}{2d_{ox}} \frac{W}{L} = \frac{1}{2} \mu_n C_{ox}^{'} \frac{W}{L} = \frac{1}{2} K_{n}^{'} \frac{W}{L} = \frac{1}{2} K_{n} = \frac{1}{2} KP \) |

|

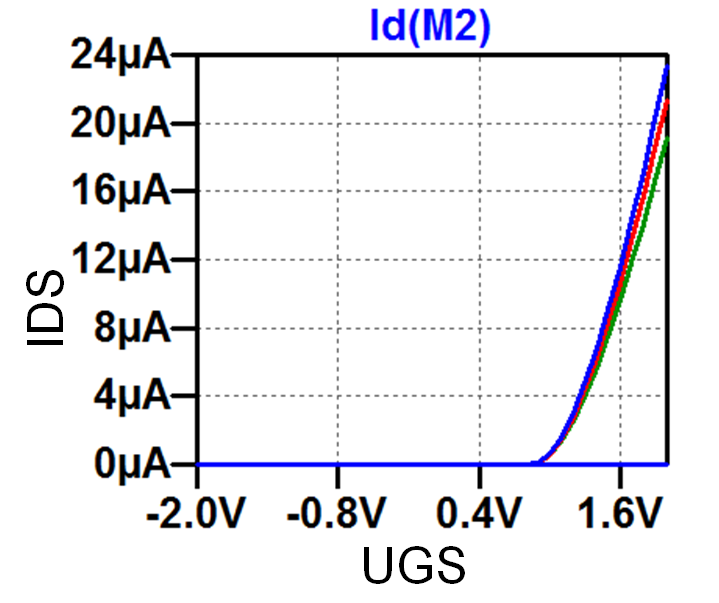

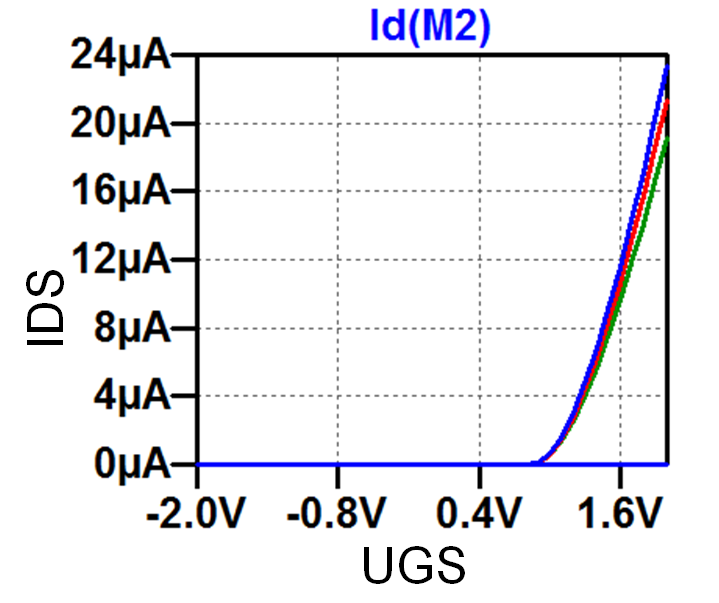

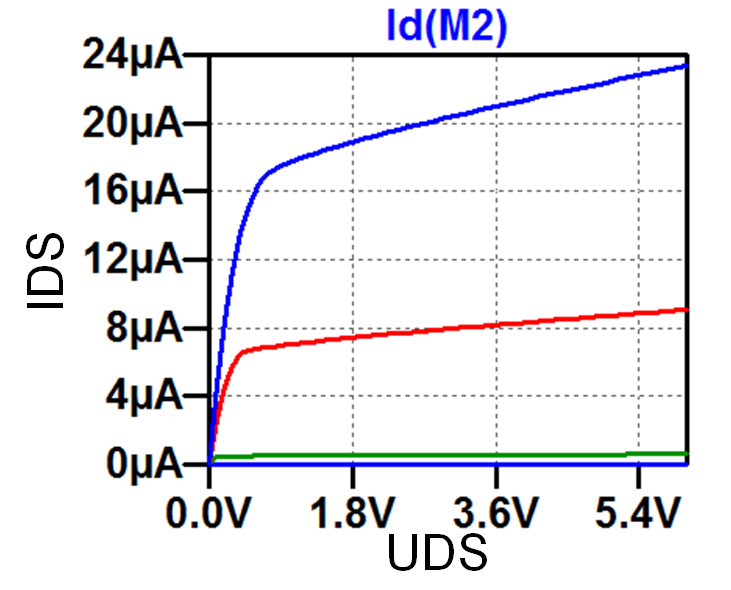

▄bertragungs- kennlinie |

Quelle Vollrath

Quelle Vollrath |

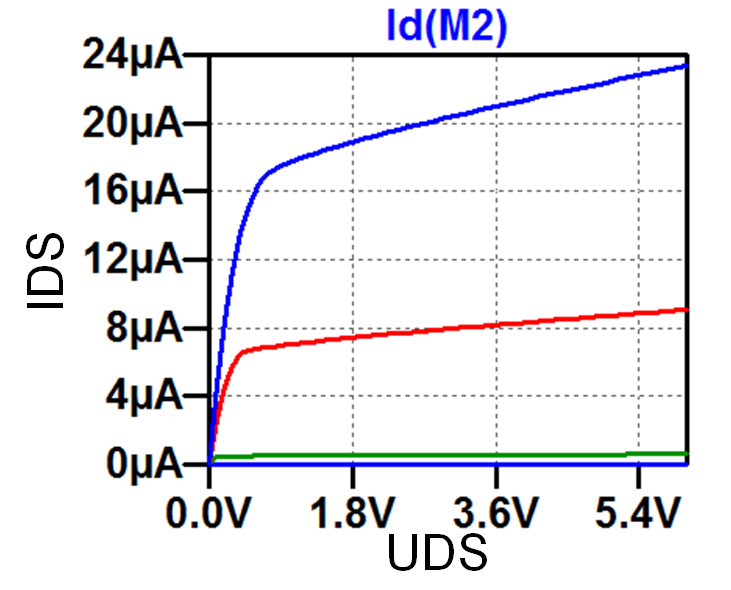

Ausgangs- kennlinie |

Quelle Vollrath

Quelle Vollrath |

Wichtige Kenngr÷▀en

- Uth : Schwellspannung [V]

- β : Steilheitsparameter [A V-2]

- \( \mu_n \): Beweglichkeit (NFET)

- Oxidkapazitõt pro Flõche \( C_{ox}^{'}=\frac{\epsilon_{ox}}{2d_{ox}} \)

- W: Transistorweite

- L: Transistorlõnge

- λ : Kanallõngenmodulation [V-1]

- Integrierte Schaltungen

- W und L werden vom Schaltungsentwickler bestimmt (gezeichnet)

- Cox: wird durch die Technologie bestimmt

SPICE:

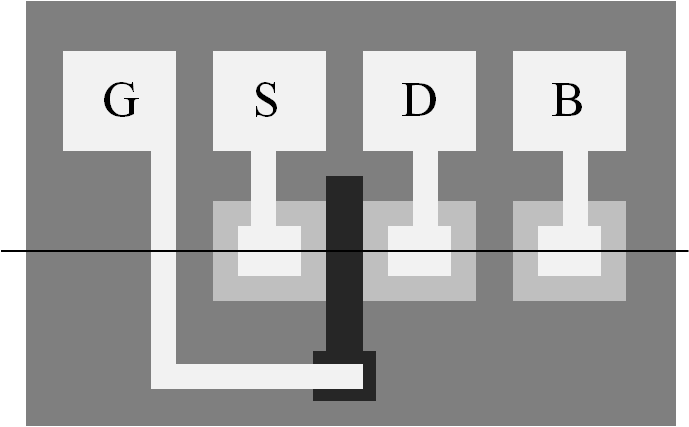

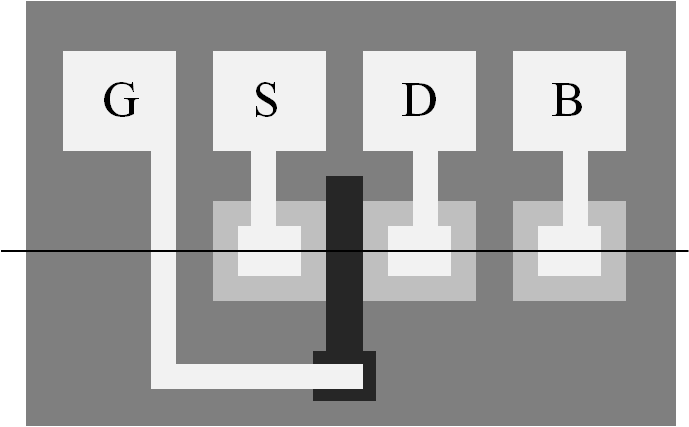

M2 0 N001 N002 0 P_1u l=1u w=1u

SPICE:

Mxxx Nd Ng Ns Nb <model> [m=<value>] [L=<len>] [W=<width>]

Anschl³sse, Knoten, Geometrie

m: Anzahl Transistoren in Parallelschaltung

Mxxx Nd Ng Ns Nb <model> [m=<value>] [L=<len>] [W=<width>]

Anschl³sse, Knoten, Geometrie

m: Anzahl Transistoren in Parallelschaltung

Kennlinien:

▄bertragungskennlinie Quelle Vollrath

Quelle Vollrath |

Ausgangskennlinie Quelle Vollrath

Quelle Vollrath |

Beispiel: NMOSFET-Transistor

Berechnen Sie den Drain Source Strom f³r einen NMOS Transistor mit UGS=5V, UDS=10V, Uth=1V, Kn=1mA/V2 und \( \lambda =0.02V^{-1} \).In welchem Arbeitsbereich befindet sich der Transistor?

\( U_{DS} > U_{GS} - U_{th} Sõttigung \)

\( I_{DS}= \beta \left(U_{GS} - U_{th}\right)^2 \left( 1+ \lambda U_{DS} \right) \)

\( I_{DS}= \frac{1}{2} K_n\left(U_{GS} - U_{th}\right)^2 \left( 1+ \lambda U_{DS} \right) \)

\( I_{DS} = \frac{1mA}{2V^2} \left(5V - 1V\right)^2 \left( 1+ 0.02 V^{-1} 10V \right) \)

\( I_{DS}= \frac{1}{2} 16 \cdot 1.2mA=9.6mA \)

\( I_{DS}= \beta \left(U_{GS} - U_{th}\right)^2 \left( 1+ \lambda U_{DS} \right) \)

\( I_{DS}= \frac{1}{2} K_n\left(U_{GS} - U_{th}\right)^2 \left( 1+ \lambda U_{DS} \right) \)

\( I_{DS} = \frac{1mA}{2V^2} \left(5V - 1V\right)^2 \left( 1+ 0.02 V^{-1} 10V \right) \)

\( I_{DS}= \frac{1}{2} 16 \cdot 1.2mA=9.6mA \)

Beispiel: MOSFET Bauteil und Kennlinie

An einem MOSFET messen Sie bei einer Gate-Sourcespannung von 2V bei UDS=3V IDS=4mA und bei UDS=5V IDS=4.4mA. Bei UGS=1.5V und UDS=3V messen Sie IDS=1mA.Berechnen Sie \( \lambda \) , Vth und KN.

3 Gleichungen, 3 Unbekannte. Der Arbeitsbereich bestimmt welche Gleichung man verwenden muss.

\( I_{DS}= \beta \left( U_{GS}-U_{th} \right)^2 \left( 1+\lambda U_{DS} \right) \) |

Mit UGS1 = UGS2 \( \frac{I_{DS1}}{I_{DS2}}= \frac{ \left( 1+\lambda U_{DS1} \right)}{\left( 1+\lambda U_{DS2} \right)} \) \( \left( 1+\lambda U_{DS2} \right) \frac{I_{DS1}}{I_{DS2}}= 1+\lambda U_{DS1} \) \( \lambda \left( U_{DS2} \frac{I_{DS1}}{I_{DS2}} - U_{DS1} \right) = 1- \frac{I_{DS1}}{I_{DS2}} \) \( \lambda =\frac{ 1- \frac{I_{DS1}}{I_{DS2}} }{U_{DS2} \frac{I_{DS1}}{I_{DS2}} - U_{DS1}} = \frac{ 1- \frac{4}{4.4} }{5 \frac{4}{4.4} - 3} V^{-1} =\frac{1}{11} \frac{11}{17} V^{-1} \) \( =\frac{1}{17} V^{-1} = 0.06 V^{-1} \) |

3 Gleichungen, 3 Unbekannte. Der Arbeitsbereich bestimmt welche Gleichung man verwenden muss.

\( I_{DS}= \beta \left( U_{GS}-U_{th} \right)^2 \left( 1+\lambda U_{DS} \right) \) \( \lambda =0.06 V^{-1} \) |

Mit UDS1 = UDS3 = konst \( \frac{I_{DS1}}{I_{DS3}}= \frac{ \left( U_{GS1}-U_{th} \right)^2}{\left( U_{GS3}-U_{th} \right)^2} \) \( \sqrt{\frac{I_{DS1}}{I_{DS3}}}= \frac{ U_{GS1}-U_{th} }{U_{GS3}-U_{th}} \) \( \left( U_{GS3}-U_{th} \right) \sqrt{\frac{I_{DS1}}{I_{DS3}}}= U_{GS1}-U_{th} \) \( U_{th} \left( 1-\sqrt{\frac{I_{DS1}}{I_{DS3}}} \right) = U_{GS1}- U_{GS3} \sqrt{\frac{I_{DS1}}{I_{DS3}}} \) \( U_{th} = \frac {U_{GS1}- U_{GS3} \sqrt{\frac{I_{DS1}}{I_{DS3}}}}{1-\sqrt{\frac{I_{DS1}}{I_{DS3}}}} = \frac{ 2V -1.5V \cdot 2}{1-2}=1V \) |

3 Gleichungen, 3 Unbekannte. Der Arbeitsbereich bestimmt welche Gleichung man verwenden muss.

Der Transistor ist immer im Sõttigungsbereich.

Der Transistor ist immer im Sõttigungsbereich.

\( \lambda = 0.06 V^{-1} \) \( U_{th} = 1 V \) |

\( \beta = \frac{I_{DS}}{\left( U_{GS}-U_{th} \right)^2 \left( 1+\lambda U_{DS} \right)}

\) \( \beta = \frac{4mA}{\left( 2V-1V \right)^2 \left( 1+0.06 \cdot 3V \right)} = \frac{4}{1.18} \frac{mA}{V^2} = 3.39 \frac{mA}{V^2} \) \( K_N = 2 \cdot \beta = 6.78 \frac{mA}{V^2} \) |

MOSFET Parameterextraktion

Extraktion aus Messpunkten im Sõttigungsbereich:\( U_{GS} = const \); \( U_{DS1}, U_{DS2} \rightarrow \frac{I_{DS1}}{I_{DS2}} \rightarrow \lambda \)

\( U_{DS} = const \); \( U_{GS1}, U_{GS2} \rightarrow \frac{I_{DS1}}{I_{DS2}} \rightarrow U_{th} \)

\( \beta \)

Auftragung der Messwerte als lineare Funktion:

\( y = \sqrt{I_{DS}} = \sqrt{\beta} \left( U_{GS} - U_{th} \right) \sqrt{\left( 1 + \lambda U_{DS} \right)} \)

\( y = \sqrt{\beta \left( 1 + \lambda U_{DS} \right)} U_{GS} - \sqrt{\beta \left( 1 + \lambda U_{DS} \right)} U_{th} \)

\( x = U_{GS} \), \( a = \sqrt{\beta \left( 1 + \lambda U_{DS} \right) } \) , \( b = - \sqrt{\beta \left( 1 + \lambda U_{DS} \right)} U_{th} = - a \cdot U_{th} \)

\( y = ax + b \)

1. Mathematische Methode:

Bei 2 Messungen bei gleicher Spannung UGS und unterschiedlicher Spannnung UDS im Sõttigungsbereich erhõlt man aus dem Verhõltnis der Str÷me λ.

Bei 2 Messungen bei gleicher Spannung UDS und unterschiedlicher Spannnung UGS im Sõttigungsbereich erhõlt man aus dem Verhõltnis der Str÷me Uth.

β kann man dann aus einer Messung durch einsetzen von IDS, Uth, λ und UGS berechnen.

2. Methode durch grafische Interpretation

Bei 2 Messungen bei gleicher Spannung UGS im Sõttigungsbereich erhõlt man aus dem Verhõltnis der Str÷me λ. Trõgt man die Wurzel des Stromes IDS ³ber der Gate-Source-Spannung auf ergibt sich eine Geradengleichung.

Aus der Steigung dieser Geraden und dem y-Achsenabschnitt bei x = UGS0 ergeben sich Uth und bei kleinem λ und Vernachlõssigung von λ UDS gegen³ber 1 dann β.

NMOSFET SPICE Modell

|

Typische Werte \( KP = 20..50 \mu A /V^2 \) KP = KN = 2 · β λ = 0 \( V_{th} = 1V \) \( C_{GD0} = C_{GS0} = 0 F \) \( C_{GB0} =C_{JSW} = 0 F \) LEVEL = 1 einfache Gleichungen .model Ntyp NMOS(LEVEL=1 KP=50u VT0=1 LAMBDA=0.002 + CGSO=45n CGBO=2n CGDO=45n) CD4007.model CD4007N NMOS(LEVEL=1 KP=500u VT0=1 LAMBDA=0.002+ CGSO=45n CGBO=2n CGDO=45n) |

SPICE MOS Modell

.model AO6407 VDMOS(pchan Rg=3 Rd=14m Rs=10m + Vto=-.8 Kp=32 Cgdmax=.5n Cgdmin=.07n Cgs=.9n + Cjo=.26n Is=26p Rb=17m mfg=Alpha_&_Omega + Vds=-20 Ron=34m Qg=13n)

.MODEL N_1u NMOS LEVEL = 3 + TOX = 200E-10 NSUB = 1E17 GAMMA = 0.5 + PHI = 0.7 VTO = 0.8 DELTA = 3.0 + UO = 650 ETA = 3.0E-6 THETA = 0.1 + KP = 120E-6 VMAX = 1E5 KAPPA = 0.3 + RSH = 0 NFS = 1E12 TPG = 1 + XJ = 500E-9 LD = 100E-9 + CGDO = 200E-12 CGSO = 200E-12 CGBO = 1E-10 + CJ = 400E-6 PB = 1 MJ = 0.5 + CJSW = 300E-12 MJSW = 0.5 *Weitere Modelle finden sich im Internet:

Baker: 1 µm MOSFET model, 50 nm MOSFET model,

cmosedu_models.txt

Sedra Smith Level=1 5 µm, 0.5 µm: sedra_lib.lib

Allen, Holberg Level=3 0.8 µm: Holberg.txt

TSMC 0.25um CMOS MOSFETs (level 3) t14y_tsmc_025_level3.lib from MOSIS .

ALD1101, ALD1102, David A. Johns University of Toronto

.model CD4007P PMOS(LEVEL=1 KP=500u VT0=-1 LAMBDA=0.002 CGSO=45n CGBO=2n CGDO=45n)

.model ALD1107P PMOS(LEVEL=1 KP=0.2m VT0=-0.7 LAMBDA=0.018 CGDO=100n CGSO=100n)

* This model was extracted from measurements.

* The model is correct only for W = 1738 um and L = 1 um.

* The device size above doesn't represent the actual device size.

* NMOS hand analysis values: Vtn = 0.71 V; UnCox(W/L) = 4.5 mA/V^2 ; VA = 80 V;

.MODEL ALD1101 NMOS LEVEL = 2 UO = 12.72 VTO = 0.6766 NFS = 1.154E12 TOX = 1E-08 NSUB = 3.892E17 UCRIT = 4.582E05 UEXP = 0.07025 VMAX = 6363 RS = 9.491 RD = 5.659 XJ = 4.787E-09 LD = 0 DELTA = 1E-12 NEFF = 0.8345 NSS = -3.801 CGSO = 1.15E-9 CGDO = 1.15E-9 CGBO = 0 CBD = 0 CBS = 0 CJ = 0 MJ = 0.5 CJSW = 0 MJSW = 0.6057 IS = 1.0E-14 PB = 0.8 FC = 0.5 NEFF=5

* PMOS hand analysis values: Vtn = -0.65 V; UpCox(W/L) = 2.10 mA/V^2 ; VA = -19 V;

.MODEL ALD1102 PMOS LEVEL = 2 UO = 5.536 VTO = -0.6093 NFS = 3.602E12 TOX = 1E-08 NSUB = 4.046E16 UCRIT = 8.118E04 UEXP = 0.1647 VMAX = 1399 RS = 9.249 RD = 38.77 XJ = 4.443E-09 LD = 0 DELTA = 8828 NEFF = 2.145 NSS = -8.793 CGSO = 1.15E-9 CGDO = 1.15E-9 CGBO = 0 CBD = 0 CBS = 0 CJ = 0 MJ = 0.5 CJSW = 0 MJSW = 0.33 IS = 1E-14 PB = 0.8 FC = 0.5

Sedra Smith Level=1 5 µm, 0.5 µm: sedra_lib.lib

Allen, Holberg Level=3 0.8 µm: Holberg.txt

TSMC 0.25um CMOS MOSFETs (level 3) t14y_tsmc_025_level3.lib from MOSIS .

ALD1101, ALD1102, David A. Johns University of Toronto

CD4007

.model CD4007N NMOS(LEVEL=1 KP=500u VT0=1 LAMBDA=0.002 CGSO=45n CGBO=2n CGDO=45n).model CD4007P PMOS(LEVEL=1 KP=500u VT0=-1 LAMBDA=0.002 CGSO=45n CGBO=2n CGDO=45n)

ALD1106, ALD1107

.model ALD1106N NMOS(LEVEL=1 KP=0.48m VT0=0.7 LAMBDA=0.018 CGDO=100n CGSO=100n).model ALD1107P PMOS(LEVEL=1 KP=0.2m VT0=-0.7 LAMBDA=0.018 CGDO=100n CGSO=100n)

ALD1101, ALD1102

* ALD ALD1101 (NMOS) and ALD 1102 (NMOS) model* This model was extracted from measurements.

* The model is correct only for W = 1738 um and L = 1 um.

* The device size above doesn't represent the actual device size.

* NMOS hand analysis values: Vtn = 0.71 V; UnCox(W/L) = 4.5 mA/V^2 ; VA = 80 V;

.MODEL ALD1101 NMOS LEVEL = 2 UO = 12.72 VTO = 0.6766 NFS = 1.154E12 TOX = 1E-08 NSUB = 3.892E17 UCRIT = 4.582E05 UEXP = 0.07025 VMAX = 6363 RS = 9.491 RD = 5.659 XJ = 4.787E-09 LD = 0 DELTA = 1E-12 NEFF = 0.8345 NSS = -3.801 CGSO = 1.15E-9 CGDO = 1.15E-9 CGBO = 0 CBD = 0 CBS = 0 CJ = 0 MJ = 0.5 CJSW = 0 MJSW = 0.6057 IS = 1.0E-14 PB = 0.8 FC = 0.5 NEFF=5

* PMOS hand analysis values: Vtn = -0.65 V; UpCox(W/L) = 2.10 mA/V^2 ; VA = -19 V;

.MODEL ALD1102 PMOS LEVEL = 2 UO = 5.536 VTO = -0.6093 NFS = 3.602E12 TOX = 1E-08 NSUB = 4.046E16 UCRIT = 8.118E04 UEXP = 0.1647 VMAX = 1399 RS = 9.249 RD = 38.77 XJ = 4.443E-09 LD = 0 DELTA = 8828 NEFF = 2.145 NSS = -8.793 CGSO = 1.15E-9 CGDO = 1.15E-9 CGBO = 0 CBD = 0 CBS = 0 CJ = 0 MJ = 0.5 CJSW = 0 MJSW = 0.33 IS = 1E-14 PB = 0.8 FC = 0.5

CMOS 1µm models (Holberg)

** Holberg, p 337 Table6.6-1 .model NMOS1 NMOS(LEVEL=1 VT0=0.70 KP = 110U GAMMA = 0.4 LAMBDA = 0.04 PHI = 0.7 MJ = 0.5 + MJSW = 0.38 CGBO =700P CGSO=220P CGDO = 220P CJ = 770U CJSW = 380P LD = 0.016U TOX= 14N) .model PMOS1 PMOS (LEVEL=1 VT0 = -0.70 KP = 50U GAMMA = 0.57 LAMBDA = 0.05 PHI = 0.8 MJ = 0.5 + MJSW = 0.35 CGBO =700P CGSO=220P CGDO = 220P CJ = 560U CJSW = 350P LD = 0.014U TOX= 14N)

Transistorentwicklung

|

1970 8 µm 1980 2 \( \mu m \) 1990 0.5 \( \mu m \) 2000 130 \( nm \) 2010 40 \( nm \) 2013 22 \( nm \) 2015 14 \( nm \) 2020 5 \( nm \)  Jahr und Strukturgr÷▀e |

MOSFET als Verstõrker: Das Prinzip

|

Wenn der MOSFET als Verstõrker betrieben wird, betrachtet man nur das Verhalten in der Sõttigung.

MOSFET als Verstõrker: Die Kennlinie (2.12.2025)

\( U_{a}= U_{DD} - \beta \left( U_{GS}-U_{th} \right)^2 \left( 1+\lambda U_{DS} \right) \cdot R_{D} \)|

die mit RD in eine Ausgangsspannung umgesetzt wird. \( \lambda = 0.01 V^{-1} \), \( R_{D} = 10 k\Omega \) Arbeitspunkt: UGS=2.5V \( \Delta U_{GS} = 2.5 V (+-0.5V) \) \( \Delta I_{DS} = 0.5 mA - 0.1 mA = - 0.4 mA \) \( \Delta U_{DS} = 4 V - 8 V = -4 V \) Spannngsverstõrkung: vU = -4V/1V = -4 |

Ausgangskennlinie |

Die Ausgangskennlinie und die Lastkennlinie des Widerstands wird dargestellt.

Der Strom des Widerstandes wird f³r verschiedene UDS aufgetragen.

F³r UDS = VDD = 9V liegt keine Spannungsdifferenz am Widerstand und der Strom durch den Widerstand wõre 0 A.

F³r UDS = 0 V liegen 9V am Widerstand an und der Strom ist IR = VDD/RD.

Dort wo die Widerstandsgerade die Ausgnagskennlinie schneidet (rote Markierungen) liegen die m÷glichen Arbeitspunkte.

Der Strom des Widerstandes wird f³r verschiedene UDS aufgetragen.

F³r UDS = VDD = 9V liegt keine Spannungsdifferenz am Widerstand und der Strom durch den Widerstand wõre 0 A.

F³r UDS = 0 V liegen 9V am Widerstand an und der Strom ist IR = VDD/RD.

Dort wo die Widerstandsgerade die Ausgnagskennlinie schneidet (rote Markierungen) liegen die m÷glichen Arbeitspunkte.

Gro▀signalverhalten und Kleinsignalverhalten

\( \text{f³r} 0 \leq U_{GS} - U_{th} \lt U_{DS} \text{Sõttigung} \) \( \frac{dI_{DS}}{dU_{GS}}= \frac{ d \beta \left( U_{GS}-U_{th} \right)^2 \left( 1+\lambda U_{DS} \right)} { dU_{GS}} \) \( \frac{dI_{DS}}{dU_{GS}} = 2 \beta \left( U_{GS}-U_{th} \right) \left( 1+\lambda U_{DS} \right) \) \( \frac{dI_{DS}}{dU_{GS}} = 2 \frac{I_{DS}}{U_{GS}-U_{th}} \) AC Analysis |

|

Kleinsignalverhalten

\( g_m = 2 \beta \left( U_{GS}-U_{th} \right) \left( 1+\lambda U_{DS} \right) \)

|

|

Lernziele

- Sie kennen das Schaltsymbol, die Gleichungen und ein einfaches Modell eines MOS Transistors

- Sie k÷nnen die Parameter eines MOS Transistors bestimmen

- Sie k÷nnen einen MOSFET als Verstõrker oder Schalter verwenden