Elektronik Projektpraktikum Ringoszillator

Autor: Jörg Vollrath, 2020

Aufgabenstellung: Ein Ringoszillator mit einer Schwingfrequenz von 1 MHz bei 5 V Betriebsspannung soll

aufgebaut werden.

Abstract

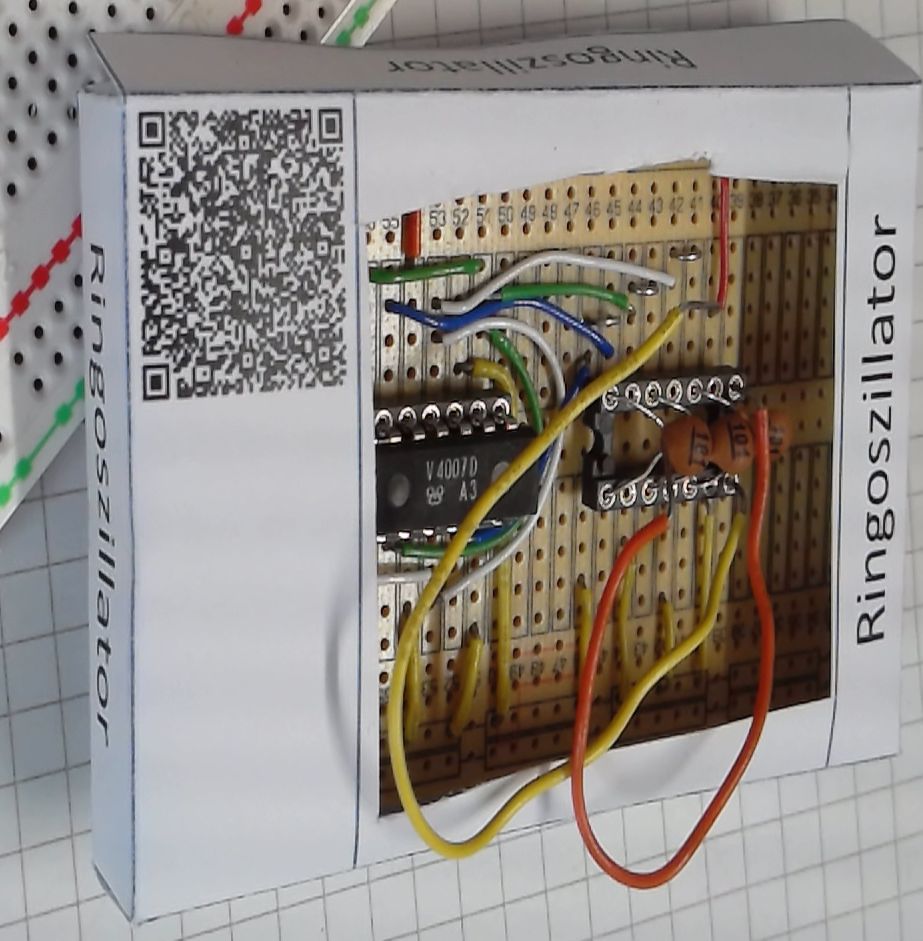

Mit einem CD4007 Baustein wurde ein Ringoszillator für 5V Betriebsspannung und 1 MHz Frequenz entwickelt.

Die theoretisch Formel für die Schwingfrequenz wurde mit Hilfe gemessener CMOS Transistorparameter ausgewertet

und mit einer LTSPICE simulation und verschiedenen Messungen an der aufgebauten

Schaltung verglichen. Die Leistungsaufnahme bei einer Spannung von 5.5V und einer Schwingfrequenz von 1.1 MHz

betrug bei Raumtemperatur 25 mW.

Die Schaltung wurde mit vorgesehenen Testpunkten in ein beschriftetes Gehäuse eingebaut.

Inhaltsverzeichnis

| | |

+ Bauteilliste

- Bauteilliste

Conrad, Digikey, Reichelt, Mouser

| Artikel | Distributer | Bestellnr | Preis |

Bild | Datenblatt |

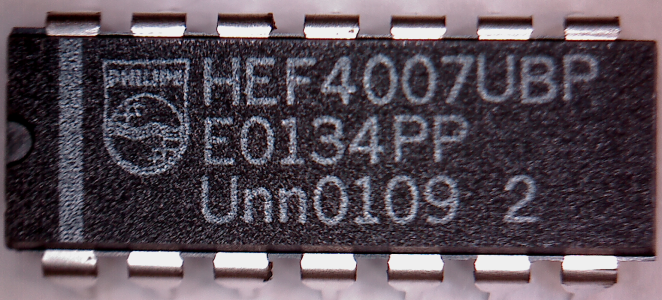

| CD4007UBE, DIP Package, Aktiv, Texas Instiuments | Digikey | 296-3501-5-ND |

0.40 |  |

CD4007 |

| Kapaziäten 100 pF, 150 pF, 200 pF | | |

| |

|

| 14 pin DIL Sockel | | |

| |

|

| Verbindungsdrähte | | |

| |

|

| Lochrasterplatine | | |

| |

|

+ Ausstattung und Messgeräte

- Ausstattung und Messgeräte

- Electronic Explorer: Power supply, function generator, oscilloscope

- LTSPICE: circuit simulation software

- Soldering station

+ Einführung: Die Schaltung Ringoszillator

- Einführung: Die Schaltung Ringoszillator

Im

Script Elektronik findet

man den LTSPICE Schaltplan und eine Simulation für einen Ringoszillator.

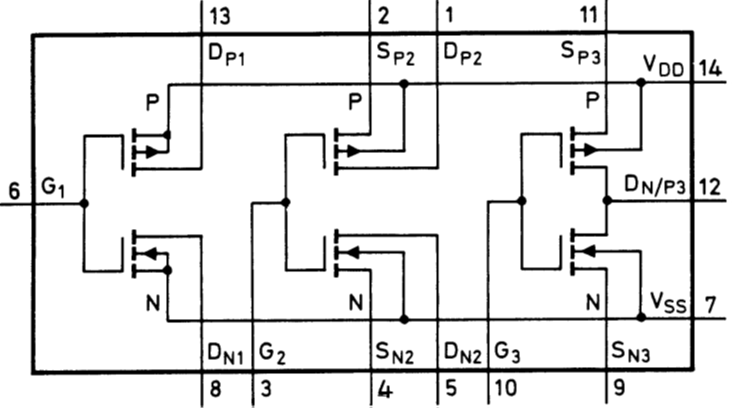

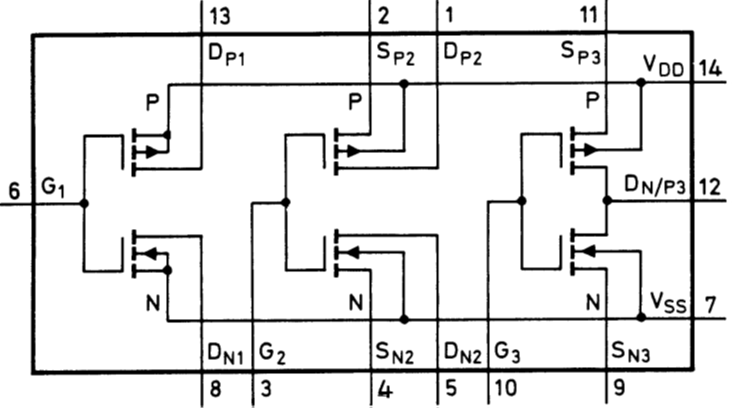

Drei CMOS Inverter sind in Reihe geschaltet. Der Ausgang des letzten Inverters wird mit

dem Eingang des ersten Inverters verbunden.

In diesem Projekt soll mit diesem Schaltplan ein Ringoszillator mit f = 1 MHz bei VDD = 5 V

aufgebaut werden und die Frequenz und Leistungsaufnahme in Abhängigkeit der

externen Spannung und zusätzlicher Kapazitäten beschrieben, gemessen und dokumentiert werden.

Man startet mit der Theorie und vergleicht diese mit der Simulation. Nach der Auswahl der Bauteile

mit dem Datenblatt wird die Schaltung mit den entsprechenden Modellen simuliert, aufgebaut,

gemessen und dokumentiert.

Man zerlegt die Schaltung in Bauelemente oder Teilschaltungen: Transistoren und Inverter und

beschreibt diese mathematisch, simuliert und charakterisiert diese.

Theorie

Nach

Wikipedia, Ringoszillator

ergibt sich für die Schwingungsdauer:

\( T = 2 \cdot n \cdot t_D = \frac{1}{f} \)

mit n: Anzahl der Inverter und t

D der Laufzeit (Verzögerungszeit).

Die Verzögerungszeit t

D kann man mit einer RC Konstanten abschätzen:

\( t_D \propto R \cdot C \)

Der Widerstand R ergibt sich aus der MOSFET-Gleichung.

C ist die Eingangskapazität des Inverters.

Mit zusätzliche Kapazitäten kann man die Verzögerungszeit vergrößern.

Die Leistungsaufnahme wird durch das Umladen der Kapazitäten bestimmt.

\( P = U \cdot I = U_{DD} \cdot \frac{Q}{t} = U_{DD} \cdot f \cdot C \dot U_{DD}

= U_{DD}^2 \cdot f \cdot C \)

Detaillierte Betrachtungen findet man unter

Integrierte Schaltungen Dr. Wolf, Prof. Klar, TU Berlin

Die Transistoren haben Kapazitäten und Widerstände.

C = Cox

Den Widerstand kann man für VDS = VGS = VDD abschätzen:

R = VDSmax/IDSmax

Die Frequenz der Schwingung ergibt sich aus den Verzögerungszeiten:

tpdHL = 0.7 * Rn * C

tpdLH = 0.7 * Rp * C

Rn und Rp sind die Widerstände von NFET und PFET, C die Gate-Source, Gate-Drain

und Lastkapazitäten.

Im elektrischen Modell werden die Kapazitäten der Transistoren mit dem Drain-Source Strom der

Transistoren geladen und entladen.

Die Periodendauer eines Ringoszillators mit 3 Invertern ergibt sich zu:

TP = n * 0.7 * C (Rn + Rp)

n: Anzahl der Inverter

Die mittlere Stromaufnahme ist:

C = Q / U = I * t / n / VDD = 2 * VDD/(Rn + Rp) * TP / n / VDD

IAVG = 2 * VDD / (Rn + RP)

PAVG = 2 * VDD * VDD / (Rn + RP)

Setzt man die Parameter der Simulation in diese Gleichungen ein erhält man:

VDD = 5 V

C = (CGS0 + CGDO) = 1.8 pF

RN = VDS / IDS = VDS * 2 / KP / (VGS - VT0)^2 = 5 V * 2 / 500E-6 / 16 V^2

= 1250 Ω

TP = 3 * 1.8 pF * 1250 = 6.79 ns

f = 148 MHz

Es gibt einen grossen Unterschied zwischen Theorie und Simulation.

Fügt man eine Kapazität am Eingang ein, sieht man bei Kapazitäten größer 1 pF

einen Einfluss auf die Frequenz.

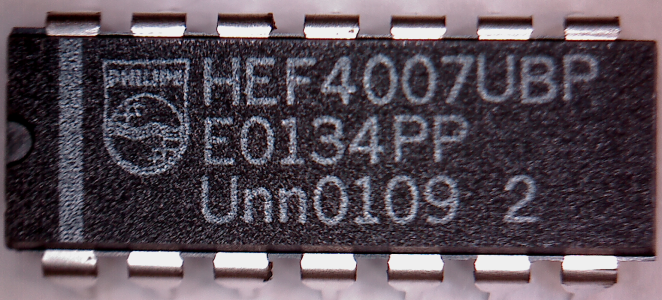

Bauteilauswahl und Datenblatt

Man kann bei Conrad, Digikey, Reichelt Mouser oder anderen Distributoren nach Invertern oder MOSFETs suchen.

Hier wurde der Baustein CD4007 ausgewählt, da er viele Einsatzmöglichkeiten hat,

bei 5 V betrieben werden kann und

bei 5 V eine spezifizierte Verzögerungszeit von 55 ns hat.

\( f_{max} = \frac{1}{2 \cdot 3 \cdot 55 ns } = 3 MHz\)

Die Eingangskapzität wird mit 10 pF angegeben.

Der Ausgangsstrom (Output Low/High Current IOL/IOH min) bei 5 V wird

mit mindestens 1 mA angegeben.

Die Kennlinie bei 5 V, 10 V, 15 V zeigt einen typischen Strom von 4 mA, 14 mA, 27 mA (Fig 5).

Figure 12 zeigt die Verzögerungszeit bei 5V bei verschiedenen Lasten.

Man kann eine Geradengleichung abschätzen:

\( t_D = 20 ns + \frac{30 ns}{50 pF} C_L \)

Für eine Frequenz von 1 MHz benötigt man eine Verzögerungszeit von:

\( t_D = \frac{1}{2 \cdot n \cdot f}

= \frac{1}{2 \cdot 3 \cdot 1 MHz} = 167 ns \)

Für diese Frequenz schätzt man eine Kapazität von 250 pF ab.

Diese Überlegungen sollen mit der Simulation bestätigt werden.

Schaltungssimulation

Im

Script Elektronik findet

man ein LTSPICE MOSFET Modell

.model CD4007N NMOS(LEVEL=1 KP=500u VT0=1 LAMBDA=0.002 CGSO=45n CGBO=2n CGDO=45n)

.model CD4007P PMOS(LEVEL=1 KP=500u VT0=-1 LAMBDA=0.002 CGSO=45n CGBO=2n CGDO=45n)

CGD0 und CGS0 werden bei LTSPICE in F/m angegeben. Der default Wert für W und L sind 20 µm.

CGD0 = 45 nF entspricht damit CGDO * 0.00002 = 0.9 pF.

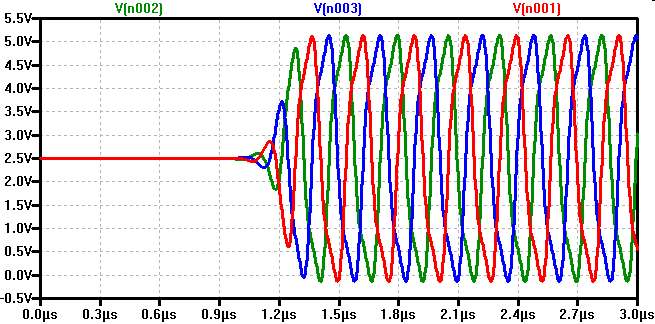

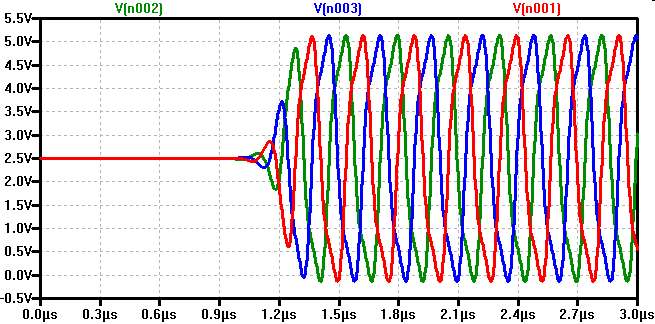

Man bekommt folgendes Simulationsergebnis bei einer Versorgungsspannung von 5V.

Mit Hilfe der folgenden Anweisungen wird Periodendauer und Frequenz bestimmt.

.MEAS TRAN T1 WHEN V(U0)=2.4 RISE=1

.MEAS TRAN T2 WHEN V(U0)=2.4 RISE=2

.MEAS TRAN TP PARAM T2-T1

.MEAS TRAN F PARAM 1/TP

Die Verzögerungszeiten sind tpdHL = 45 ns und tpdLH =40 ns.

Die Periodendauer beträgt: 259 ns

Die Frequenz ist: 3.85 MHz

Der mittlere Stromverbrauch ist 2.144 mA.

Dies entspricht den Erwartungen auf Grund des Datenblatts.

Untersuchung von VDD und IAVG für die Bestimmung von Rn und Rp

| VDD / V | 5 | 6 | 7 | 8 | 9 | 10 | 12 | 15 |

| IAVG / mA | 2.14 | 3.39 | 4.94 | 6.78 | 8.93 | 11.4 | 17 | 28.3 |

| f / MHz | 3.85 | 5.09 | 6.34 | 7.60 | 8.86 | 10.1 | 12.7 | 16.5 |

Bei VDD = 5V erwartet man mit dem vorhandenen einfachen LEVEL1

Transistormodell IDS = 0.5mA (5 - 1)^2 = 8 mA Strom.

Trennt man die Rückkopplung auf und legt an den Eingang ein Serienwiderstand (100 kΩ) und eine

Spannungsquelle (2.5 V) und führt eine AC Simulation durch kann man bei 5V eine

3dB Eckfrequenz von 566 Hz und damit eine Eingangskapazität von:

C = 1 / 2 / π / R / f = 1 / 2 / π / 100 kΩ / 566 Hz = 2.8 pF

bestimmen.

Spannungsquelle (2.7 V) f3db = 45 kHz: C = 35 pF

Spannungsquelle (2.6 V) f3db = 35 kHz: C = 45 pF

Spannungsquelle (2.5 V) f3db = 566 Hz: C = 2.8 pF

Spannungsquelle (2.4 V) f3db = 34 kHz: C = 45 pF

Spannungsquelle (2.3 V) f3db = 44 kHz: C = 35 pF

Spannungsquelle (2.2 V) f3db = 52 kHz: C = 30 pF

Eine Transientenanalyse Spannungsquelle (2.5 V) 0.5V Amplitude ergibt f3db = 25 kHz ergibt C = 63 pF

Das Ausgangssignal ist nicht sinusförmig.

Eine AC Analyse mit Source und Drain auf konstanten Potential verbunden ergibt:

Eckfrequenzen von 173 MHZ (PFET) und 315 MHz (NFET) entsprechend Cinp = 9 pF und Cinn = 5pF

Weiterhin wird untersucht, wie sich die Verzögerungszeit bei Veränderung

der Lastkapazität verhält.

| CL/pF | 20 | 40 | 60 | 80 |

| tDsim5V/ns | 66 | 89 | 112 | 130 |

| tDData5V/ns | 36 | 48 | 60 | 73 |

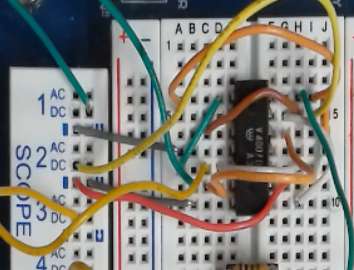

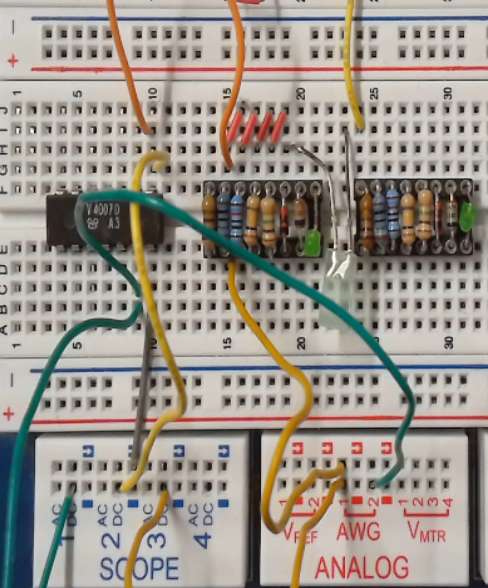

+ Praktischer Aufbau Transistormessung

- Praktischer Aufbau Transistormessung

Aufgrund des Unterschieds zwischen Datenblatt und Simulation wird noch einmal versucht durch Messung

die Transistorparameter Vth, KN, KP und Cin zu bestimmen.

Messung der statischen Kennlinien

Die Transistorparameter und die Kennlinien können analog zu

dem Versuch 4

und

dem Versuch 5 bestimmt werden.

Mit dem Spannungsabfall am Messwiderstand R1 wird der Drain-Source-Strom für

verschiedene UGS und UDS bestimmt.

Die Parameter werden entsprechend der Vorlesung

MOSFET Transistor MOSFET Parameterextraktion bestimmt.

NFET

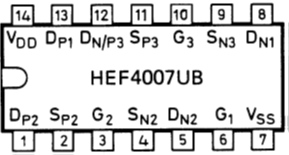

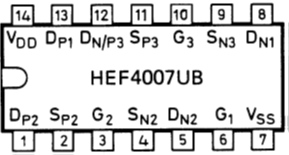

Verdrahtungsliste:

NFET Transistor 3:

Gate Pin 6 auf Pin 8, OSC1

Source Pin 7 auf GND

Drain Pin 8 auf 100Ω, OSC2

AWG1 auf 100Ω auf OSC3

Übertragungskennlinie: AWG1 = 1V..4V 0.2V Schritten, 100 Ω

| OSC1 (UGS) / V | 0.98 | 1.77 | 1.96 | 2.15 | 2.33 | 2.70 | 3.05 | 3.40 | 3.74 | 5.37 |

| OSC3 (AWG1) / V | 0.98 | 1.80 | 2.00 | 2.20 | 2.40 | 2.80 | 3.20 | 3.60 | 4.00 | 6.00 |

| IDS = (OSC3 - OSC1)/100 / mA | 0 | 0.30 | 0.40 | 0.50 | 0.70 | 1.00 | 1.50 | 2.00 | 2.60 | 6.30 |

Übertragungskennlinie: AWG1 = 1V..4V 0.2V Schritten, 1 kΩ

| OSC1 (UGS) / V | 2.03 | 2.25 | 2.45 | 2.64 | 2.82 | 3.60 | 4.26 |

| OSC3 (AWG1) / V | 2.39 | 2.80 | 3.20 | 3.60 | 4.00 | 6.00 | 8.00 |

| IDS = (OSC3 - OSC1)/1000 / mA | 0.36 | 0.55 | 0.75 | 0.96 | 1.18 | 2.40 | 3.74 |

Uth = 1 V

beta = 0.350 mA/V^2

KP = 700 µA/V^2

Gate wird auf AWG2 gelegt.

Ausgangskennlinie UGS = AWG2 = 4V, 1 kΩ

| OSC2 (UDS) / V | 0.52 | 1.25 | 2.85 | 3.82 | 4.80 | 5.78 | 6.76 |

| OSC3 (AWG1) / V | 2.00 | 4.00 | 6.00 | 7.00 | 8.00 | 9.00 | 10.00 |

| IDS = (OSC3 - OSC1)/1000 / mA | 1.48 | 2.75 | 3.15 | 3.18 | 3.20 | 3.22 | 3.24 |

λ = 0.0081 V^-1

PFET

PFET Transistor 3:

Gate Pin 6 auf Pin 13, OSC1

Source Pin 14 auf GND

Drain Pin 13 auf 1 kΩ, OSC2

AWG1 auf 1 kΩ auf OSC3

Übertragungskennlinie: AWG1 = -1V..-4V 0.2V Schritten, 100 Ω

| OSC1 (UGS) / V | -1 | -1.38 | -1.54 | -1.68 | -1.80 | -1.93 | -2.15 | -2.35 | -2.59 | -2.81 | -3.20 | -3.91 | -4.77 |

| OSC3 (AWG1) / V | -1 | -1.40 | -1.60 | -1.80 | -2.00 | -2.20 | -2.60 | -3.00 | -3.50 | -4.00 | -5.00 | -7.00 | -10.00 |

| IDS = (OSC3 - OSC1)/1000 / mA | 0 | -0.02 | 0.04 | -0.12 | -0.20 | -0.27 | -0.45 | -0.65 | -0.91 | -1.19 | -1.80 | -3.09 | -5.23 |

y=-0.0198x-0.0218

β = 0.392 mA/V-2

KP = 784 µA/V^2

Gate wird auf AWG2 gelegt.

Ausgangskennlinie UGS = AWG2 = -4V, 1 kΩ

| OSC2 (UDS) / V | -6.43 | -2.84 | -1.51 | -0.65 | -3.70 | -5.50 | -4.60 |

| OSC3 (AWG1) / V | -10.00 | -6.00 | -4.00 | -2.00 | -7.00 | -9.00 | -8.00 |

| IDS = (OSC3 - OSC1)/1000 / mA | -3.57 | -3.16 | -2.49 | -1.34 | -3.30 | -3.50 | -3.4 |

y = 0.1x-2.9366

λ = 0.0340 V^-1

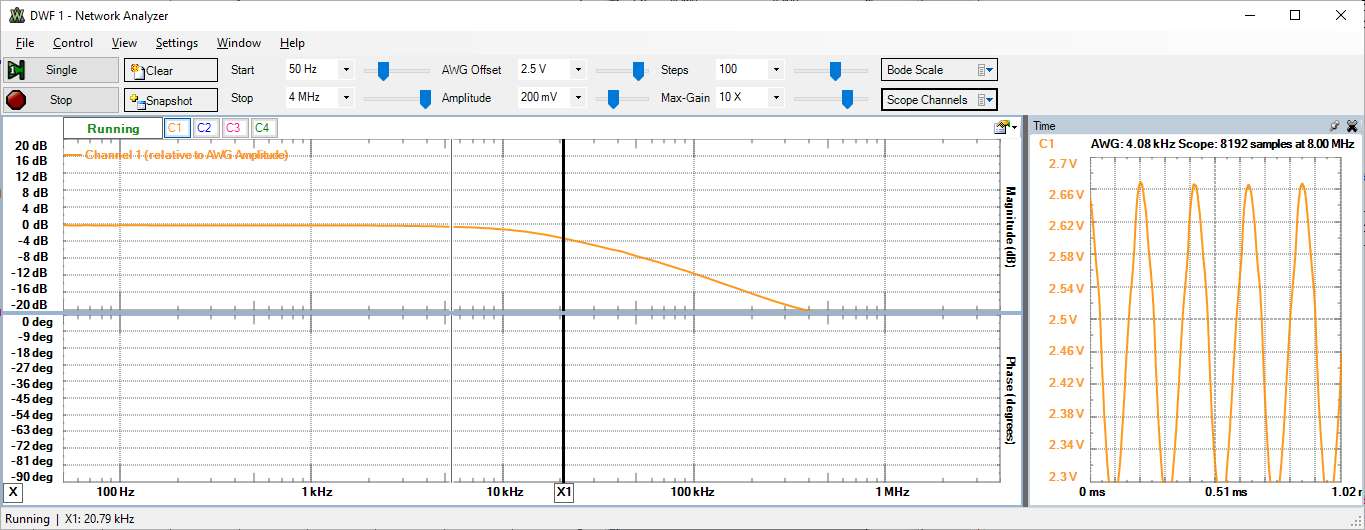

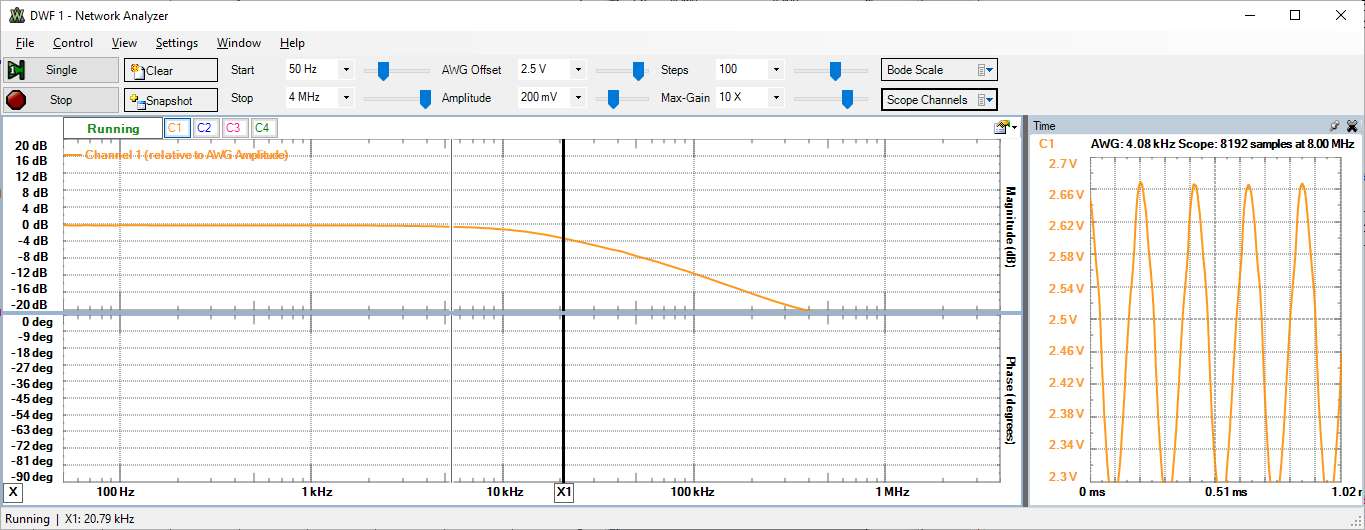

Input Kapazität

Als erstes wird die Breadboardkapazität bestimmt:

Messung Übertragungsfunktion 2V 100k + - Leitung 3dB 30kHz, C= 53 pF

Messung Übertragungsfunktion 2V 100k ohne Leitung 3dB 70kHz, C = 22 pF

Messung Übertragungsfunktion 2V 100k 5er Leitung 3dB 60kHz, C = 26 pF

Messung Übertragungsfunktion 2V 1M + - Leitung 3dB 2.2kHz, C = 72 pF

Die Breadboardkapazitäten werden nur bei den Versorgungsleitungen mit 50..70 pF sichtbar.

Die Messgenauigkeit bzw. Kapazität des Messaufbaus alleine liegt bei 20pF.

Messung Übertragungsfunktion 2V 1M Kapazität 1nF 3dB 180 Hz, C = 0.88 nF = 880 pF

Messung Übertragungsfunktion 2V 100k Kapazität 1nF 3dB 1.65 kHz, C = 0.96 nF = 960 pF

Kapazitäten um 1 nF können gut bestimmt werden.

VDD = 5V = VP+ pin 14

Pin 13 und Pin 17 Ausgang verbunden.

Pin 6 Gate SCOPE 1, R = 100 kΩ

AWG1 verbunden mit R= 100 kΩ

Pin 7 GND

Network Analyzer

AWG1 2.5V Offset, 200mV Amplitude

C = 1 / 2 / π / 100 kΩ / 20 kHz = 80 pF

AWG1 2.0V Offset, 200mV Amplitude

C = 1 / 2 / π / 100 kΩ / 35 kHz = 45 pF

Messung NFET:

Uthn= 1 V

Kp = 700 uA/V^2

λ = 0.0081 V^-1

Messung NFET:

Uthp= -1.1 V

Kp = 784 uA/V^2

λ = 0.034 V^-1

Kapazität:

Cin = 45..80 pF

|

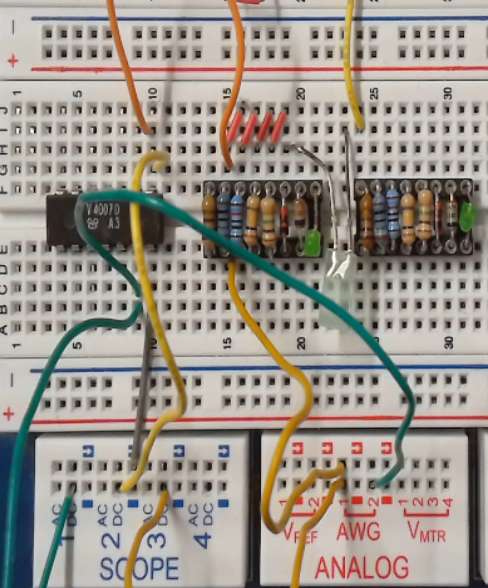

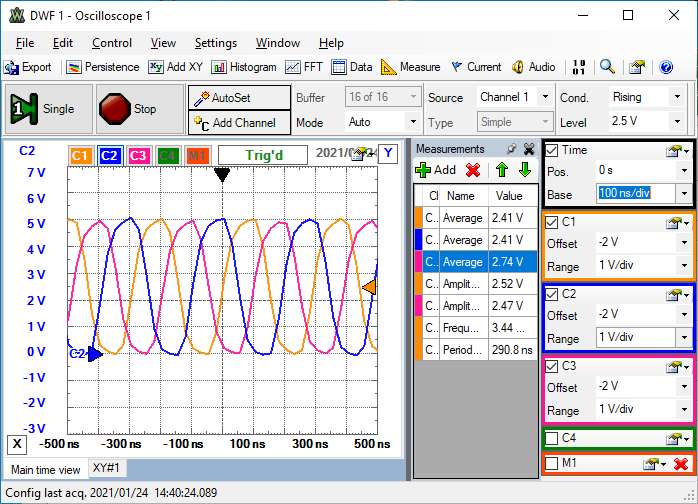

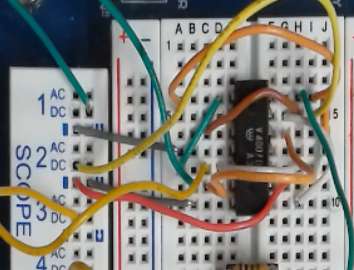

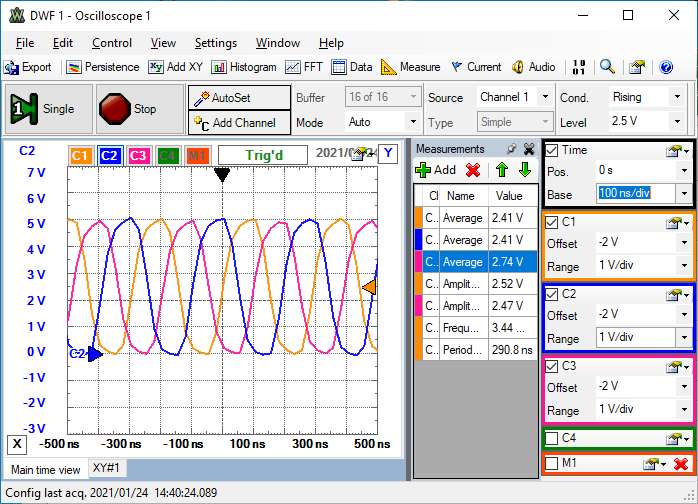

+ Ringoszillator Messung

- Ringoszillator Messung

Start: 14:31 - 15:05

Pin 14 VP+

Pin 13 Pin 8 Pin 3 OSC2

Pin 2 VP+

Pin 1 Pin 5 Pin 10 OSC3

Pin 4 GND

Pin 7 GND

Pin 11 VP+

Pin 9 GND

Pin 12 Pin 6 OSC1

| VP+ / V | 5 | 6 | 7 | 8 | 9 | 4 | 3 | 2 | 1.5 | 1.3 | 1.2 | 1.1 |

| f kHz | 3438 | 4255 | 4960 | 5560 | 6095 | 2494 | 1499 | 506 | 128 | 38 | 13 | 2.5 |

| IDD mA | 3 | 5 | 7 | 9 | 11 | 2 | | | | | | |

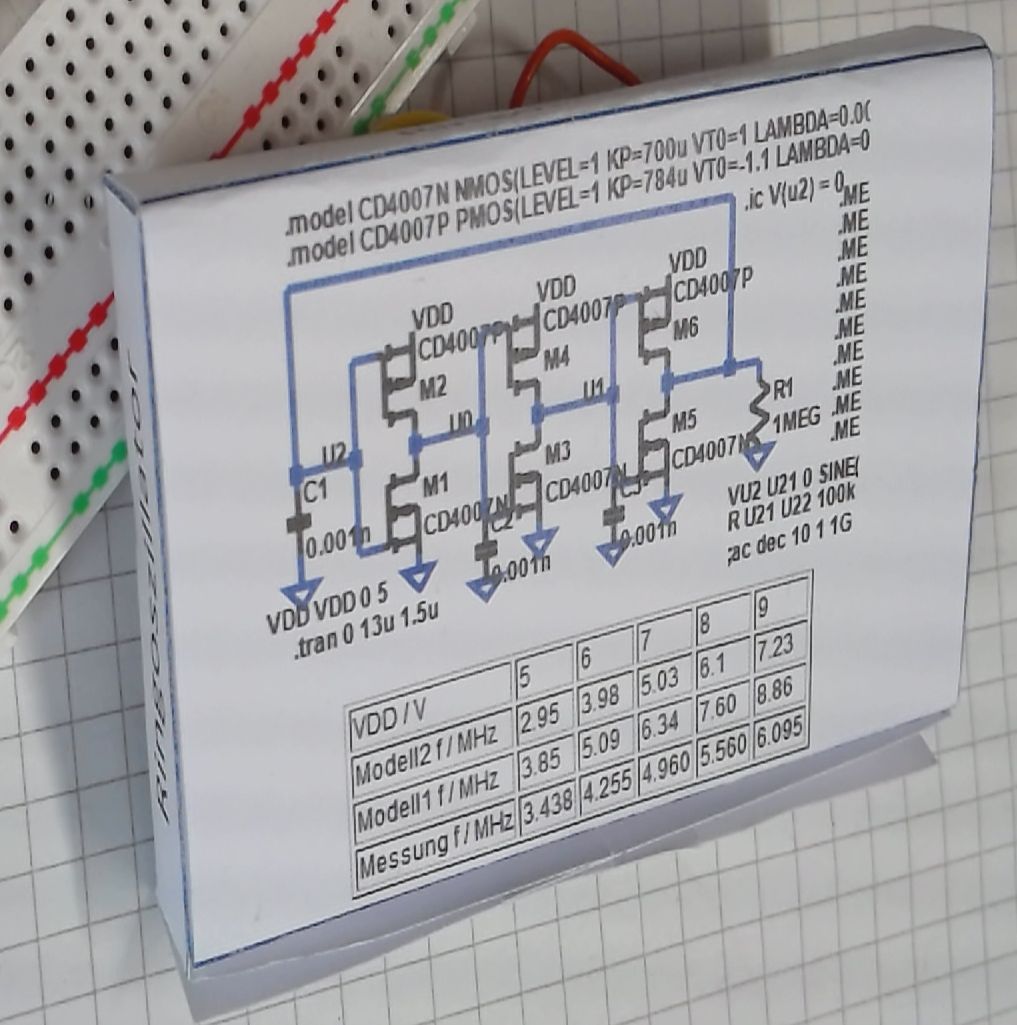

+ LTSPICE Simulation

- LTSPICE Simulation

25.01.2021: 7:30-8:58

Geändertes Modell:

.model CD4007N NMOS(LEVEL=1 KP=700u VT0=1 LAMBDA=0.008 CGSO=90n CGBO=.2n CGDO=90n)

.model CD4007P PMOS(LEVEL=1 KP=784u VT0=-1.1 LAMBDA=0.034 CGSO=90n CGBO=.2n CGDO=90n)

| VDD / V | 5 | 6 | 7 | 8 | 9 | 10 | 12 | 15 |

| IAVG / mA | 3.2 | 5.2 | 7.65 | 10.6 | 14.2 | 18.3 | 28.3 | 47.7 |

| f / MHz | 2.95 | 3.98 | 5.03 | 6.1 | 7.23 | 8.36 | 10.7 | 14.4 |

+ Zusammenfassung

- Zusammenfassung

Die Schaltung wurde erst ohne Kapazitäten gemessen und mit der Simulation verglichen.

| VDD / V | 5 | 6 | 7 | 8 | 9 |

| Modell2 IAVG / mA | 3.2 | 5.2 | 7.65 | 10.6 | 14.2 |

| Modell1 IAVG / mA | 2.14 | 3.39 | 4.94 | 6.78 | 8.93 |

| Messung IDD mA | 3 | 5 | 7 | 9 | 11 |

Man sieht deutliche Unterschiede zwischen Messung und Simulation.

| VDD / V | 5 | 6 | 7 | 8 | 9 |

| Modell2 f / MHz | 2.95 | 3.98 | 5.03 | 6.1 | 7.23 |

| Modell1 f / MHz | 3.85 | 5.09 | 6.34 | 7.60 | 8.86 |

| Messung f / MHz | 3.438 | 4.255 | 4.960 | 5.560 | 6.095 |

Messung mit verschiedenen Kapazitäten

5 V, 1 nF (Aufdruck 102), 211 kHz

5 V, 0.1 nF (Aufdruck 101), 1.28 MHz

5 V, 0.2 nF (2 x Aufdruck 101), 787 kHz

Für den Betrieb wurde eine Kapazität von 150 pF aus drei 100 pF Kapazitäten verwendet.

Messung der Variabilität

- Kapazität: +- 10%

- Spannung: +- 10%

- Temperatur: 0°, 50°

- CD4007 austauschen, anderer Hersteller

Betriebspunkt:

VDD = 5 V, C = 0.15 nF, 25°C, ftyp = 0.975 MHz, Iavg = 3.8 mA

Minimum und maximum Werte:

VDD = 5 V, C = 0.10 nF, 25°C, ftyp = 1.28 MHz

VDD = 5 V, C = 0.20 nF, 25°C, ftyp = 0.787 MHz

VDD = 5.5 V, C = 0.15 nF, 25°C, fmax = 1.10 MHz, Iavg = 4.5 mA

VDD = 4.5 V, C = 0.15 nF, 25°C, fmin = 0.840 MHz, Iavg = 2.85 mA

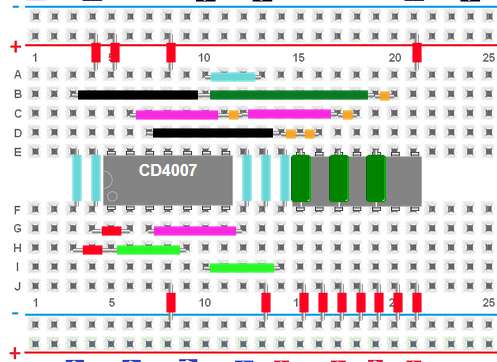

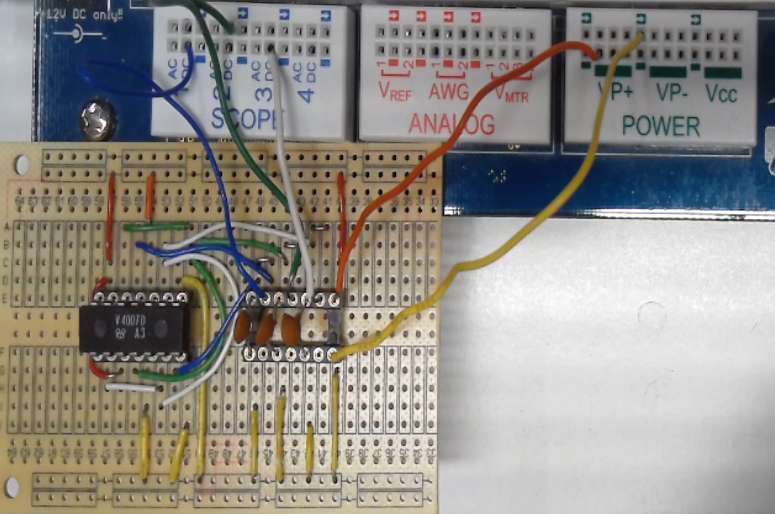

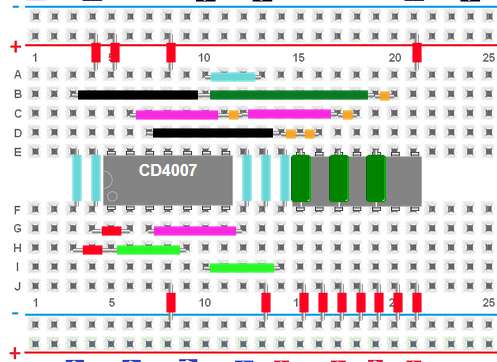

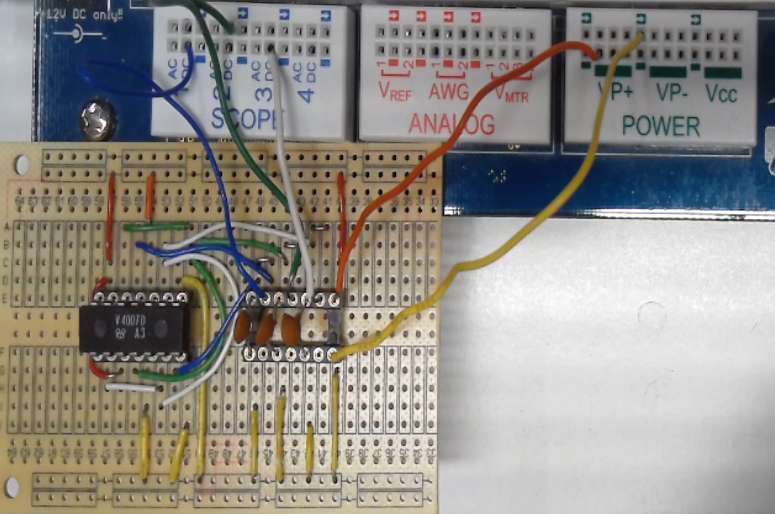

Platine

Die Platine ist analog zum Steckbrett aufgebaut.

GLOBALSCALE=0.7

IC||264|312|1|CD4007|U?|||DIP14|IC||DIP14

IC||453|312|1||U?|||DIP14|IC||DIP14

Capacitor||451|310|5|Capacitor|C?||2||||cap_5

Capacitor||489|310|5|Capacitor|C?||2||||cap_5

Capacitor||526|310|5|Capacitor|C?||2||||cap_5

Wire||269|194|2|||#FF0000|1||||

Wire||290|269|1|||#FF9000|5||||

Wire||308|385|1|||#00A060|6||||

Wire||401|310|2|||#FF9000|4||||

Wire||384|269|1|||#CC6D00|2||||

Wire||571|194|2|||#FF0000|1||||

Wire||571|444|2|||#FF0000|1||||

Wire||403|269|1|||#FF0000|5||||

Wire||498|269|1|||#CC6D00|2||||

Wire||458|444|2|||#FF0000|1||||

Wire||496|444|2|||#FF0000|1||||

Wire||533|444|2|||#FF0000|1||||

Wire||252|385|1|||#FF0000|3||||

Wire||250|310|2|||#FF9000|4||||

Wire||250|194|2|||#FF0000|1||||

Wire||271|404|1|||#DFFF00|5||||

Wire||231|310|2|||#FF9000|4||||

Wire||233|404|1|||#FF0000|3||||

Wire||233|250|1|||#DFFF00|7||||

Wire||365|250|1|||#DFFF00|9||||

Wire||535|250|1|||#CC6D00|2||||

Wire||325|444|2|||#FF0000|1||||

Wire||325|194|2|||#FF0000|1||||

Wire||365|231|1|||#FF9000|4||||

Wire||420|310|2|||#FF9000|4||||

Wire||420|444|2|||#FF0000|1||||

Wire||460|288|1|||#CC6D00|2||||

Wire||477|444|2|||#FF0000|1||||

Wire||515|444|2|||#FF0000|1||||

Wire||552|444|2|||#FF0000|1||||

Wire||308|288|1|||#00A060|7||||

Wire||365|423|1|||#00A060|4||||

Wire||441|288|1|||#CC6D00|2||||

Wire||439|310|2|||#FF9000|4||||

BREADBOARDSTYLE=BB7

Es wurden Testpunkte für die Anschlüsse und Messungen am 2. Sockel implementiert.

Die Kapazitäten wurden auf den 2. Sockel gesteckt, damit diese austauschbar sind.

Man könnte noch Brücken auf dem Sockel vorsehen, damit die Gesamtschaltung in einzelne

Schaltungsblöcke zur besseren Analyse aufgeteilt werden kann.

Pinbelegung 2. DIL 14 Sockel:

Pin 13 OSC1 (Ausgang 1)

Pin 11 OSC2 (Ausgang 2)

Pin 9 OSC3 (Ausgang 3)

Pin 8 VP+

Pin 7 GND, 0 V

Pin 1 Pin 14 C1

Pin 3 Pin 12 C2

Pin 5 Pin 10 C3

Es wurde eine abschliessende Messung durchgeführt.

VDD = 5 V, C = 0.10 nF, 25°C, f = 1.34 MHz

Die Frequenz ist im Vergleich zum Breadboard erhöht.

Die parasitären Kapazitäten sind geringer.

Jedes Board muss bei einer Fertigung am Ende gemessen und kalibriert werden.

Zusammenfassung

Die Übereinstimmung von Theorie, Simulation und Messung ist

tendenziell da, aber nicht sehr genau.

Das LEVEL 1 Transistormodell ist nicht ausreichend.

Mit der Versorgungsspannung nimmt die Frequenz des Ringoszillators

und die Leistungsaufnahme zu.

Mit zusätzlichen Lastkapazitäten nimmt die Frequenz ab.

Bei Änderungen der Temperatur, Spannung und der Lastkapazitäten um 10%

ändert sich die Frequenz um 10 %.

Die vorgestellte Schaltung kann nur kleine Lasten C < 10 pF treiben,

ansonsten benötigt man noch einen Treiberbaustein.

Die Dokumentation könnte man noch verbessern.

Ma sollte die Anschlüsse direkt auf der Schaltung noch beschriften.

Man sollte die Schaltung noch in ein

Gehäuse einbauen.

+ References

- References

Versuche Labor Elektronik 3

Vorlesung Elektronik 1

Datenblatt CD4007

Die Rohdaten wurden auch lokal in dem Verzeichnis Elektronik in einer Excel-Datei: OpAmp272RemoteBode.xls gespeichert.

Zeitaufwand

23.01.2021: 14:33-16:14 Theoriegleichung

24.01.2021: 8:45-10:15 Aufteilung in LTSPICE, Theorie, Datenblatt und

Untersuchung der Ströme und der Eingangskapazität

24.01.2021: 10:45-11:49 Kapazitätssimulation

24.01.2021: 11:53-13:09 NFET Messung

24.01.2021: 13:34-14:05 PFET Messung

24.01.2021: 14:05-14:31 Input Kapazität

24.01.2021: 14:31-15:05 Ringoszillator

25.01.2021: 7:30-8:58 LTSPICE Simulation

25.01.2021: 10:00-10:30 Breadboardkapazität

23.02.2021: 10:00-12:00 Simulation, Messung Variabilität (C, VDD) und Dokumentation

24.02.2021: 8:30-10:00 Lötaufbau und Messung

Gesamter Zeitaufwand mindestens ca. 9 x 90 min.