Interface ElectronicsLab 04 Analyze, Simulation and Calibration of a 8bit R2R-DAC***742R, ***136H |

Overview

- Building a 8bit R2R-DAC

- Simulation of the DAC with real resistor values

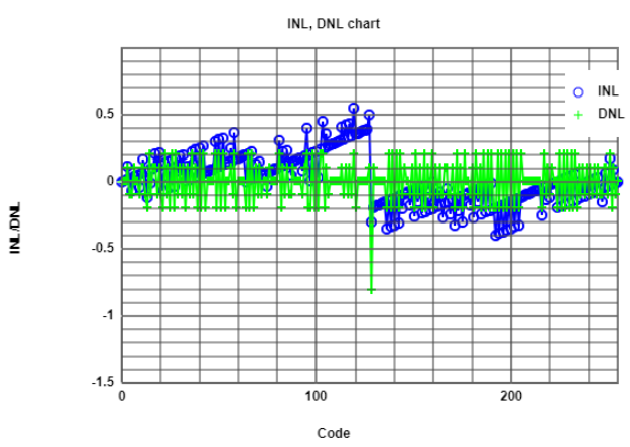

- INL/DNL ramp test, FFT (sine test) of simulated DAC

- Measurements of real DAC

- DAC behaivior at high frequency

- Settling time of the real DAC

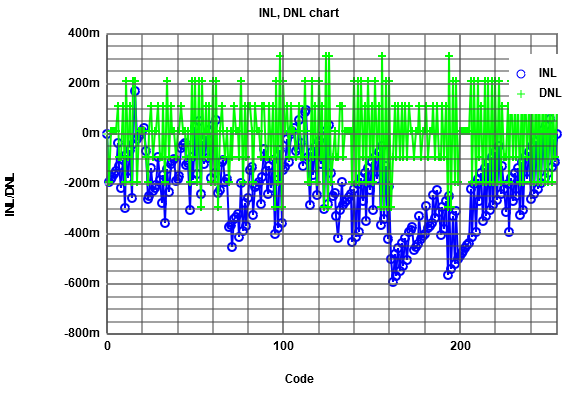

- INL/DNL of real DAC (ramp test)

- Optimization of real DAC

- Software Calibration of DAC

- FFT of optimized DAC

- Including "Export data with ReadOsci tool": ***742R

- From there: ***136H

Work distribiution:

Building a 8 bit DAC

|

| schamatic 1 |

Simulation of DAC with ramp test

|

|