Microelectronics06 Design RulesProf. Dr. Jörg Vollrath05 Manufacturing Process |

Video of lecture 06 28.04.2021

|

Länge: 01:02:59 |

0:1:23 Chip cross section REM picture 0:4:18 Bad oxide thickness, bad contact 0:6:54 Top view defects 0:10:24 Cross section doping REM 0:11:12 Reverse Engineering and competitor analysis 0:14:38 NAND Chip analysis, technology, size, capacity 0:18:23 Matching schematic versus layout 0:21:10 Layout LTSPICE AD, AS, PD, PS added capacitance 0:22:18 Schematic LTSPICE bare transistor model 0:23:42 MOSIS Design rules 0:28:43 Electric Preferences Technology Design Rules 0:32:48 From circuit to chip 0:36:1 Inverter mask set with alignment marks 0:39:48 Inverter Alignment 0:40:35 Pattern transfer, small feature size, shape, neighborhood 0:45:22 REM picture with rounded features of material 0:47:18 Dummy shapes 0:48:28 Overetch 0:49:28 Underexposure 0:51:34 Manual design rule check example 0:59:28 Extracting the schematic from layout 1:2:38 Logic function truth table extraction 1:5:18 LTSPICE simulation of truth table 1:8:38 LTSPICE PULSE statement 1:11:38 Learning Outcome |

Overview

Review:Yield, wafer, chips, defect density, manufacturing

Today:

- Carcass, chip, component

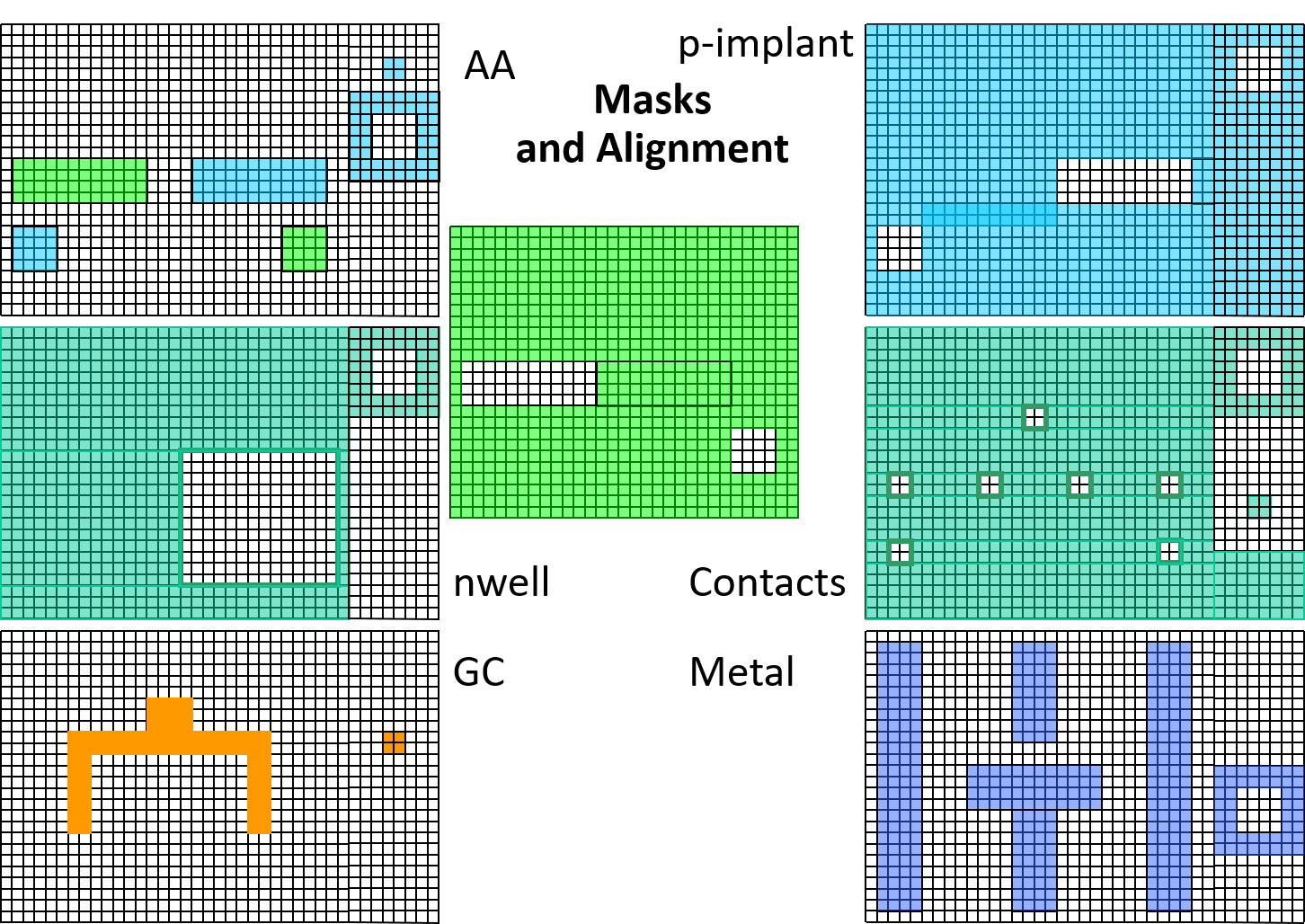

- Masks and alignment

- Alignment error

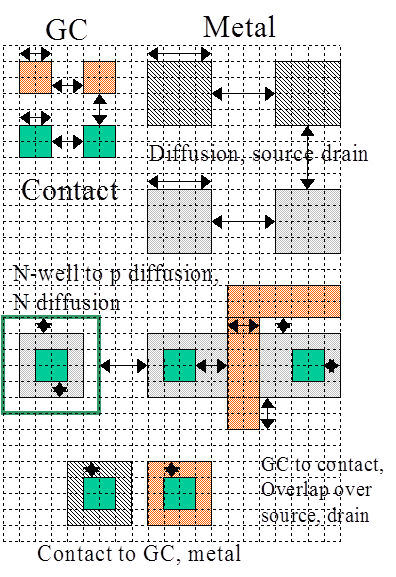

- Design rules: Feature size, distance, overlap

- Layout, errors, schematic, stick diagram

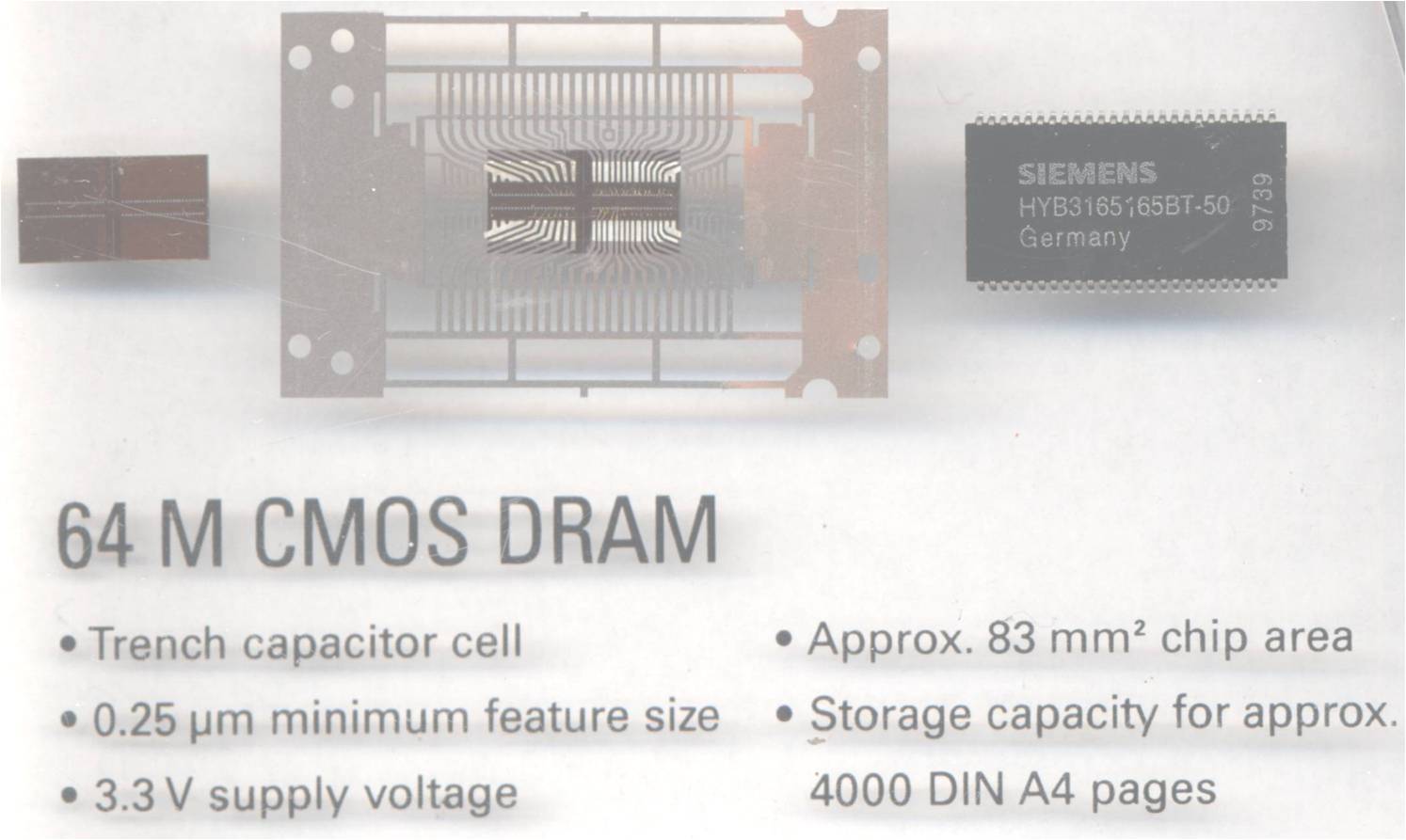

A 64MBit DRAM 1997

Author: Joerg Vollrath

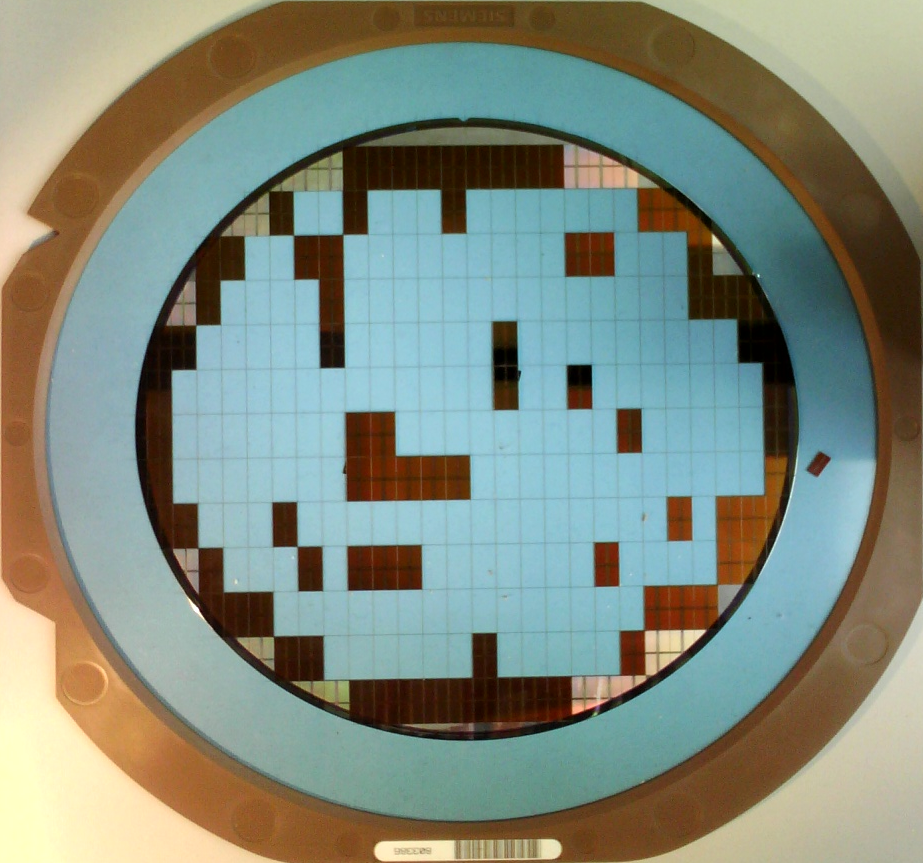

Wafer Carcass

Author: Joerg Vollrath

Semiconductor Manufacturing Strategies

Chip cross sections and top view

REM (raster electron microscope) or TEM (transmission electronic microscope) pictures of manufactured defect chips can be used to look for the root cause of failure.

Random defect density can be improved with clean rooms and cleaning steps.

Other faults can be backtraced to bad equipment, bad manufacturing recipes or malhandling.

Continous monitoring and traceability are very important to find root causes, eliminate faults and improve yield.

Reverse Engineering

Reverse Engineering is a common task in microelectronics.

The biggest companies doing this are:

IC-Insight: ic insight dram semiconductor market share

Formerly Chipworks now TechInsights Search "TechInsights-Samsung-48L-3D-V-NAND"

Product analysis:

iFixit: Search: "iPhone-3GS Tear down"

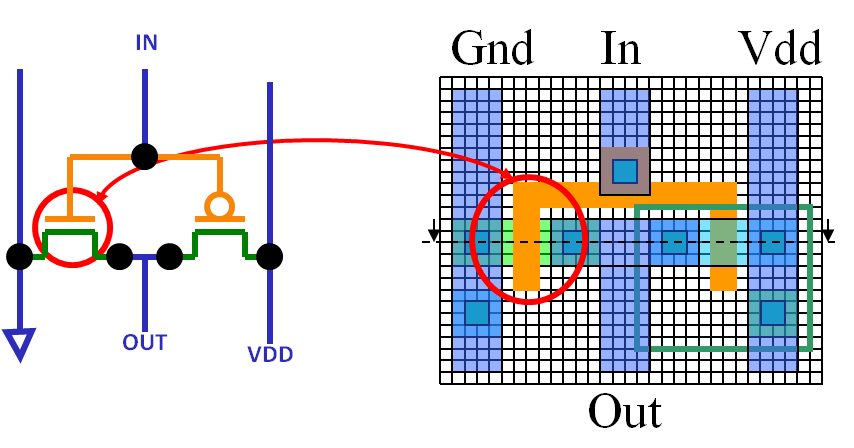

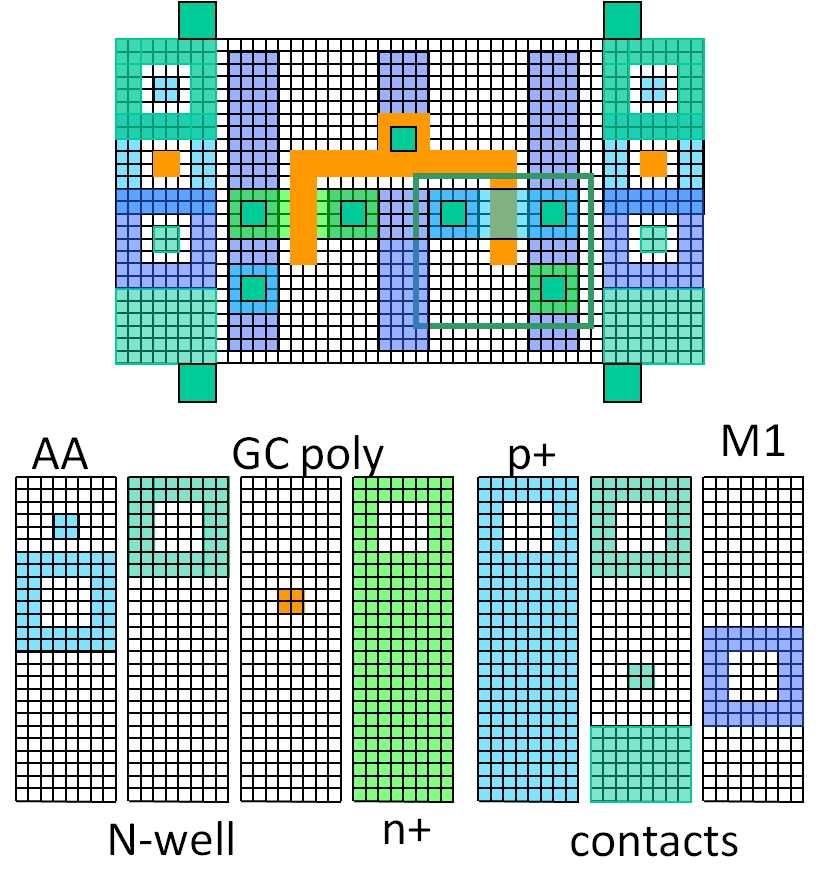

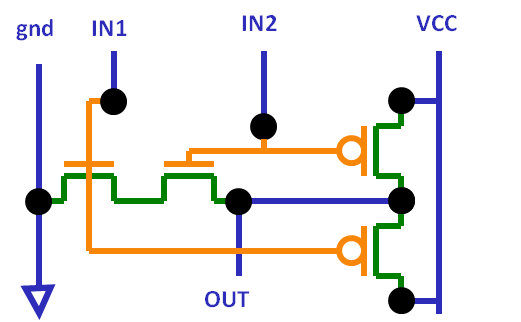

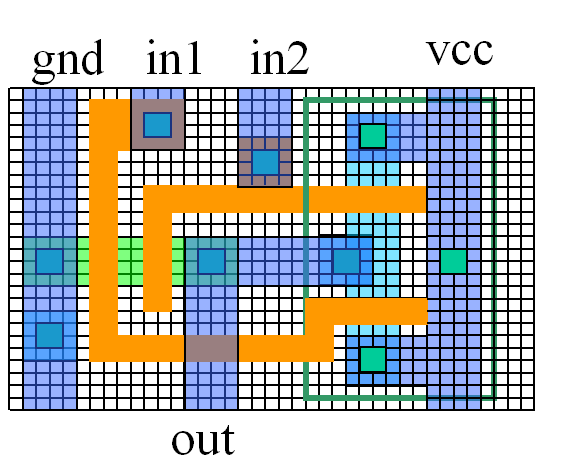

Matching Schematic versus Layout; Stick diagram

|

Symbols: Transistor, gnd, Vdd Properties: Names, width, length |

Layers, different color: Connection: metal (blue), polysilicon (orange,pink), contact (black) Transistor: crossing polysilicon and n- or p-diffusion (green) |

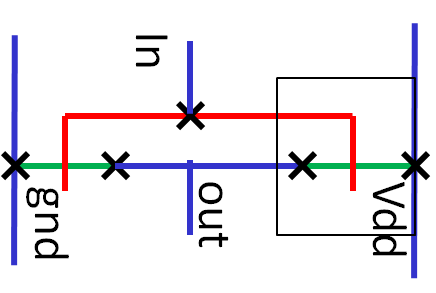

Before layouts are done stick diagrams can help planning.

This is shown on the right.

Only colored lines are used representing the layout.

Black crosses represent contacts.

Blue lines are metal, orange/red/pink lines are polysilicon, green lines are diffusion.

This is shown on the right.

Only colored lines are used representing the layout.

Black crosses represent contacts.

Blue lines are metal, orange/red/pink lines are polysilicon, green lines are diffusion.

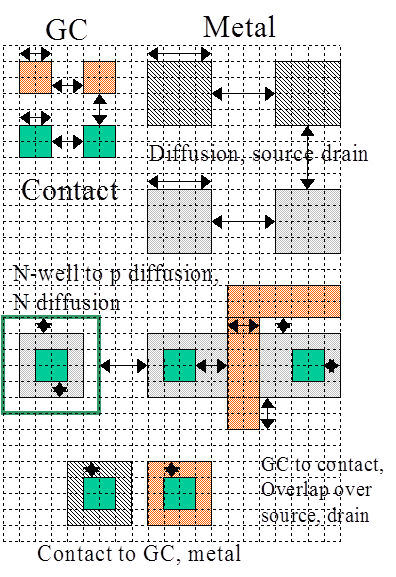

MOSIS design rules

|

|

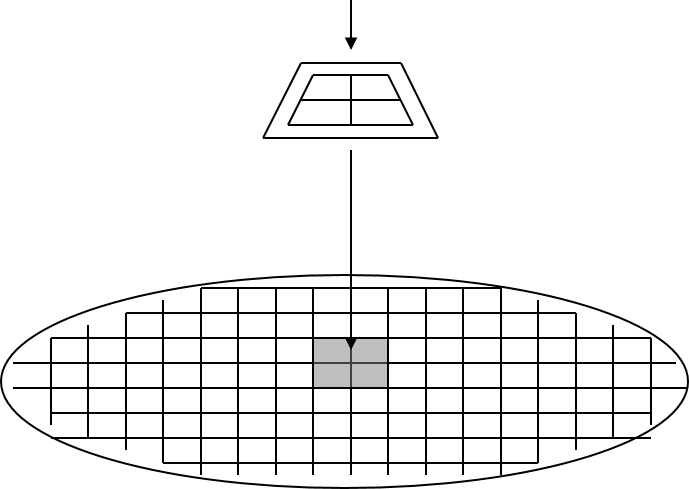

From Circuit to Chip

|

|

Inverter Mask Set

Author: Joerg Vollrath

Alignment for Layers

- They have to be visible: Step size in a film

- Accuracy, shape, electrical signal

- Position on chip

- Lateral, vertical transition

- Rotation

- Lens aberration

- Chip to chip alignment (Step size)

Inverter Alignment

Author: Joerg Vollrath

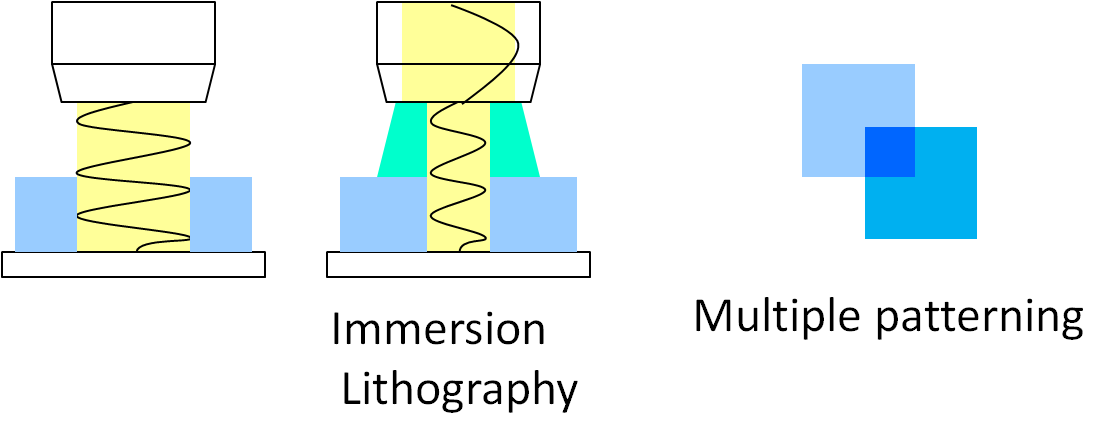

Pattern Transfer

Patterns are transfered by illuminating a photoresist and changing the material

structure. During photo resist development the illuminated part is

chemically removed.

Patterns can change during this process.

Wavelengths to transfer patterns changed with feature size.

i-Line 365nm was used for 1.0..1.5µm.

248 nm from 1µm..180nm.

193 nm Deep ultra violett (DUV) from 180 nm..13 nm.

In the future for less than 10nm extreme ultra violett (EUV) could be used.

Since wavelength is bigger than the feature size immersion lithography and multiple patterning is used.

A liquid changes the wavelength of light.

With multiple patterning only an overlap of 2 structures is printed.

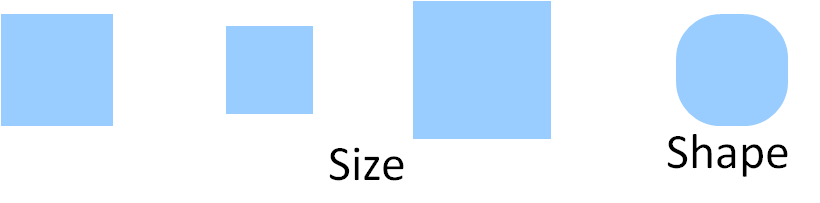

The shape of a feature is changed during the transfer.

- Size can change

- Edges and corners are rounded

- The shape can depend on the surroundings.

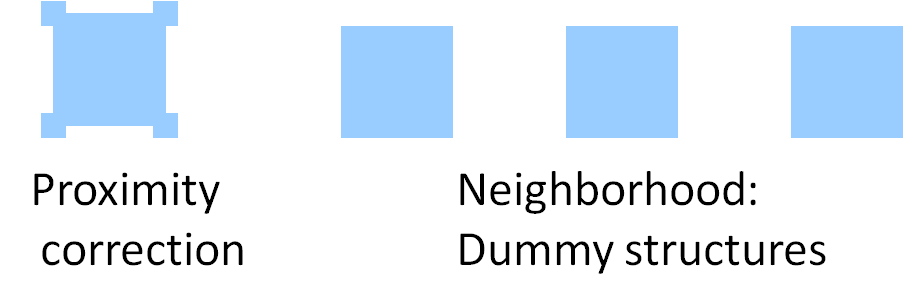

These errors can be precompensated by sizing, adding smaller features or dummy structures.

Also for chemical and mechanical processing a constant pattern density is needed for uniformity.

Dummy structures are used for that: GC fill, dummy contacts.

A common centroid layout should be used.

Patterns can change during this process.

Wavelengths to transfer patterns changed with feature size.

i-Line 365nm was used for 1.0..1.5µm.

248 nm from 1µm..180nm.

193 nm Deep ultra violett (DUV) from 180 nm..13 nm.

In the future for less than 10nm extreme ultra violett (EUV) could be used.

Since wavelength is bigger than the feature size immersion lithography and multiple patterning is used.

A liquid changes the wavelength of light.

With multiple patterning only an overlap of 2 structures is printed.

The shape of a feature is changed during the transfer.

- Size can change

- Edges and corners are rounded

- The shape can depend on the surroundings.

These errors can be precompensated by sizing, adding smaller features or dummy structures.

Also for chemical and mechanical processing a constant pattern density is needed for uniformity.

Dummy structures are used for that: GC fill, dummy contacts.

A common centroid layout should be used.

Overetch

Overetch, smaller lines causing opens

Author: Joerg Vollrath

Underexposure

Underexposure, fat lines causing shorts

Author: Joerg Vollrath

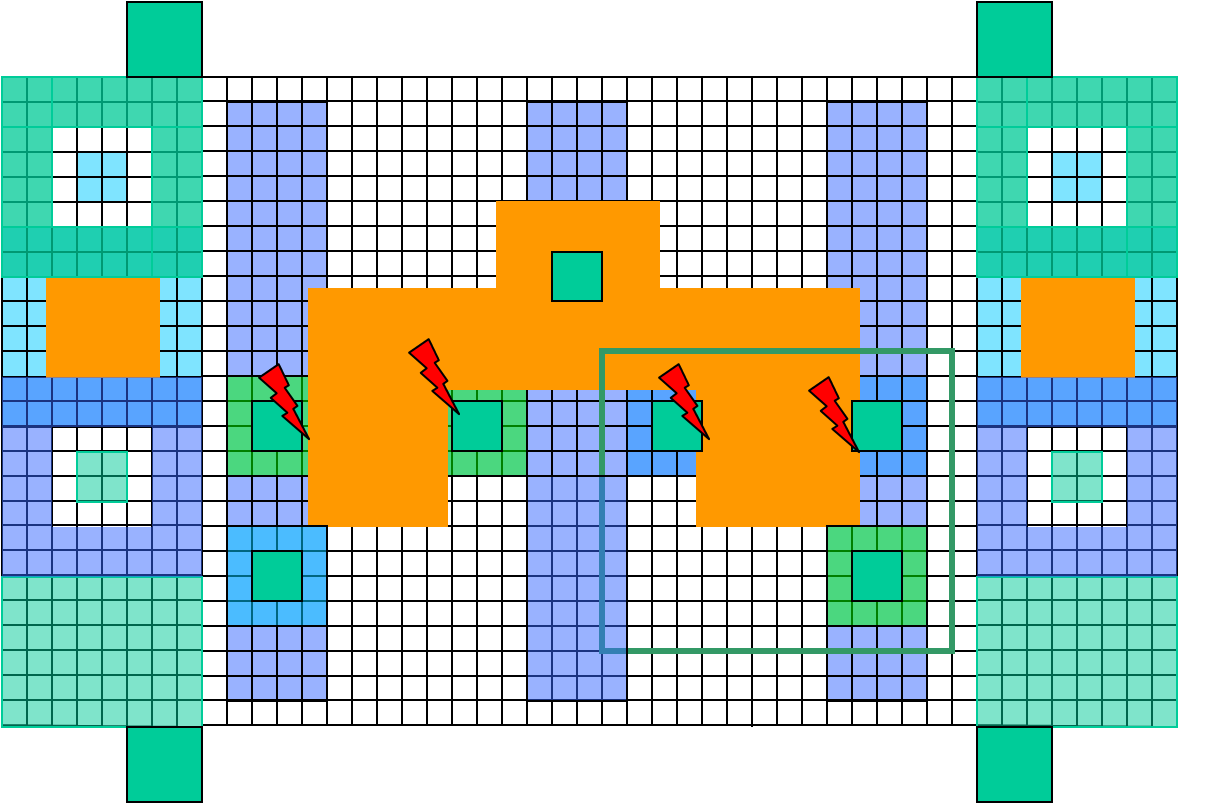

Translational misalignment causing shorts

Author: Joerg Vollrath

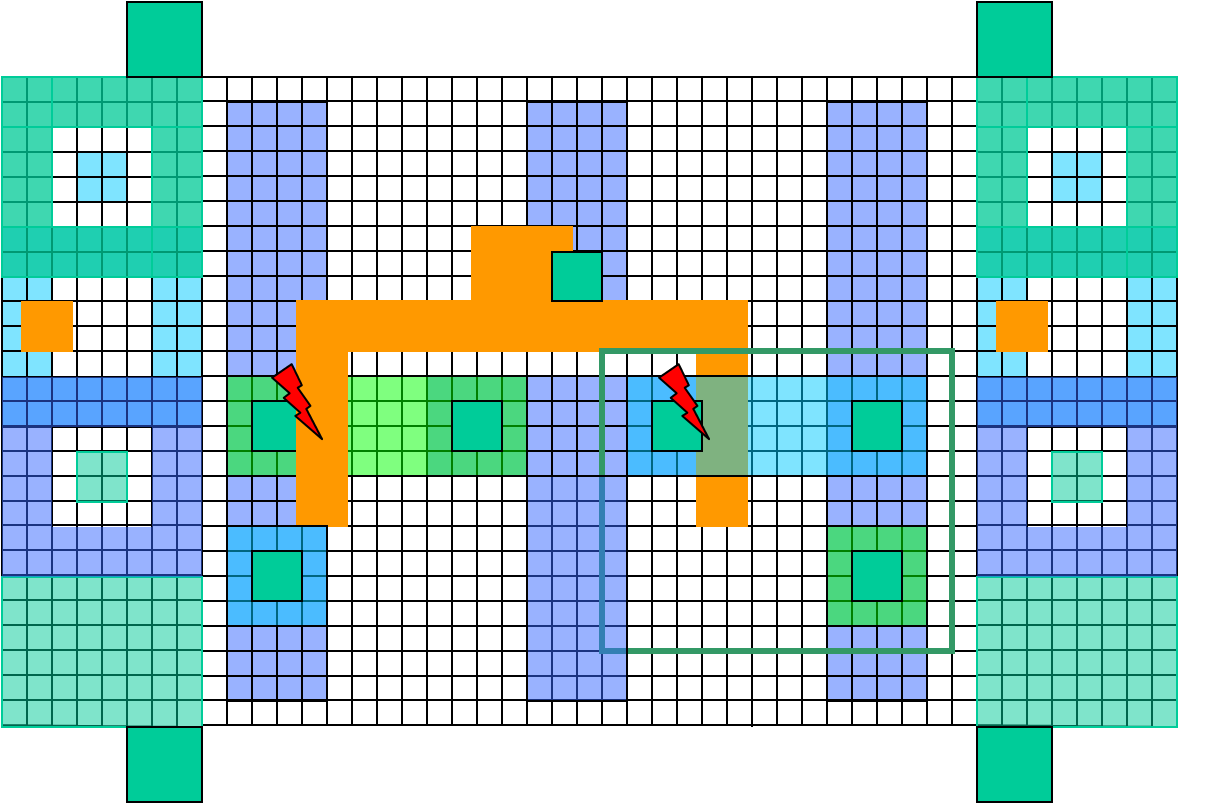

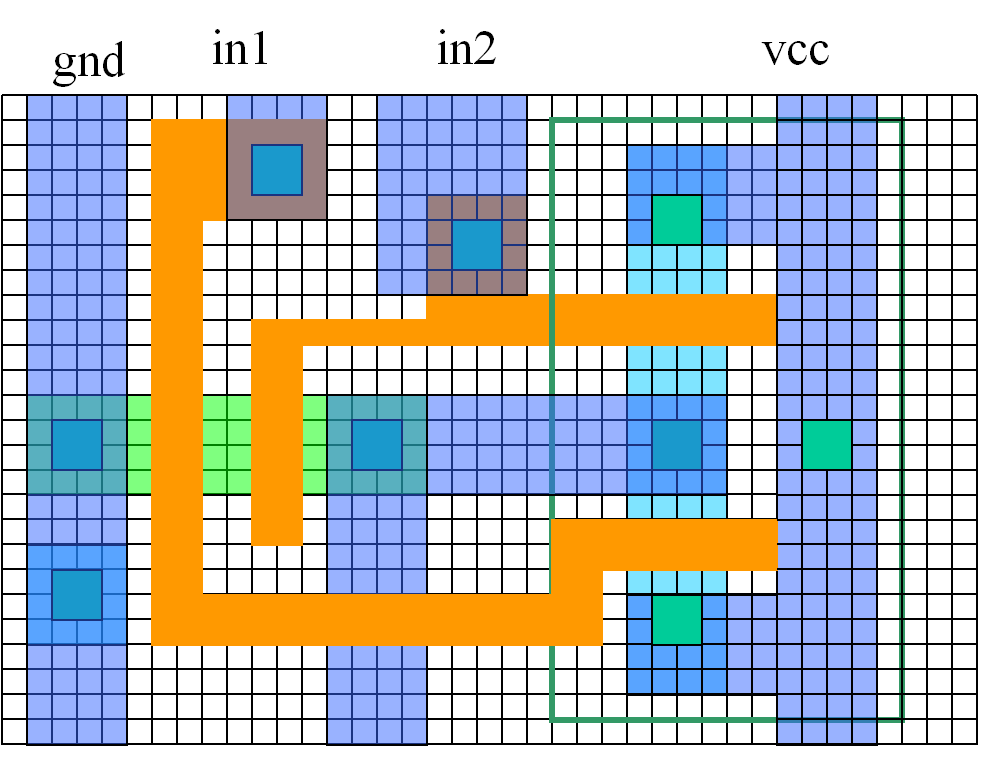

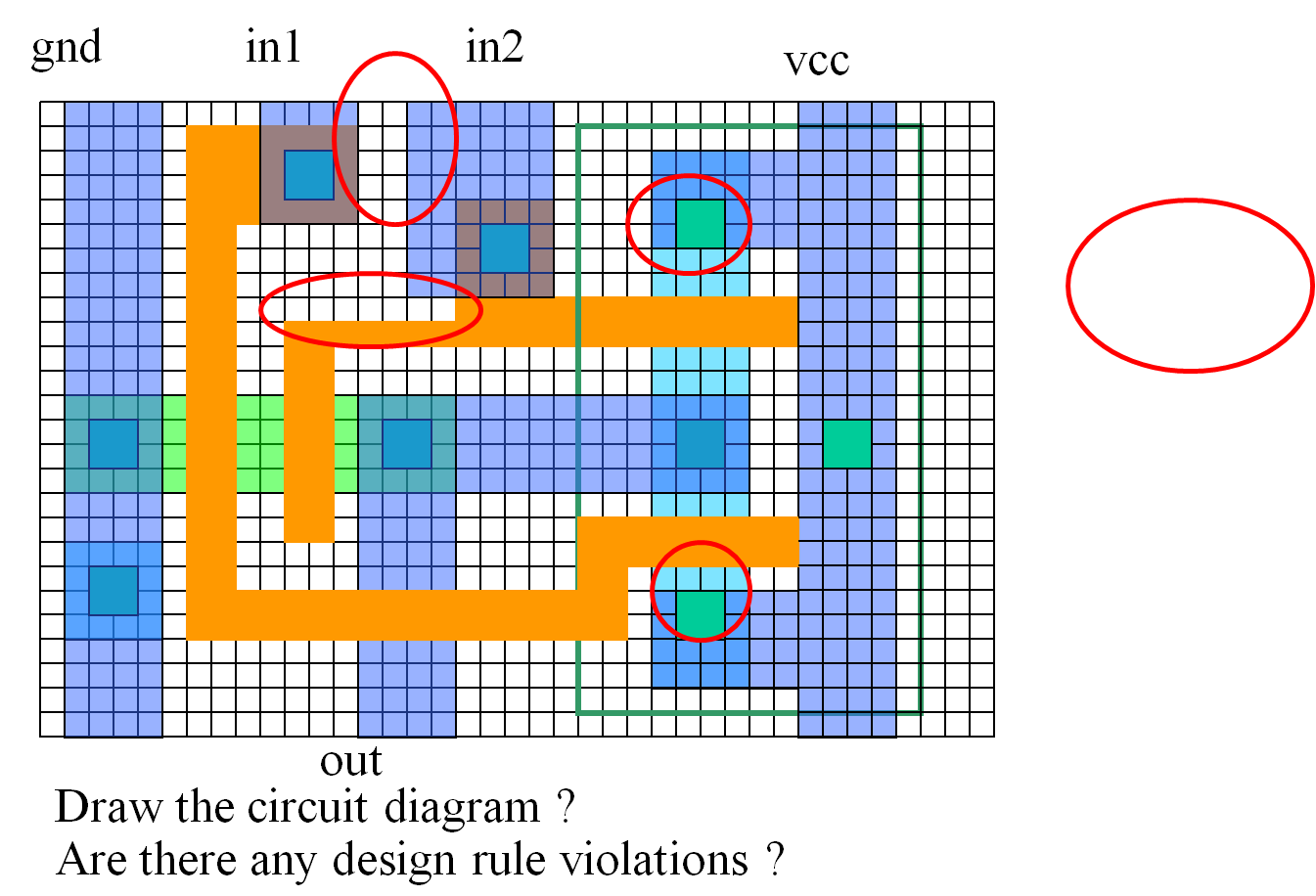

Problem Design Rule Check

Author: Joerg Vollrath

Problem Design Rule Check

Author: Joerg Vollrath

Problem Design Rule Check

| In2 | In1 | Out |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Using the simple MOSFET switch model a NFET switch is closed,

if the input is 1. A PFET switch is closed, if the input is 0.

The path to ground 0V is only connected if In2 and In1 are 1. Then the output is '0'.

The path to ground 0V is only connected if In2 and In1 are 1. Then the output is '0'.

Learning Outcome

- Be prepared for non functional chips

Design for test, diagnosis - Literature research is accompanied by competitor Analysis with reverse engineering

- A good layout starts with simple design rules (grid, straight lines), a stick diagram

and generates a robust (defect tolerant) design.

Area optimization only after detailed area problems are identified. - Manufacturing can cause opens and shorts and needs test.

Next: 07 CMOS Logic