Open Access MicroelectronicsEWME 2018Prof. Dr.-Ing. Jörg Vollrath12th European Workshop on Microelectronics Education |

Overview

- Course setting

- Open access, content overview and web page

- LTSPICE schematics

- Electric design and layout

- UART example

- VHDL: behavioural to structural with Xilinx Webpack

- Standard cells for synthesis

- AnalyzeJS: Glue web tool

- Result

- Outlook

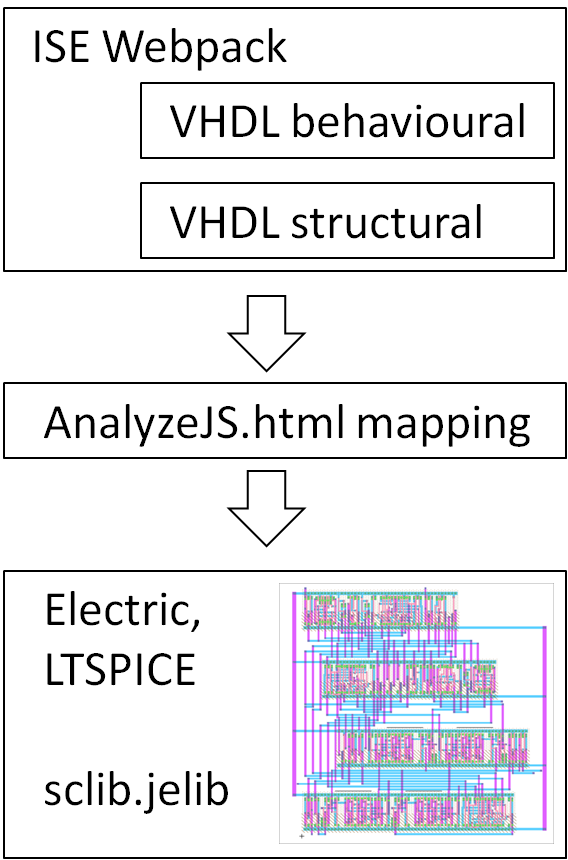

Generating structural VHDL with Xilinx Webpack and post processing with AnalyzeJS.html

Synthesis of a UART with Electric VLSI Design System

Simulation with LTSPICE.

Course setting

|

|

General Learning Outcome

General lessons Microelectronics provides- Roadmap goal setting

- First any solution, then improvement

- Simulation before realization

- Automation avoiding mistakes and providing repeatability

- Working on a tight schedule

- Test, verification, root cause analysis and reflection

- How to deal with high volume and big data

Open access, content overview and web page

|

|

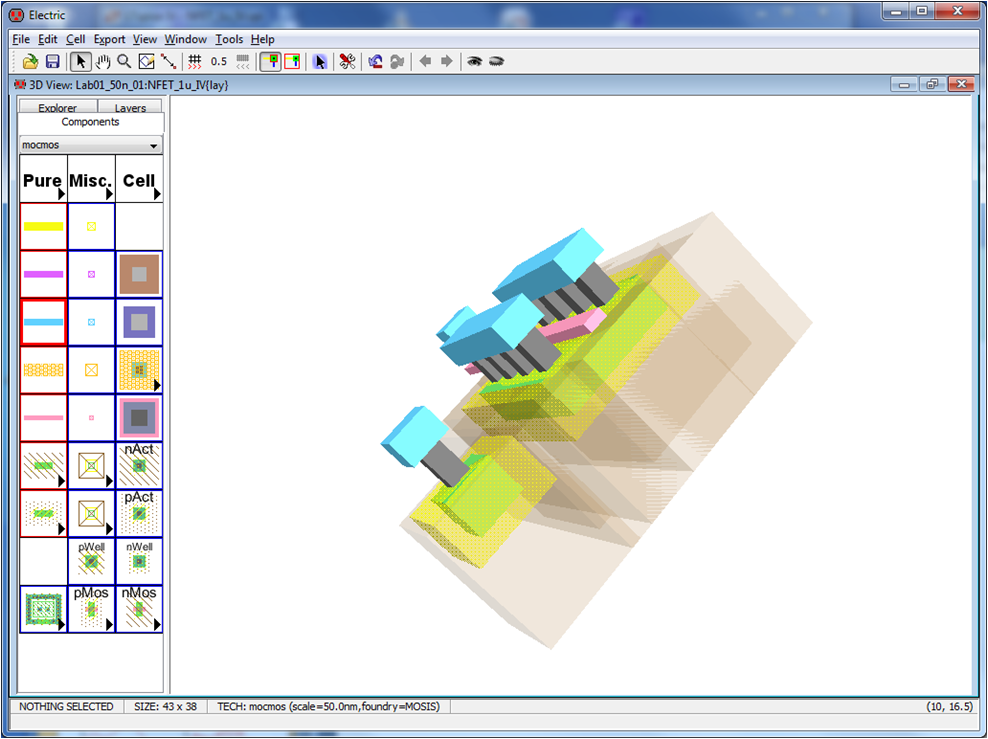

CMOS Manufacturing process animation

Top view:

Cross section:

0

This animation is done via JavaScript and can be directly operated in the browser.

It is easy to copy it and modify it.

LTSPICE schematic: Scan cell

|

<canvas id="Scan_cell_small_CE" width="300" height="250"

level="0" class="LTSPICE" sym="NAND2,TG,INVx,AND2,OR2"> </canvas>

A scan cell is used in this class to emphasize design for test.

This cell can be designed by hand or generated with the silicon compiler.

This cell can be designed by hand or generated with the silicon compiler.

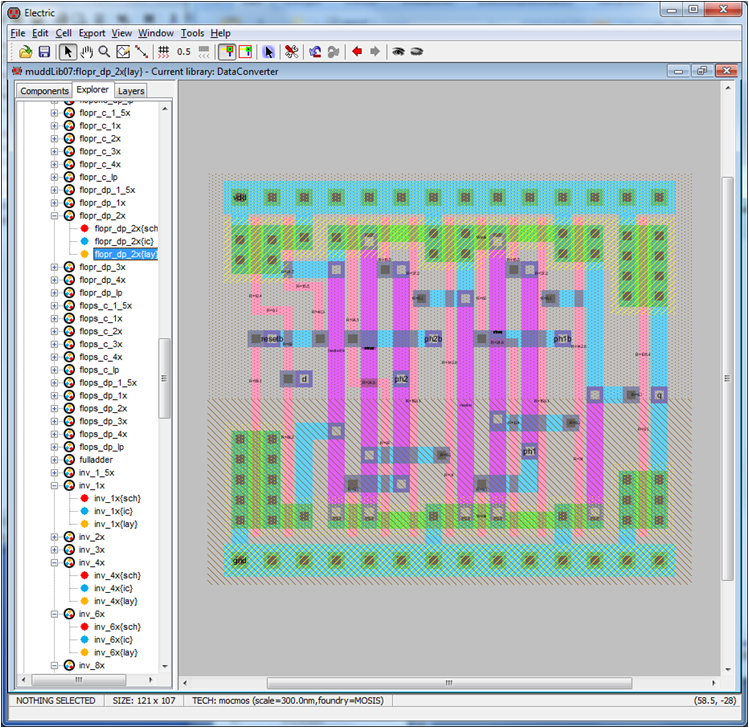

Electric design and layout

|

Java program using a portable Java No cost

|

Electric VLSI Design System |

Electric has most of the tools of a commercial software.

The results are not optimum, but the students learn what to expect from a

design software.

They also experience all the difficulties of engineering software, which has no perfect user interface, but has to work somehow.

They also experience all the difficulties of engineering software, which has no perfect user interface, but has to work somehow.

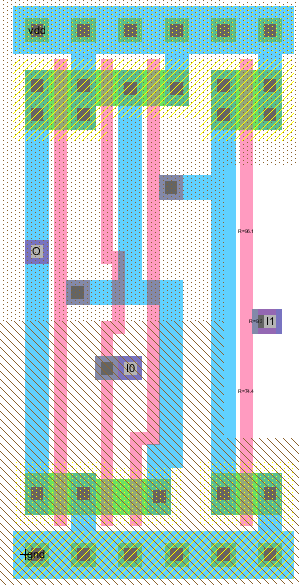

Scan cell example

- Silicon compiler generated layout from schematic

- Routing rules: M1 horizontal, M2 vertical

- Gaps between the cells

- Minimum transistor size

- Cell size more limited by connections than by transistors

UART example

Open Laboratory

|

|

Cells for synthesis

Students designed 39 basic cellsLogic verification with simulation

|

|

These cells are necessary to realize all possible 2 input truth tables (16)

and to realize the Spartan 3 FPGA primitives..

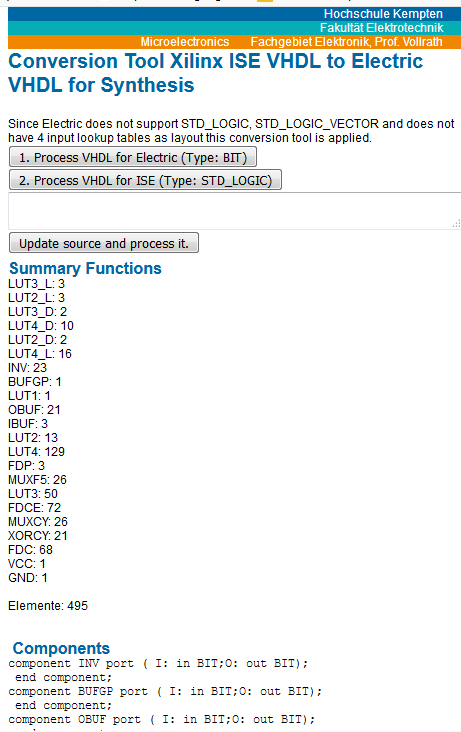

AnalyzeJS.html

Glue script between Xilinx Webpack

and Electric for VHDL

|

AnalyzeJS.html |

The script is realized using JavaScript and accessable from the internet.

Using node.js it can also be employed in a regular tool chain.

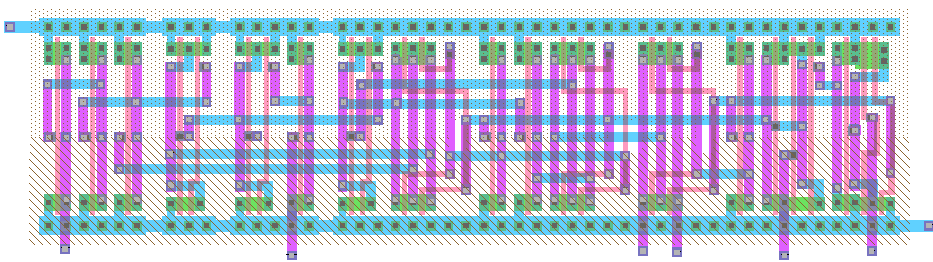

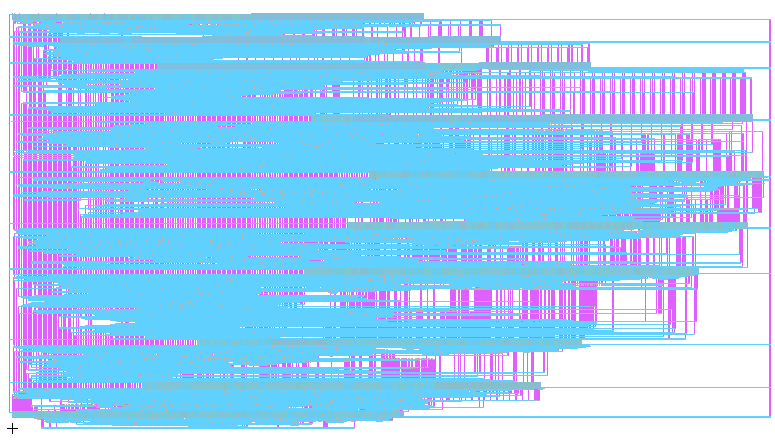

Synthesis Result Layout

Synthesis took 2..3 minutes.

Area: 14554 x 7938 F2; 10 rows;

Synthesis design rules: 4, 3, 32, 8, -9

Tools: DRC: Check Hierarchically: cells ok

uart_test takes a long time.

Outlook

Summary:

- Open access documentation and laboratory successfull

- LTSPICE can be easily documented and shared

- No cost VHDL synthesis successfull

- Sucessfull web tool for VHDL translation implemented

- Web tools and pages are easily maintainable and accessable

- All tools are also working locally from file system

- It is very easy to update a web page

Outlook:

- Improvement of LTSPICE display

- Web layout display and generation tool

- Routing with more than 2 layers metal

- Routing in a chip frame

- Improvement of documentation

- IRSIM simulation

- Chip fabrication

Questions

|

Thank You ! |