Microelectronics02 HistoryProf. Dr. Jörg Vollrath01 Introduction |

|

Video of lecture 03 24.03.2021

|

Länge: 1:02:33 min |

0:0:54 Transistor, Layout, Cross Section 0:4:5 Transistor count 0:9:5 Moore's Law: Feature Size 0:13:0 Microelectronics over time 0:16:20 iFixit iPhone Analysis 0:18:5 iPhone Main Board 0:19:40 Blessing and Curse of Microelectronics 0:22:48 Design Entry 0:27:5 Software Tools 0:28:35 Integrated Circuit Challenges 0:29:55 Laboratory: Build a 4 bit positive number multiplier 0:32:43 Hierarchical description, one solution 0:36:40 Citations: Don't optimize too early. 0:39:19 Design flow 0:43:25 Technologies 0:47:15 Inverter schematic 0:49:45 Truth table 0:51:13 Source drain, schematic, color, layout box 0:54:5 Stick diagram 0:56:13 What do I do with 1 billion transistors? 0:57:32 Inverter schematic and layout 1:2:5 p-well and n-well 1:5:57 p-well and n-well contact 1:8:31 Layout well contact 1:12:45 F and lambda 1:13:29 N-MOSFET equations 1:16:16 β, width W, length L, capacitance Cox 1:22:4 0 |

Review and Overview

- Welcome

- LTSPICE

Netlist, elements, nodes, simulation mode, waveforms

- Companies

- References

- Transistor Evolution, Moores Law

- Blessing and curse of microelectronics

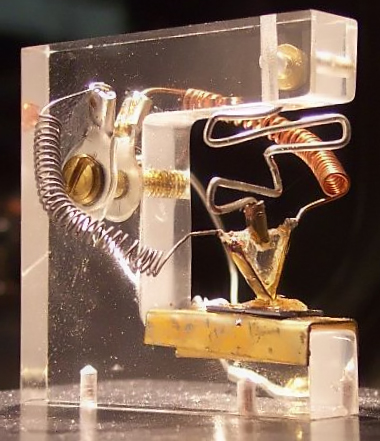

Transistor Evolution

Quelle: Wikimedia 1947 Bell 1 Bipolar transistor 30 μ m 50 MHz |

|

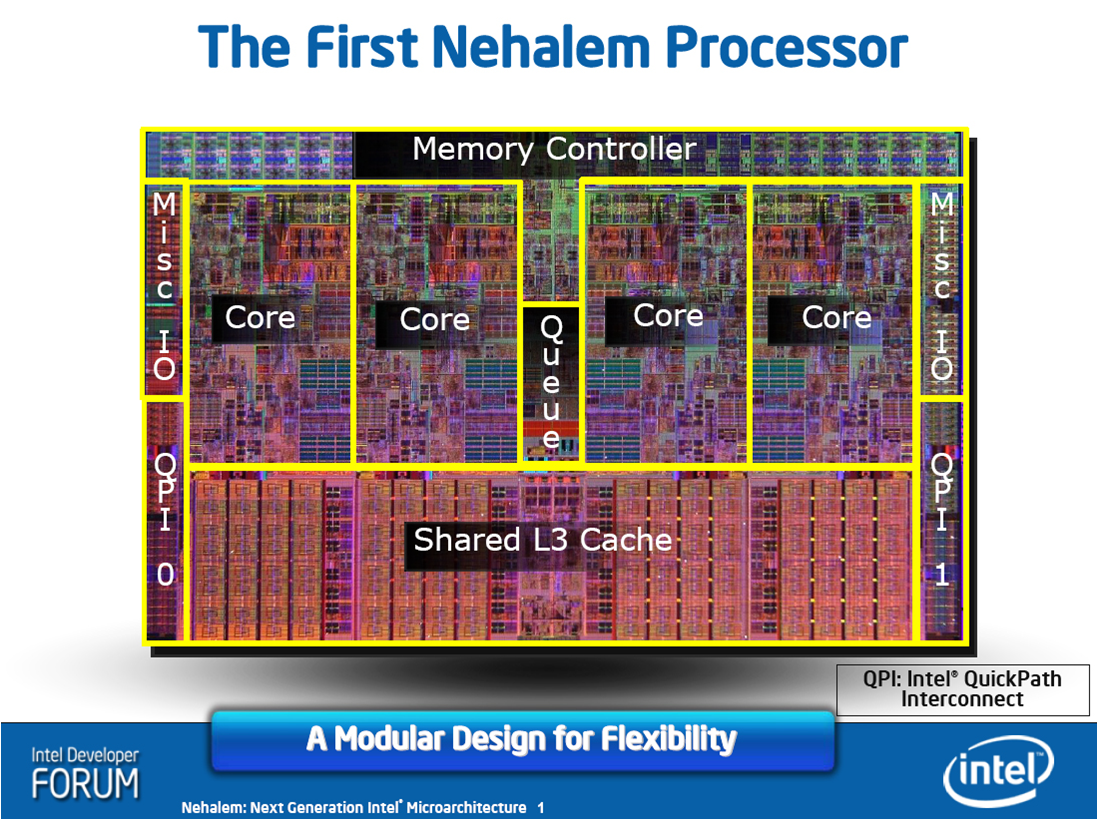

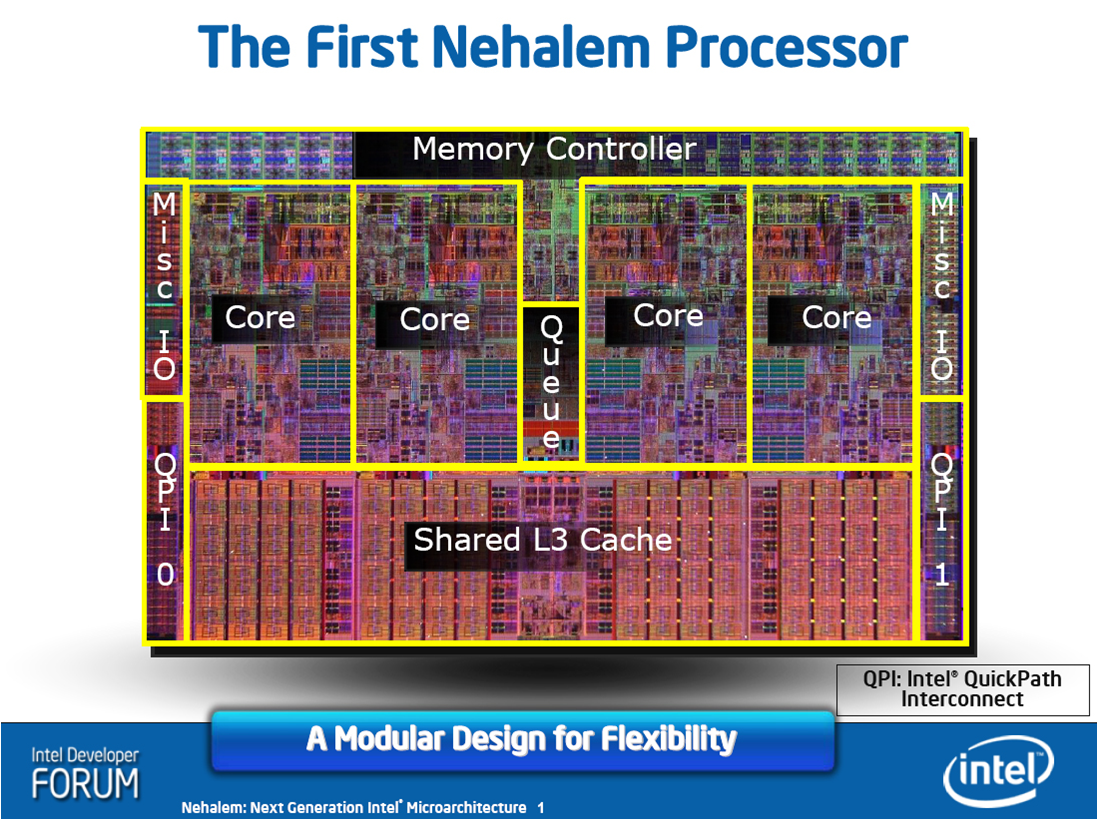

Courtesy of Intel 2008 Intel Core i7 731 Million MOS Transistors 45 nm process 263 mm2 2.6..3.2 GHz |

It can be seen that the Intel Core i7 has 731 million transistors

in a process using 45nm feature size on an area of 263 mm2.

As an critical thinking engineer it is important

to be able to check statements, claims and facts.

In this example the number of transistors for the given chip area is checked. A single transistor needs a minimum size of 16 F2 as seen before. The number of transistors is chip area (AChip) divided by transistor area (AMOSFET).

263 mm2/(16 * (45nm)2) = 8117 Mio Transistors.

This is a factor of 11 higher than the claimed 731 million transistors.

In highly integrated chips the total size is not limited by the area of transistors, but by the area needed for contacts and wiring.

In a microprocessor one transistor needs around 180 F2. This number is important for estimation of chip area for a given circuit with a given number of transistors.

Links:

http://www.intel.com/pressroom/archive/releases/2008/20081117comp_sm.htm

http://download.intel.com/pressroom/kits/corei7/images/Nehalem_Die_Shot_3.jpg

http://www.tomshardware.com/de/Core-i7-Nehalem,testberichte-240172-2.htm

https://en.wikipedia.org/wiki/List_of_Intel_Core_i7_microprocessors

In this example the number of transistors for the given chip area is checked. A single transistor needs a minimum size of 16 F2 as seen before. The number of transistors is chip area (AChip) divided by transistor area (AMOSFET).

263 mm2/(16 * (45nm)2) = 8117 Mio Transistors.

This is a factor of 11 higher than the claimed 731 million transistors.

In highly integrated chips the total size is not limited by the area of transistors, but by the area needed for contacts and wiring.

In a microprocessor one transistor needs around 180 F2. This number is important for estimation of chip area for a given circuit with a given number of transistors.

Links:

http://www.intel.com/pressroom/archive/releases/2008/20081117comp_sm.htm

http://download.intel.com/pressroom/kits/corei7/images/Nehalem_Die_Shot_3.jpg

http://www.tomshardware.com/de/Core-i7-Nehalem,testberichte-240172-2.htm

https://en.wikipedia.org/wiki/List_of_Intel_Core_i7_microprocessors

History of integrating microelectronic circuits

- 1947 Bipolar Transistor invented by Bardeen, Brattain and Shockley at Bell Laboratories

- 1958 Simultaneous Development of Integrated Circuit by Kilby at Texas Instruments & Noyce and Moore at Fairchild Semiconductor

- 1961 First commercial digital IC available from Fairchild Semiconductor

- 1967 First Semiconductor RAM (64bits) discussed at the IEEE International Solid-State Circuits Conference (ISSCC)

- 1968 Introduction of the first commercial IC operational amplifier the µA709 by Fairchild Semiconductor

- 1970 1-transistor dynamic memory cell invented by Dennard at IBM

- 1971 Introduction of the 4004 microprocessor by intel

- 1972 First 8-bit Microprocessor The Intel 8008

- 1974 First 1kBit memory chip, 8080 microprocessor

- 1978 First 16-bit Microprocessor

- 1984 1MBit Memory chip

Electronic components

- 1906 vacuum tube

- 1958 First integrated cicuit:

More than one transistor next to each other on the same die - 1970 Intel i1103 1kBit DRAM

- 1972 Intel 8008

http://en.wikipedia.org/wiki/File:RCA_%E2%80%99808%E2%80%99_Power_Vacuum_Tube.jpg

http://www.ti.com/corp/docs/company/history/tihistory_subpage1.shtml

http://www.icknowledge.com/history/1970s.html

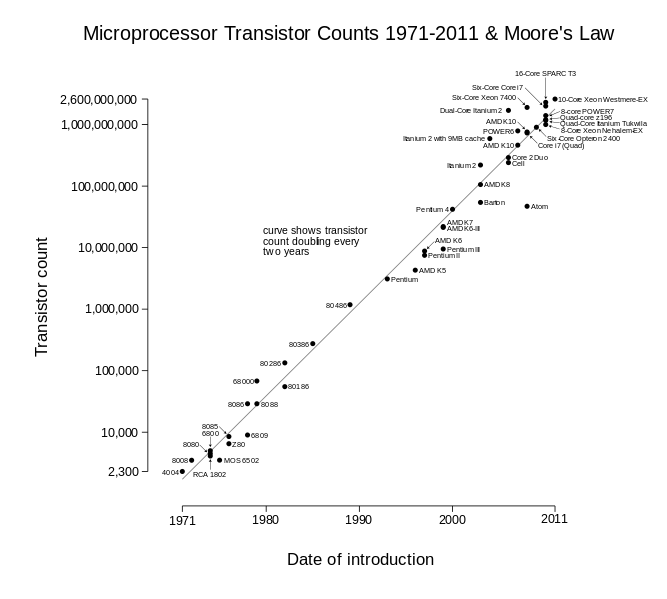

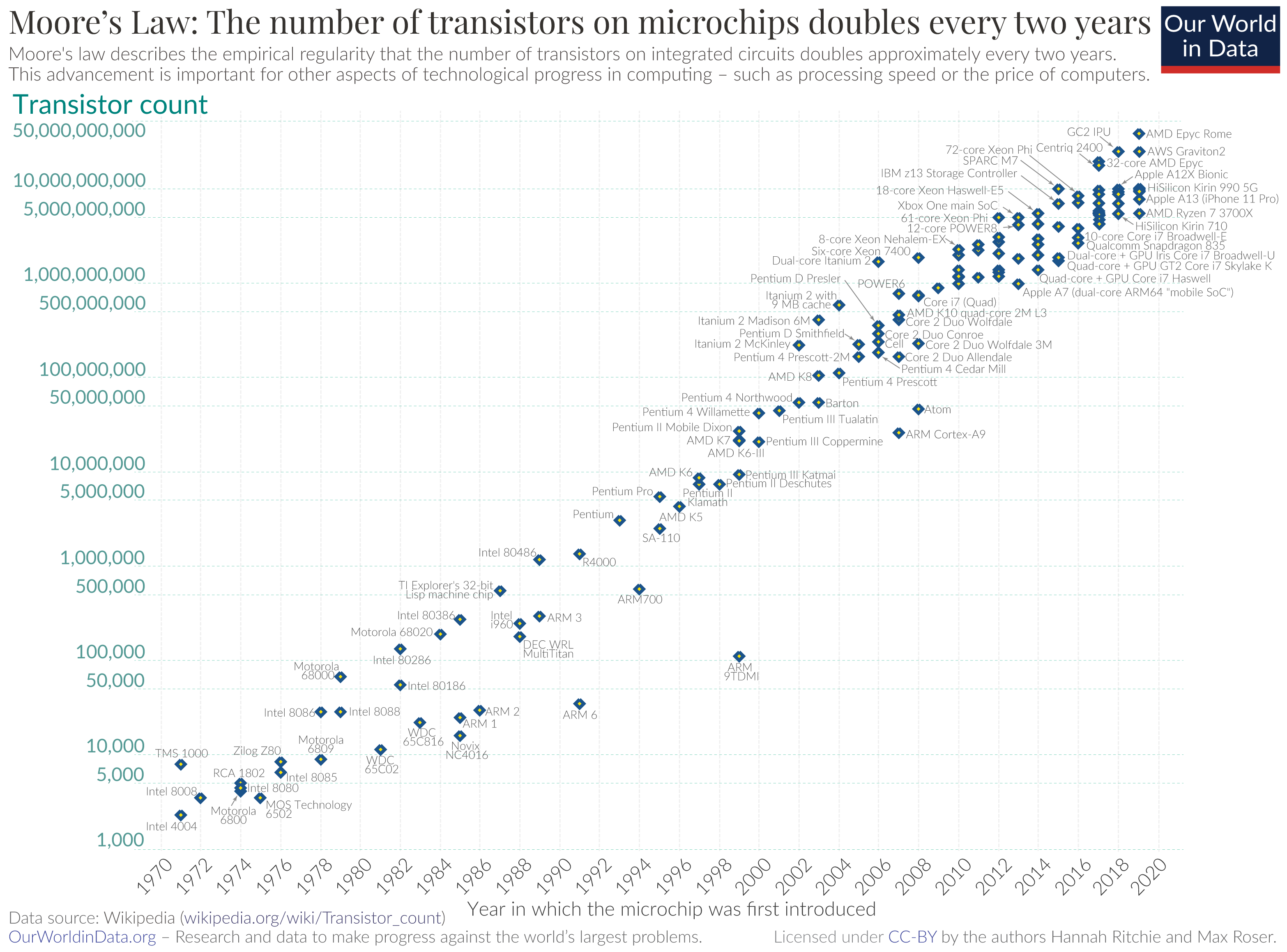

Moore's Law: Transistor count 2020

Every 2 years the number of transistors per area doubles.

Each year manufacturing productivity gains are about 30%.

Microelectronics over time

Benefits

- More transistors per area

- More functions per area

- Less cost per function

Challenges

- How to decrease feature size

- How to handle complexity

- How to design and test circuits

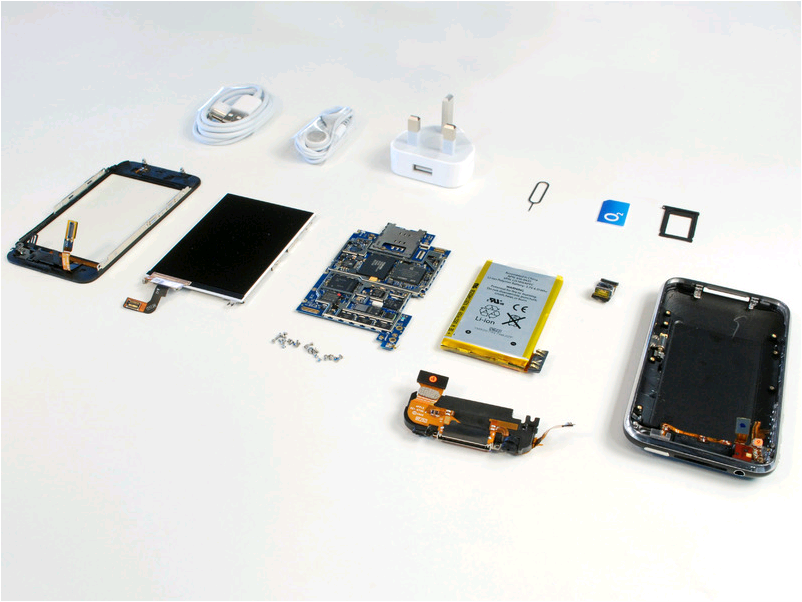

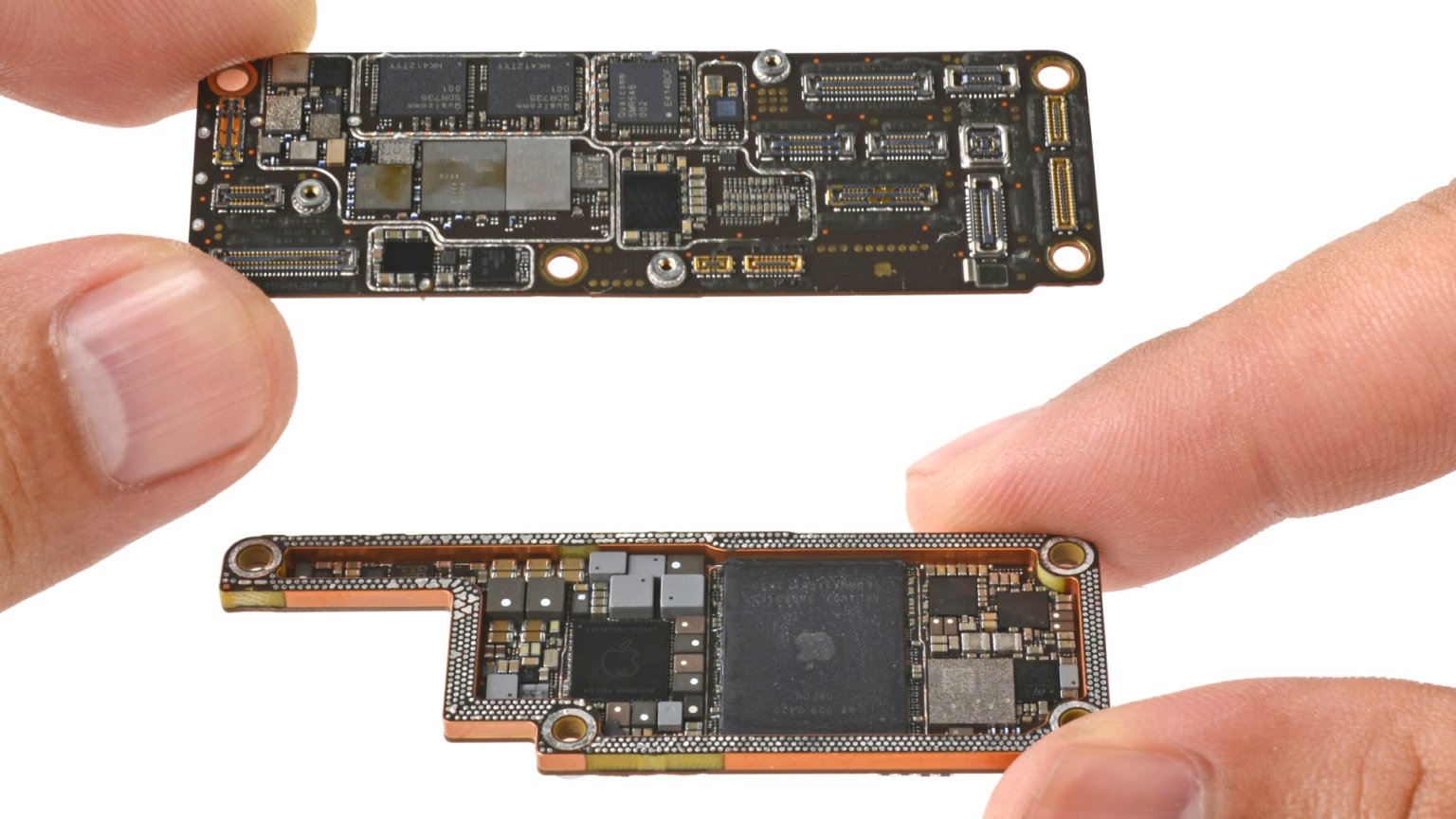

Mobile phone components

| A18 SoC, 8GB LPDDR5 SDRAM, Kyoxia 128GB NAND Flash-Speicher |

|

It is also very interesting to see the 3D integration since one PCB sits on top of the other.

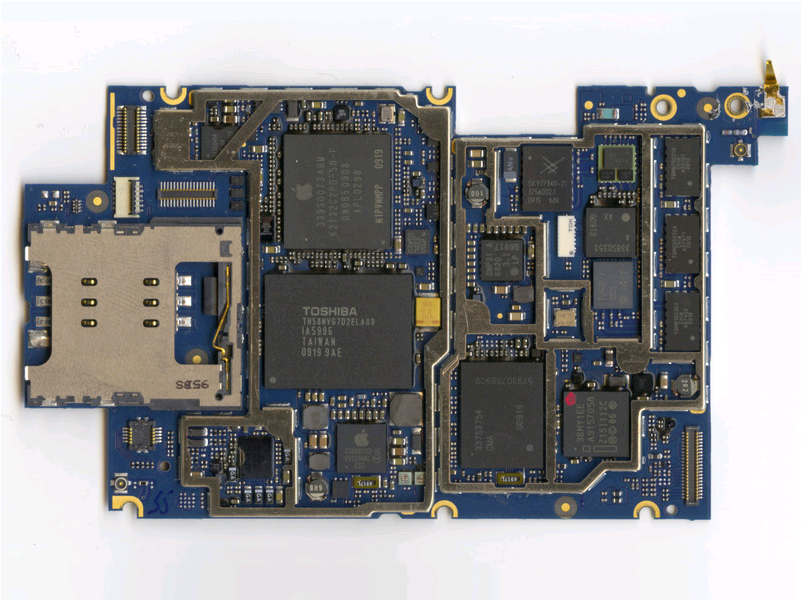

Mobile phone main board

Source: iFixit CC BY-NC-SA 3.0 |

Samsung ARM processor S5PC100 600MHz 16 GB of Toshiba NAND flash memory NOR Pseudo SRAM Numonyx 256MB DDR SDRAM Analog Broadcom, Infineon Power Management Infineon, NXP |

Blessing and curse of microelectronics

Design and manufacturing- Each year a new model hits the market

- More features (Flash Memory, Camera, sensors, protocoll)

- Lower price

- Each year manufacturing productivity gains are about 30%

Blessings:

- New products are possible

- Everything gets cheaper

Curse (Challenge):

- Tight schedule for product development and sales

- Constant improvement is needed

- Electronics are getting more complex

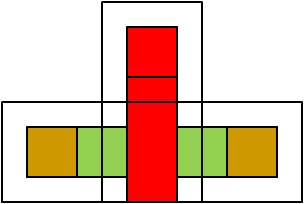

MOSFET Transistor

Quelle Vollrath

Quelle Vollrath

|

Quelle Vollrath

Quelle Vollrath

|

| Technology | RN | RP | COX | Vthn | VDD | IDD | gmmax | gdmax | ft | Model |

| 1 μm | 15kΩL/W | 45kΩL/W | 1.75fF WL/F2 | 1V | 5V | 3 mA | cmosedu_models N_1um | |||

| 600 nm | ΩL/W | ΩL/W | fF WL/F2 | V | mA | C5_models | ||||

| 50 nm | 34kΩ/W | 68kΩ/W | 62.5aF WL/F2 | 0.3 V | 1 V | mA | cmosedu_models N_50nm |

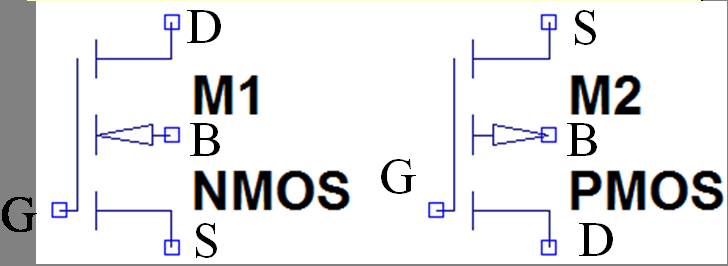

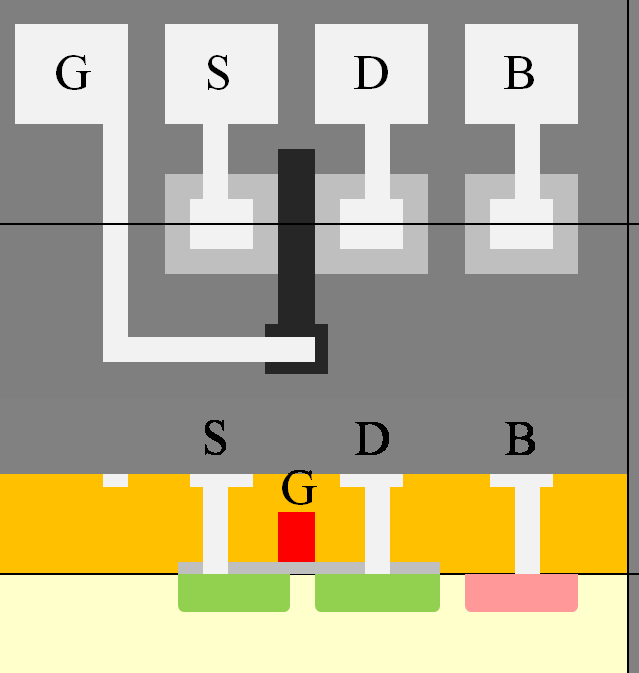

MOSFET

A MOSFET (Metal oxide semiconductor field effect transistor) has the terminals gate (G), source(S), drain(D) and bulk(B). The gate controls current flowing between source and drain. There is a threshold voltage Vth which is needed to enable current flow. A bulk potential and bulk connection can change threshold voltage. Therefore bulk connections are needed to guarantee a stable threshold voltage.

There are enhancement mode PFETs and NFETS available making CMOS (complementary MOS) circuits possible. Enhancement mode FETS have a threshold voltage so that no current is flowing with 0V between source and gate.

NFETs have a positive threshold voltage, PFETS have a negative threshold voltage.

Transistor representation

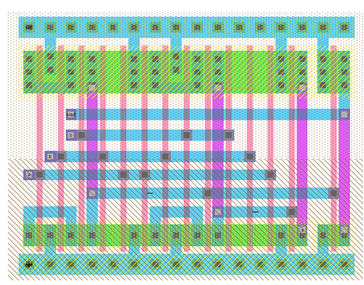

Transistors as electrical components can be small black boxes with 3..4 wires. They are represented in a schematic as a symbol. In microelectronics a transistor is represented by a red rectangle (polysilicon) crossing a green rectangle (diffusion). Connections betweeen different colored areas are represented by black boxes between overlapping colored rectangles. Metal lines for connections are drawn as blue, violet or pink boxes.

In microelectronics circuits are built by transfering a transistor schematic to a layout (colored shapes). There are design rules limiting the size and distance of these colored boxes due to the limitations of the manufacturing process.

Minimum feature size and transistor area

The minimum total area of a transistor is based on the minimum feature size F.

The minimum feature size is the smallest pattern which can be realized in a given manufacturing process. The minimum feature size is depending on the wavelength of the used light source for the photoprocess used to transfer patterns with a mask onto the photoresist on a chip. A MOSFET uses at least 3 connections with minimum square area of F2. Since there should be no shorts a distance to the next feature should also has a minimum distance of 1 F. Therefore 3 connections and one active transistor area, where a red and green line are crossing, with isolation require:

4 * 4 F2 = 16 F2

Tools

- LTSPICE

- Circuit Simulator

- http://www.linear.com/designtools/software/

- Electric

- EDA (Electronic Design Automation) Software

- Layout, Schematic Editor, Simulator and other Tools

- http://www.staticfreesoft.com/index.html

- ISE Webpack

- https://efabless.com/designers/

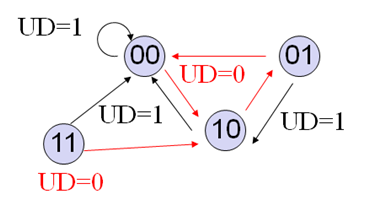

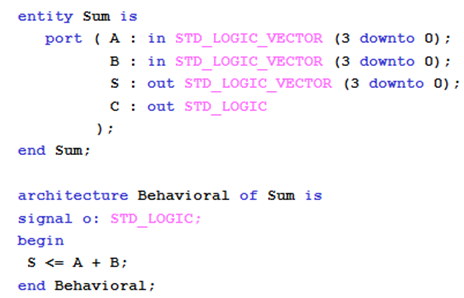

Design Entry

|

Schematic Layout Graphical State machine VHDL SystemC C/C++ |

|

|

Result: Integrated Circuit

Courtesy of Intel

http://www.intel.com/pressroom/archive/releases/2008/20081117comp_sm.htm

http://download.intel.com/pressroom/kits/corei7/images/Nehalem_Die_Shot_3.jpg

Integrated Circuit Challenges

- Design a circuit first time right:

- It has to work the first time, since chip manufacturing and mask design is costly and time consuming and measurement is very difficult.

- Geometric shapes in different layers define transistors, resistors and capacitances

- Circuit simulations will replace breadboard assembly and measurement

- Layout with Electric will replace wiring of components

- Tools:

- Usage of LTSPICE and Electric

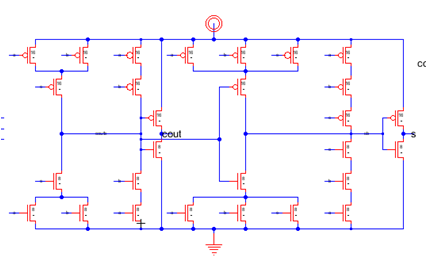

2025 Serial CPU Investigation

|

|

Lecture and Laboratory

2022 Compare Adder Architectures

- Review of articles: IEEE Explore

Analysis and Comparison on Full Adder Block in Submicron Technology

Compare_Full_Adder.pdf

Two New Low Power High Performance Full Adders with Minimum Gates

v4-10-100_Full_adder_minimum_transistors.pdf

- What adder architectures are presented?

- What simulations are done?

- How does the layout look like?

- Different groups design the layout, schematic of different adders, drivers and load

Is there an optimum layout? - Simulation and comparison with various feature sizes

Lecture and Laboratory

2021 Build a 4 bit postive number multiplier

- Bottom up:

- Transistor, logic cell, register, floor plan

- IV curves, timing behaviour, system simulation

- Single transistor drawing, gates, cells, blocks, system

- Tools:

- Usage of LTSPICE and Electric