Microelectronics12 Power, Clock, IO, MicroelectronicsProf. Dr. Jörg Vollrath11 Memories |

Video of lecture 12 (19.05.2020)

|

Länge: 1:01:57 |

0:0:0 Microelectronics 0:0:59 Story complex systems 0:5:30 Test 0:7:5 Power equations 0:10:26 Power, VDD, delay 0:12:5 DRAM IDD Specification 0:15:46 Dynamic current analysis 0:19:2 Ring oscillator 0:22:24 Bypass capacitances 0:24:42 Power grid 0:27:16 Internal voltages power on sequence 0:32:26 Power system model 0:35:54 Memory chip package 0:37:54 Clock 0:38:39 Clock distribution 0:43:7 Clock examples 0:45:46 Package 0:49:19 Package parasitics 0:50:13 SPICE simulation and measurement 0:53:23 Input and outputs 0:59:15 FPGA IO pads 1:0:36 Chip with pads |

20.5.2020 Review of laboratory status

You should not use M3 or M2-M3 contacts.Load and source should be comparable to input capacitance and output resistance of DUT cell.

Make versions of your cell: Duplicate with name and version number.

Transistor size in schematic and layout should match.

Tools-NCC-Schematic and layout

File-Preferences-Tools-NCC-Check transistor sizes

Select metal2 and the draw a line in M2.

Exports should be in M1-M2 contact.

Measurements statements can be included in the LTSPICE file and results are written in a log file.

Placing a contact does not yet make connection. You have to do it afterwards by connecting lines.

Overview

Review:- Memory: Type, Array, Realization, Trends

- SRAM, DRAM, Flash

Today:

- Power

- Clock

- Package: Physical design, parasitics, heat, power

- IO Pads (Input and Output): Level, noise, ESD

Microelectronics story

How to build complex systems and plan progress

- Bottom up, characterize (simulate), reuse, simple solution, no optimization

- Rules help to keep it simple: Design rules, standard cells, rules for yield

Make automation easy - Silicon compiler, VHDL helps to assemble complex circuits automatically

- High level design VHDL, high level simulation IRSIM.

- Top level: SystemC, Matlab/Simulink, Labview (not yet in this class)

- Circuits and Test: Inverter, AND, OR, AOI, TG, Flip-Flop

- Microcontroller (datapath, ALU, random logic) comparator, adder, multiplier, shift

- Reuse of IP: read, understand, verify with simulation

- Test for reuse and yield

- Memory array, data flow

- Timing closure

- Power, clock, IO

- Chip assembly

- Test for yield and diagnostic

Power

Instantaneous power

P = v(t) · i(t)

Average power

Pavg = Average(v(t) · i(t)) = Vrms,DD Irms,avg

- Standby:

Diode leakage, transistor off current - Active:

Charge and discharge of capacitance

Cross current at switch point: NFET and PFET simultaneously on

Analog bias currents

\( I = \frac{C \cdot V}{t} = C \cdot V_{DD} \cdot f_{CLK} \)

\( P_{act} = C \cdot V_{DD}^2 \cdot f_{CLK} \)

Power discussion

- High clock frequency has maximum power

Clock frequency of small devices is limited by allowed power density - Supply voltage

Lower voltage gives lower power: P∝ V2

higher RDSon, higher tPD, lower fCLK

- Voltage limits:

Upper limit: transistor breakdown

Lower limit: transistor threshold voltage, variation, delay

- Optimum performance for power and speed:

Regulated voltage

Clock frequency variation and clock gating

Time and space

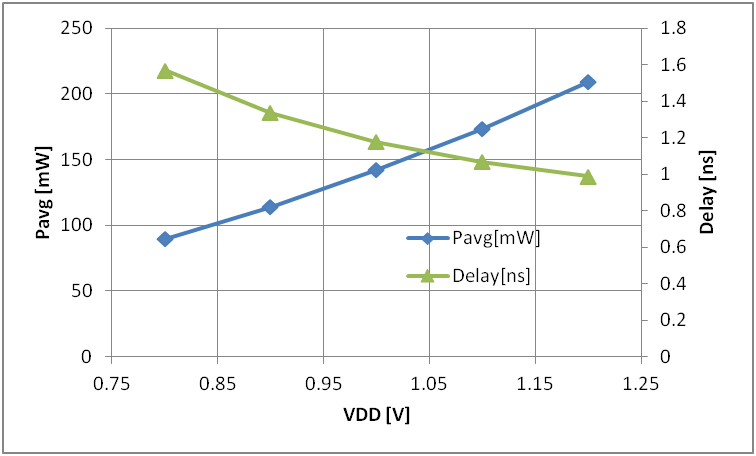

Power and Speed

|

|

Performance of a semiconductor process can be measured using a ring oscillator.

The ring oscillator connects the output of an odd series of inverters with the input creating an unstable feedback.

The oscillator frequency is limited by the propagation delay of the inverters.

This measures the RDSon, Cin and ft.

The ring oscillator connects the output of an odd series of inverters with the input creating an unstable feedback.

The oscillator frequency is limited by the propagation delay of the inverters.

This measures the RDSon, Cin and ft.

DRAM IDD Specification

Micron 256Mb DRAM -5B, VDD = 2.6 V, MT46V32M8

| Operating one-bank precharge current | IDD0= 75 mA |

| Operating one-bank active-read-precharge current | IDD1= 85 mA |

| Precharge power-down standby current | IDD2P= 4 mA |

| Idle standby current | IDD2P= 23 mA |

| Auto refresh burst current | IDD5= 115 mA |

| Operating bank interleaved read current | IDD7= 175 mA |

There is a great variation in current. Receiver and driver circuits can be turned on and off.

The voltage has to be stable for all conditions.

The voltage has to be stable for all conditions.

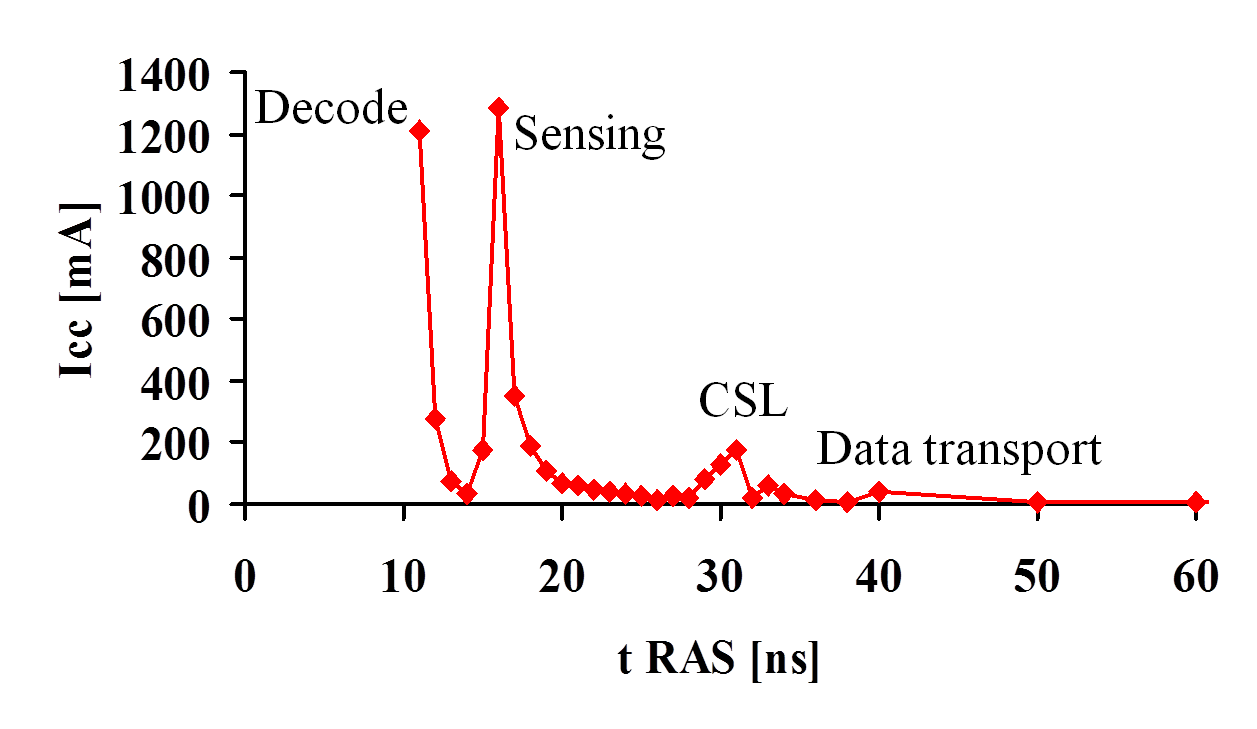

Dynamic power peaks and currents

|

DRAM dynamic read current

|

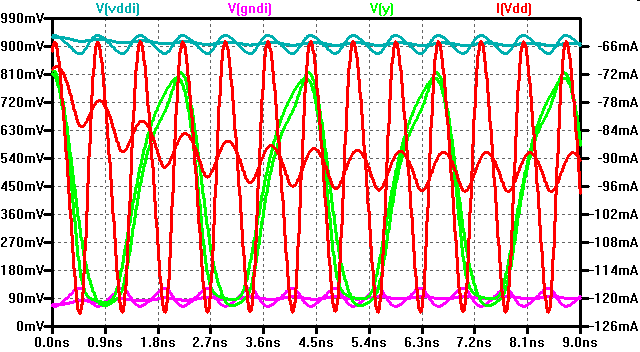

Ring oscillator power buffering with bypass capacitors

Simulation:

|

A ring oscillator shows the performance of a given semiconductor technology.

A 50 nm simulation shows a frequency of 500 MHz.

Series resistance in the power lines limits the voltage swing between 80 mV and 900 mV.

Average current is 93 mA.

The voltage level of gnd and vdd shows a ringing due to changing IDD.

Bypass capacitors can reduce the swing on the power lines, given more stable operation.

Not used area on chip can be filled with capacitance.

A 50 nm simulation shows a frequency of 500 MHz.

Series resistance in the power lines limits the voltage swing between 80 mV and 900 mV.

Average current is 93 mA.

The voltage level of gnd and vdd shows a ringing due to changing IDD.

Bypass capacitors can reduce the swing on the power lines, given more stable operation.

Not used area on chip can be filled with capacitance.

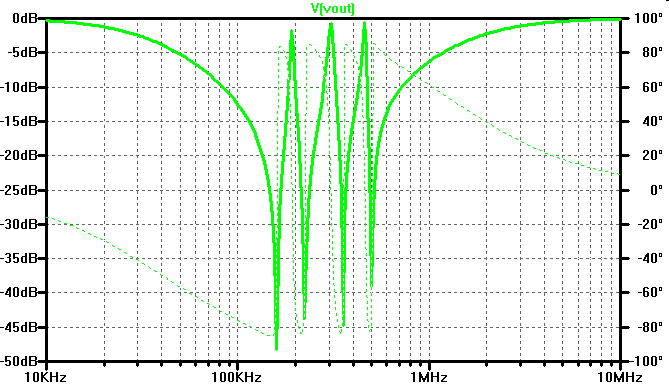

Real bypass capacitors

Frequency response of power capacitances:

|

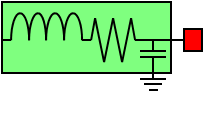

A real capacitance has a parasitic resistance and inductance.

There is a limited bandwidth for supply voltage stabilization.

A combination of many capacitances with optimized resistance and inductance is needed.

There is a limited bandwidth for supply voltage stabilization.

A combination of many capacitances with optimized resistance and inductance is needed.

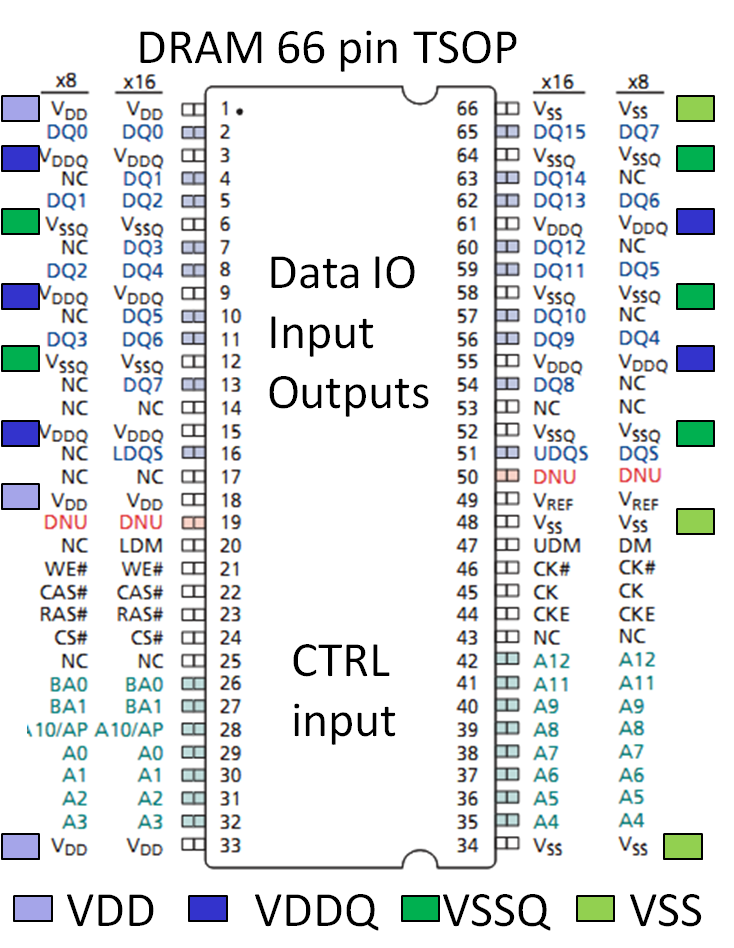

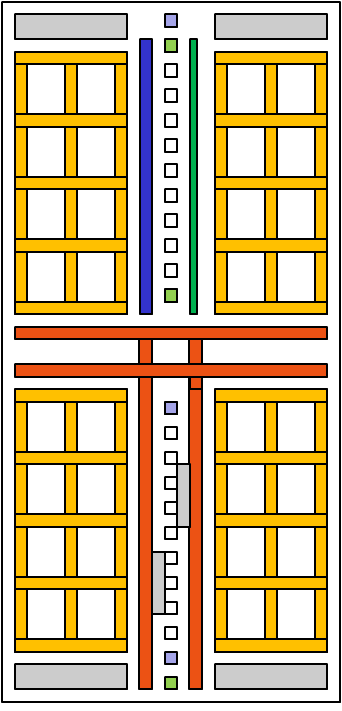

Power grid: DRAM example

|

|

There are separate power supply pins for the data input and outputs (IO).

The number of power pins is proportional to the number of IOs.

There are separate grids for digital and analog circuits.

Horizontal and vertical lines are connected to a grid and provide power.

The block diagram shows different voltages in different colors in different areas.

Voltage pumps and regulators are shown in grey.

A bandgap reference circuit provides temperature and voltage independent voltages.

The number of power pins is proportional to the number of IOs.

There are separate grids for digital and analog circuits.

Horizontal and vertical lines are connected to a grid and provide power.

The block diagram shows different voltages in different colors in different areas.

Voltage pumps and regulators are shown in grey.

A bandgap reference circuit provides temperature and voltage independent voltages.

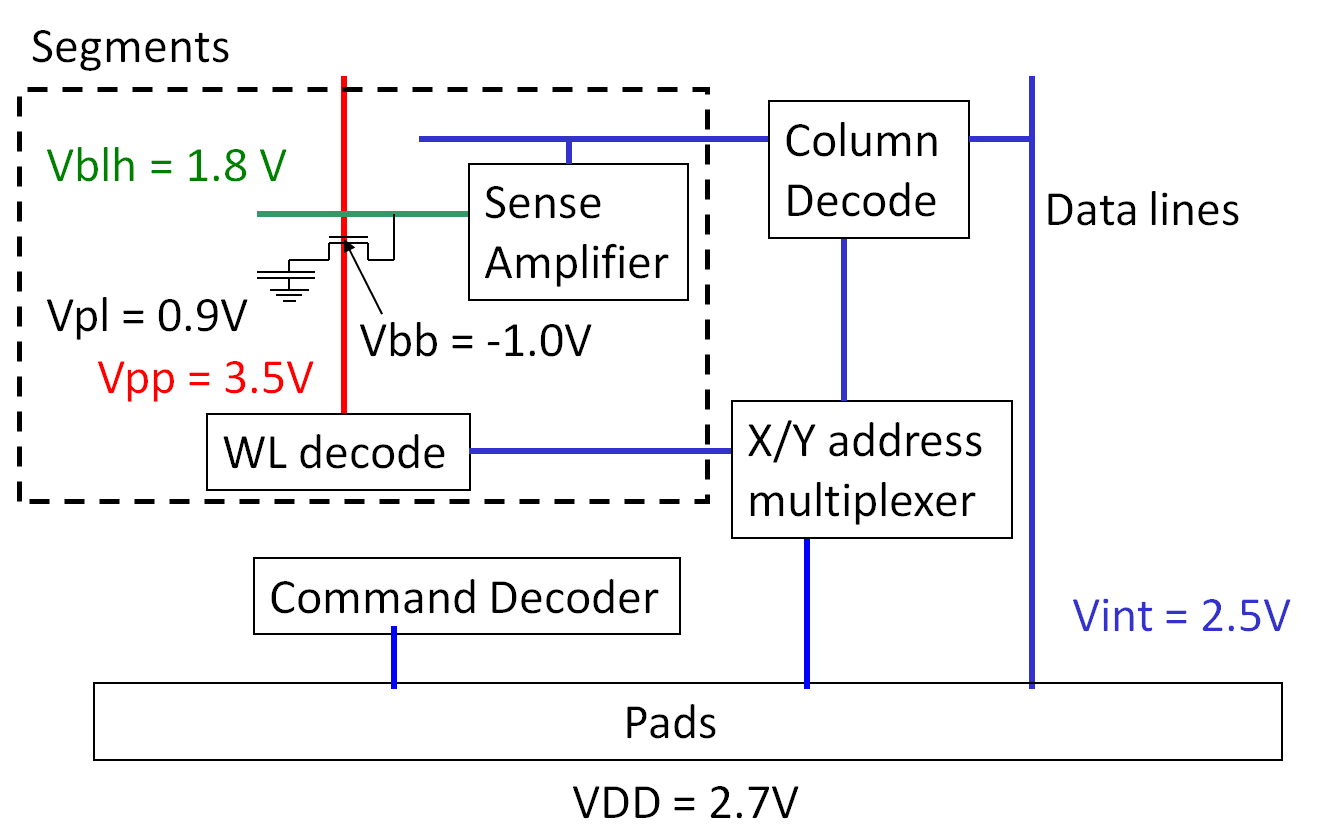

Power on sequence: DRAM

|

A low array voltage is used to save power.

A negative back bias is needed reducing memory cell leakage current.

A high voltage Vpp gives the select transistor overdrive to store the full Vblh level in the memory cell.

Vint is optimized for speed and to be able to drive the IOs.

A high current peak, when power is turned on, has to be avoided.

All capacitances will be charged up at power up.

A negative back bias is needed reducing memory cell leakage current.

A high voltage Vpp gives the select transistor overdrive to store the full Vblh level in the memory cell.

Vint is optimized for speed and to be able to drive the IOs.

A high current peak, when power is turned on, has to be avoided.

All capacitances will be charged up at power up.

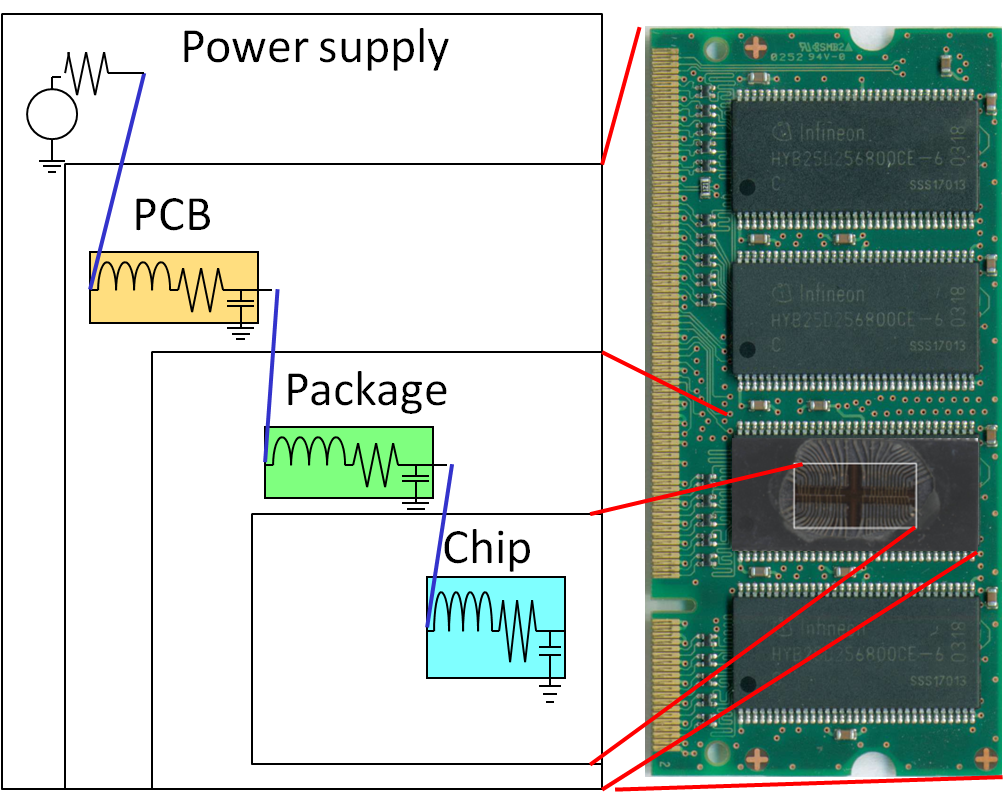

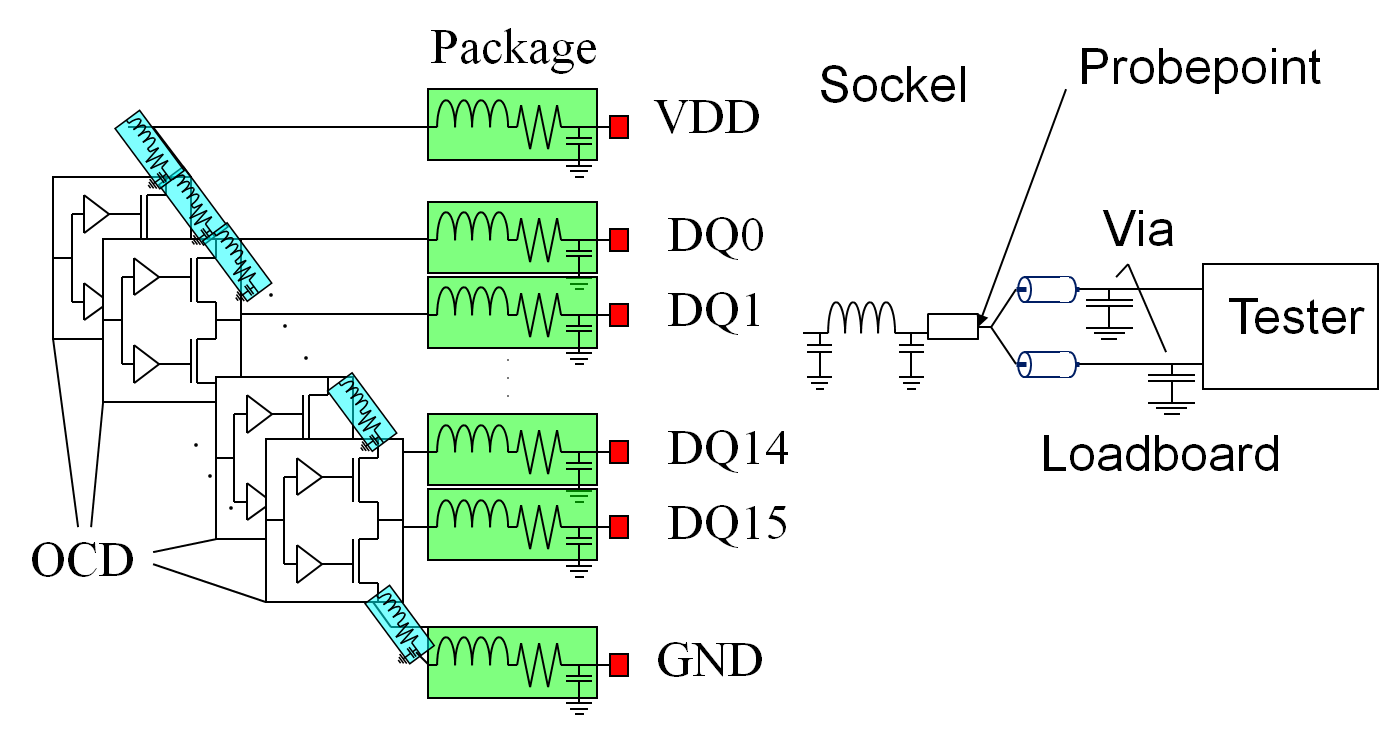

Power system model

|

|

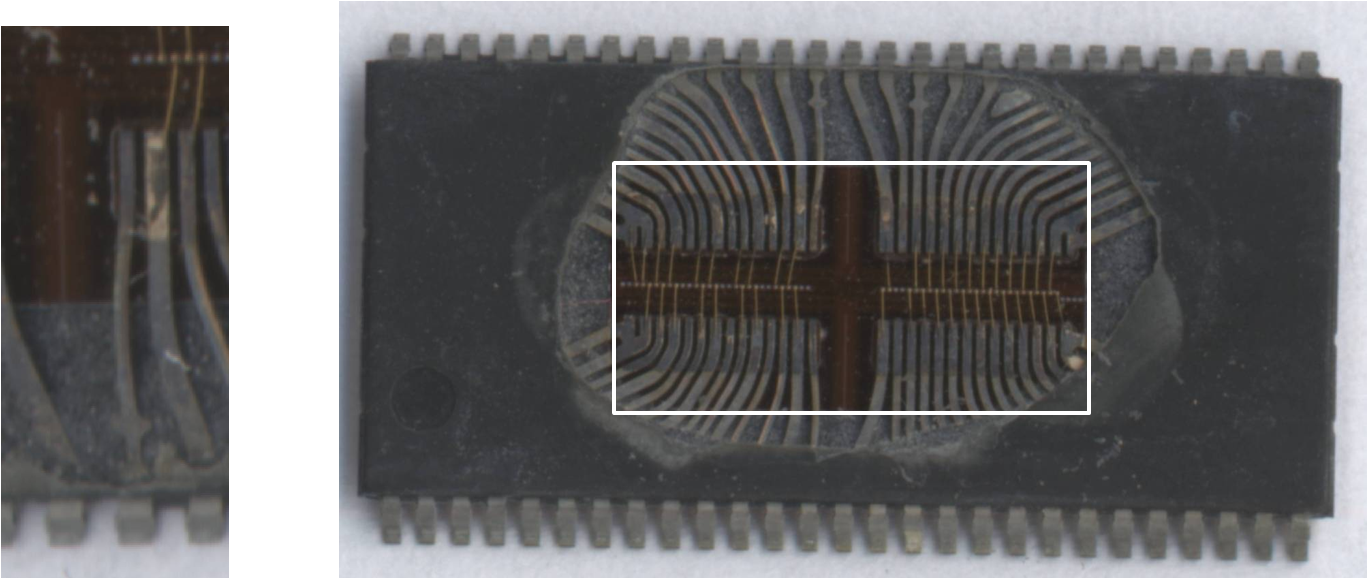

Memory chip package

This is a TSOP5 package used around 2005 for DRAM memories.

Nowadays memories use bga packages.

The package is smaller and has better high speed performance. It is more expensive than a TSOP package. Test and failure analysis is more difficult.

Nowadays memories use bga packages.

The package is smaller and has better high speed performance. It is more expensive than a TSOP package. Test and failure analysis is more difficult.

Clock

- Clock: single ended, differential, non overlapping (TBD)

- Clock skew and jitter (TBD)

- DLL and PLL (TBD)

- Clock tree and clock domains

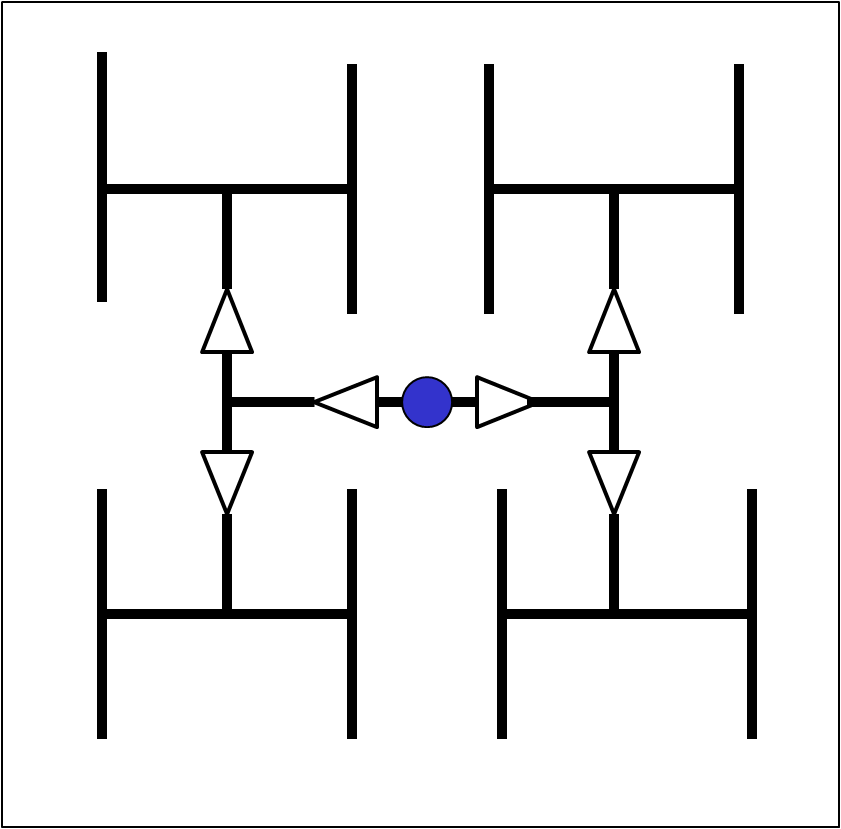

CLK Distribution: H-Tree and clock domains

H Tree

|

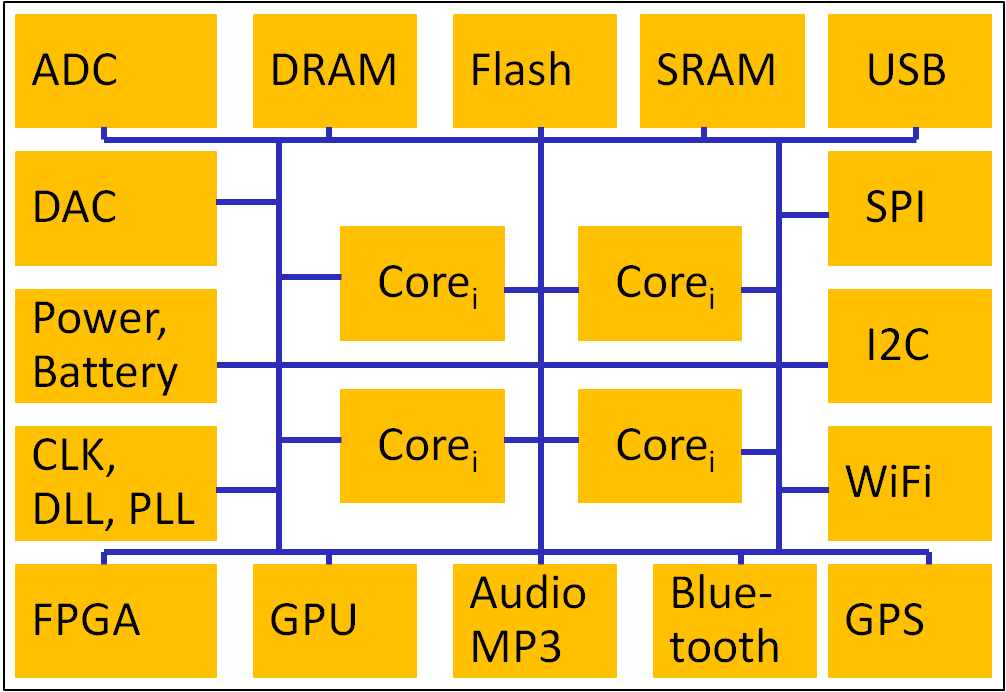

System on chip

|

Microprocessors have one central clock distributed via a balanced or unbalanced H-tree.

Systems on chip have many blocks with local clocks.

Communication is done via serial bus between clock domains.

Divide and conquer.

Systems on chip have many blocks with local clocks.

Communication is done via serial bus between clock domains.

Divide and conquer.

Power and clock Example

Dynamic random access memory (DRAM)

DLL for clock recovery for data alignment

Multiple internal voltages: Vpp, VBB, Vint, Vblh

Power up sequenceMicroprocessor (µP)

Single clock treeField programmable gate array (FPGA)

Multiple clock synthesis circuits (PLL, DLL)System on chip (SoC)

Multiple blocks with separate clocks (clock domains), communicating via serial links-

Data converters

Mixed signal design with low jitter clock

Package and Pads

|

Dual in line (DIL) Thin small outline (TSOP)  Ball grid array (BGA)  |

Package parasitics

Bond wiresGold bond wires connect the chip pads with metal lead frame. Thermal coupling is also achieved with bond wires and lead frame. Model: Inductance Capacitance Resistance |

|

SPICE simulation and measurement

Input and Outputs (IOs)

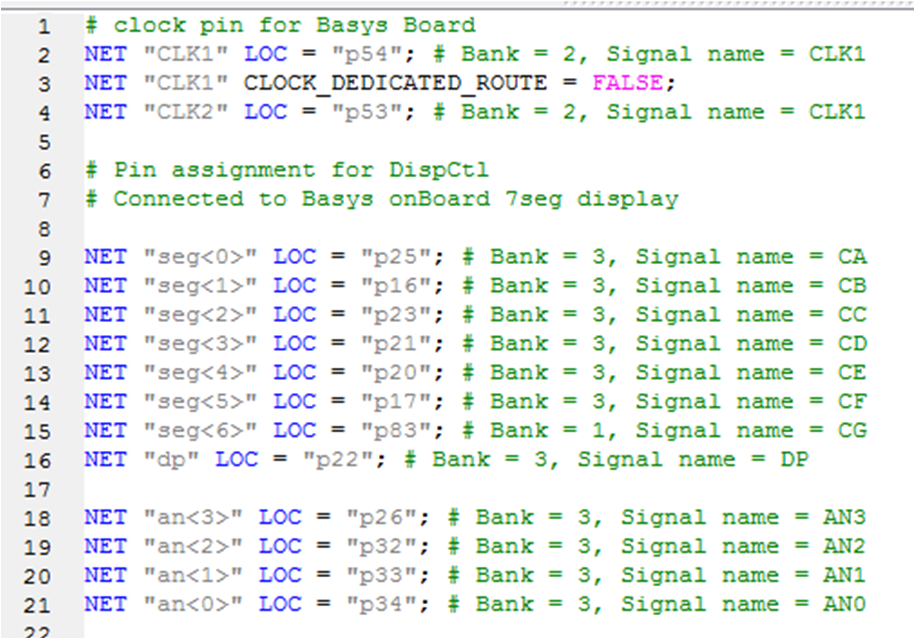

IO pads and pins in VHDL

User constraint file (.ucf)

|

|

References

Laboratory: TinyFPGA2018 TinyFPGA

Electric libraries:

muddpads13_ami05.jelib

pads4u.jelib

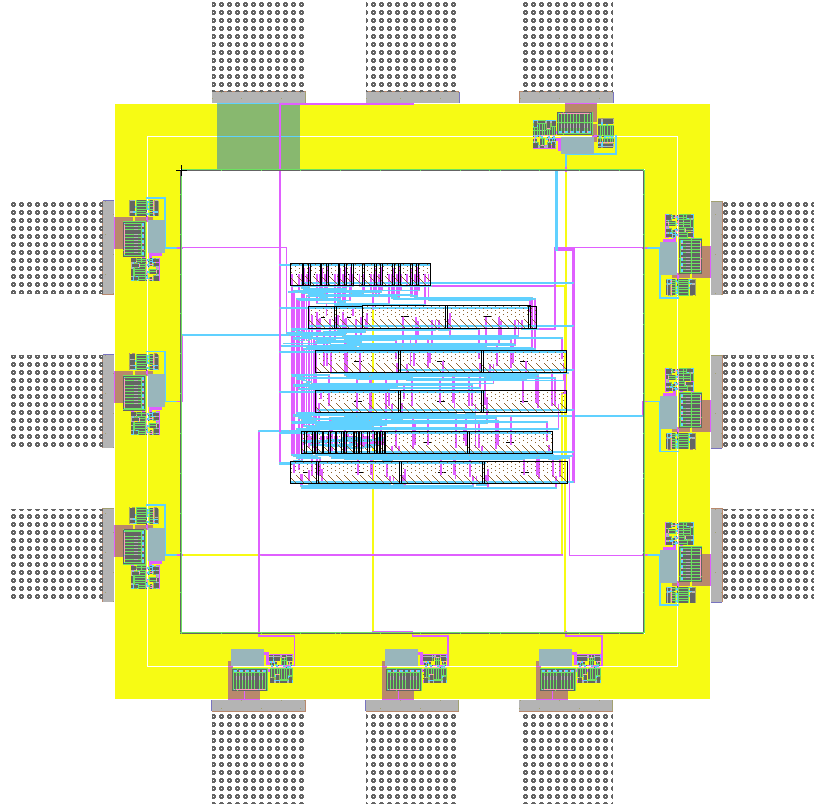

Electric: Tools -> Generation -> Pad frame generator

A configuration file (*.arr) allows automatic pad generation. Wiring can then be done with the Sea of gates route.

In the user manual an example is provided.

This example shows the pad frame not the active area to limit minimum chip size.

Alignment marks and labels for chip identification are missing.

Multiple chips are put on one reticle with a distance of 200 µm for sawing (dicing) to separate the chips.

Test structures are placed in this space to be able to monitor process performance.

MOSIS 0.35 µm IO Pads

MOSIS 0.35 µm IO Pads

Summary

- A power grid and bypass capacitors stabilize internal chip voltage

- There can be multiple clock domains with H-trees on a chip.

- IO Pads are provided by the manufacturer