Schaltungstechnik10/11 Operationsverst‰rkerProf. Dr. Jˆrg Vollrath09 Differenzverst‰rker Elektronik 3 Operationsverst‰rker |

|

Video der 10. Vorlesung 21.4.2021

|

L‰nge: |

0:0:0 Wilsonstromspiegel 0:2:55 Gleichtaktverst‰rkung 0:6:38 Eingangsspannung und Gate source Spannung 0:14:10 Diskussion vernachl‰ssigen 0:16:10 Folie Gleichtaktverst‰rker 0:18:0 LTSPICE 0:20:46 Ðbertragungsfunktion, Bodediagramm 0:22:10 Rechnung Differenzverst‰rkung 0:28:51 vd = 100 oder 40.6 dB 0:30:10 Gleichtaktverst‰rkung LTSPICE 0:31:20 Avgl = -46 dB 0:38:25 vgl1 = 1/gm7/rd5 = - 46 dB 0:43:44 CMRR = 86 dB (86 dB / 6 dB = 14 Bit) 0:47:8 Eingangs- und Ausgangsspannungsbereich 0:54:30 Operationsverst‰rker versus einfacher Verst‰rker 1:4:16 OpAmp Symbole 1:6:54 Erster Operationsverst‰rker 1:7:53 Realer Operationsverst‰rker 1:9:17 TLC272 1:12:35 Statische Parameter 1:19:0 Schaltbild vom TLC272 |

Video der 11. Vorlesung 27.4.2021

|

L‰nge: |

0:0:0 Arbeitspunkt 0:3:58 KP, KN, KN', beta 0:7:13 Bodediagramm Operationsverst‰rker 0:10:50 Transitfrequenz 0:15:0 Analyse mir Excel 0:19:10 Ðberlagerung Excelgleichung und Datenblatt 0:20:53 Verst‰rkung in dB 0:24:2 Ðbertragungsfunktion 0:27:0 Phase margin 0:27:42 Gain band width GBW = ft * 1 = f*Av(f) 0:30:0 Externe Beschaltung 0:31:51 LTSPICE Simulation 0:36:20 Datenblattwerte 0:38:45 OpAmp als Comparator 0:43:10 Hysterese 0:44:14 Rechnung Hysterese 0:50:42 Hysterese Spannung 0:53:35 Zeichnung Hysterese, Signal und Ausgang 0:59:0 Diskussion Vref, VDD, VSS Verschiebung der Kurve 1:3:50 3 Bit Flash Analog Digital Konverter (ADC) 1:10:30 Rechnung und Zeichnung Ðbertragungsfunktion 1:14:30 Delta, LSB abs 1:17:40 Fehler 1/2 LSB |

R¸ckblick und Ðbersicht

- Differenzverst‰rker

- Gleichtakt und Gegentakt

- Funktionsweise

- CMRR und PSRR

Heute

- Der Operationsverst‰rker

- 3 bit Flash ADC

Unit 3, 1-20

Der Operationsverst‰rker

- Why Operational Amplifiers? U3.1

- OpAmp Symbols U3.2

- First commercial OpAmp U3.3

- Packaging U3.4

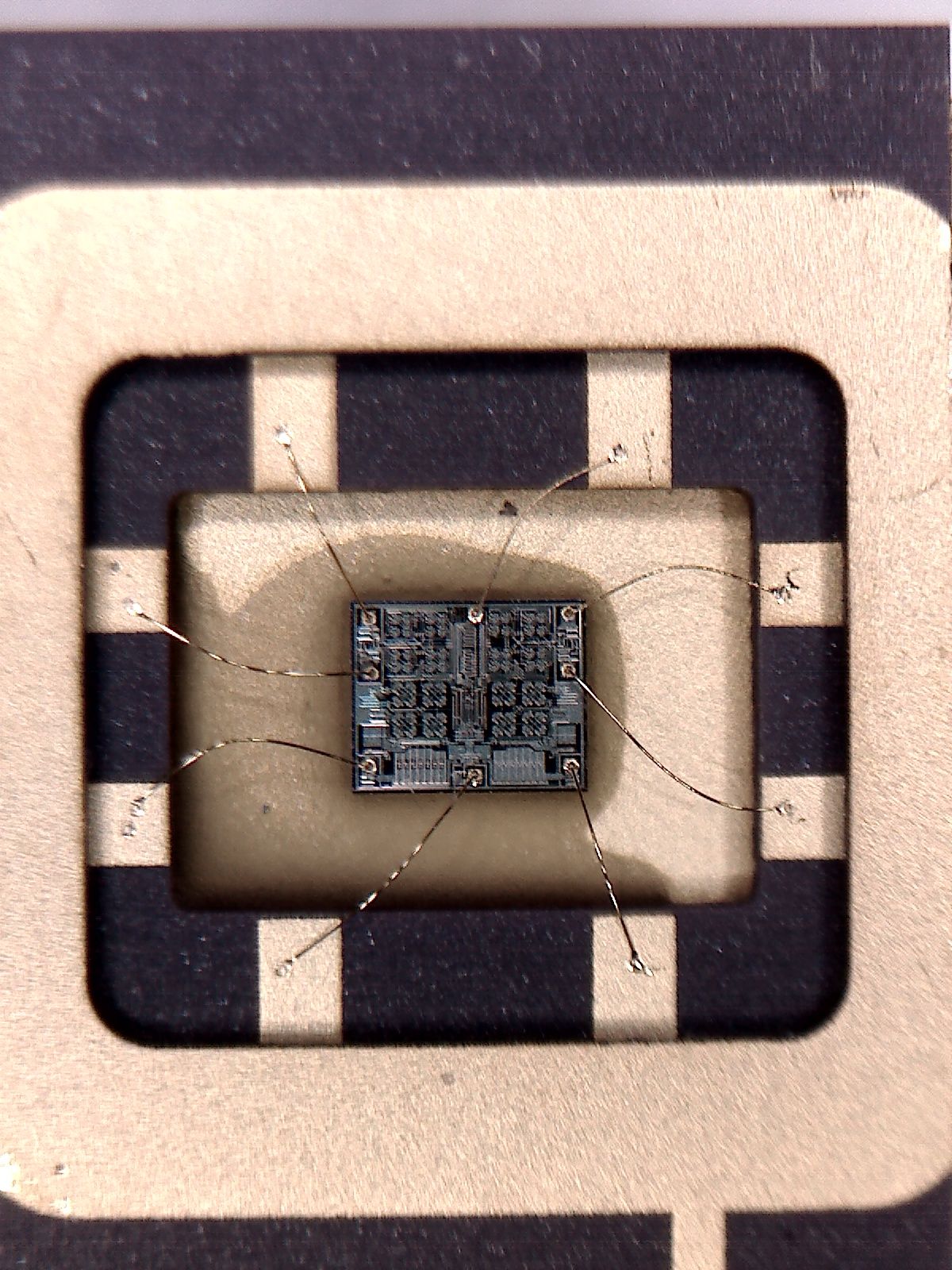

CMOS Operationsverst‰rker TLC272 gebondeter Chip

|

|

Man kann integrierte Bauelemente auch als Wafer oder Chips bekommen.

Das Bild zeigt den Chip TLC272 dessen Bondpads mit feinen Golddr‰hten (25 µm Dicke) mit dem Geh‰use verbunden sind.

Pin 1 ist bei dem Bild rechts oben, damit die Eing‰nge links und die Ausg‰nge rechts sind.

Die Chips wurden hier an der Hochschule Kempten im Labor Mikrosystemtechnik gebondet.

Es befinden sich 2 Operationsverst‰ker auf dem Chip. Einer oben und einer unten.

Die Spannungsversorgungspads befinden sich in der Mitte rechts (VDD) und links (GND).

Links oben und unten befinden sich jeweils die beiden Eing‰nge.

Links In+ rechts In-.

Rechts oben und unten befinden sich die Ausg‰nge.

Der Chip ist 1.524 mm x 1.8542 mm (60 mil x 73 mil) gross.

Weitere Informationen findet man auch im Datenblatt.

Das Bild zeigt den Chip TLC272 dessen Bondpads mit feinen Golddr‰hten (25 µm Dicke) mit dem Geh‰use verbunden sind.

Pin 1 ist bei dem Bild rechts oben, damit die Eing‰nge links und die Ausg‰nge rechts sind.

Die Chips wurden hier an der Hochschule Kempten im Labor Mikrosystemtechnik gebondet.

Es befinden sich 2 Operationsverst‰ker auf dem Chip. Einer oben und einer unten.

Die Spannungsversorgungspads befinden sich in der Mitte rechts (VDD) und links (GND).

Links oben und unten befinden sich jeweils die beiden Eing‰nge.

Links In+ rechts In-.

Rechts oben und unten befinden sich die Ausg‰nge.

Der Chip ist 1.524 mm x 1.8542 mm (60 mil x 73 mil) gross.

Weitere Informationen findet man auch im Datenblatt.

Der Operationsverst‰rker

- Static parameters U3.5, U3.6

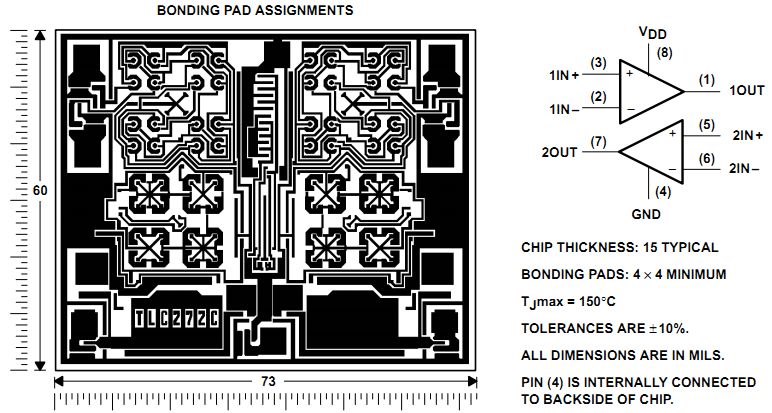

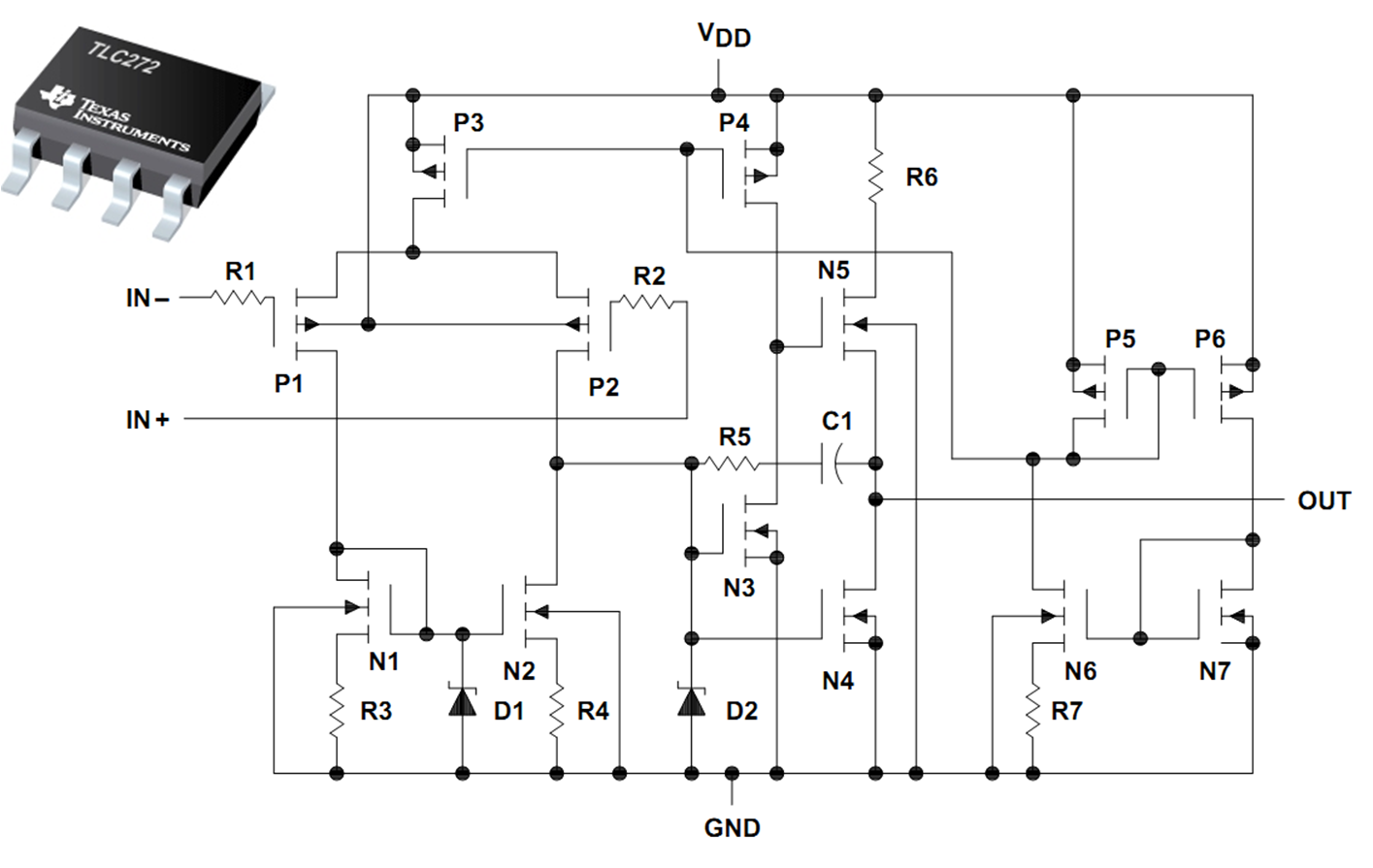

CMOS Operationsverst‰rker TLC272

Quelle: Texas Instruments Datenblatt tlc272a.pdf

Referenzstromquelle rechts: P5, P6, N6, N7, R7

Differenzverst‰rker: P1, P2, P3, N1, N2

Zenerdiode f¸r den Startup

2.te Verst‰rkerstufe: Sourceschaltung: N3, P4

Ausgangsstufe: N4, N5

Frequenzgangkompensation: R5, C1

Differenzverst‰rker: P1, P2, P3, N1, N2

Zenerdiode f¸r den Startup

2.te Verst‰rkerstufe: Sourceschaltung: N3, P4

Ausgangsstufe: N4, N5

Frequenzgangkompensation: R5, C1

Der Operationsverst‰rker

27.04.2021

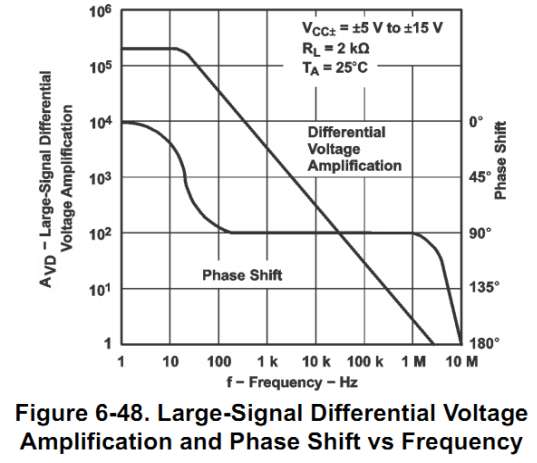

- Bode Diagramm TL071

- Komparator, Hysterese

- Flash ADC

Der Operationsverst‰rker

a) Determine the values for AVD(f3dB), AVD(ft) and phase margin φm

b) Calculate the signal bandwidth for a closed loop amplifier with a gain of 200.

Der Operationsverst‰rker

Frequency response U3.8

Datenblatt TL071

- Datenblatt: 6.18. Avd = 200000

- Datenblatt: 6.17. GBW = 5.25 MHz

Diskussion 3 dB Eckfrequenz

\( \underline{A_{VD}} (j\omega) = \frac{A_{VD}(DC)}{1+ j \frac{f}{f_{3dB}}}\)

Phase margin

\( \phi_m = 180∞ - |\phi (f_t) | \gt 45∞, 60∞ \)

TL071 Simulation

Der Operationsverst‰rker

- Comparator U3.9

- Hysteresis U3.10

- Simulation

Schmitt Trigger

Ein Schwellwertschalter mit Hysterese

Achtung: Der Anschluþ der Eingangsspannung an den Operationsverst‰rker erfolgt am

positiven Eingang des Operationsverst‰rkers.

\( U_H = U_{eE} - U_{eA} \) Berechnung der Umschaltschwellen

Erster Fall: \( U_a = U_{amin} \); \( U_e < U_{eE} \)

F¸r den Umschaltpunkt muss gelten: \( I(U_x = 0) = \frac{U_{eE}}{R1} = - \frac{U_{amin}}{R_2} \) \( U_{eE} = - U_{amin} \frac{R_1}{R_2} \) Symmetrie: \( U_{eA} = - U_{amax} \frac{R_1}{R_2} \) Hysterese: \( U_H = U_{eE} - U_{eA} = \left( U_{amax} - U_{amin} \right) \frac{R_1}{R_2} \) |

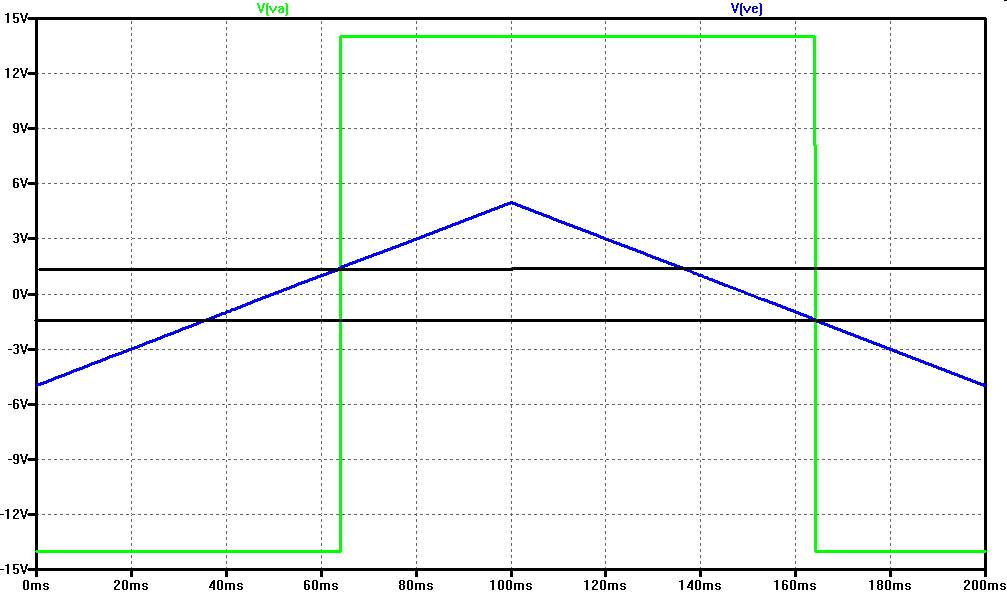

Reale Signale haben immer Stˆrungen.

Kleine Wechselspannungen sind dem idealen Signal ¸berlagert.

Wenn sich das Eingangssignal ‰ndert kann es an der Umschaltschwelle durch die Stˆrsignale zum mehrmaligen Umschalten oder Prellen f¸hren.

Um das zu verhindern kann man einen Tiefpass oder eine Hysterese einsetzen.

Kleine Wechselspannungen sind dem idealen Signal ¸berlagert.

Wenn sich das Eingangssignal ‰ndert kann es an der Umschaltschwelle durch die Stˆrsignale zum mehrmaligen Umschalten oder Prellen f¸hren.

Um das zu verhindern kann man einen Tiefpass oder eine Hysterese einsetzen.

Schmitt Trigger in LTSPICE

|

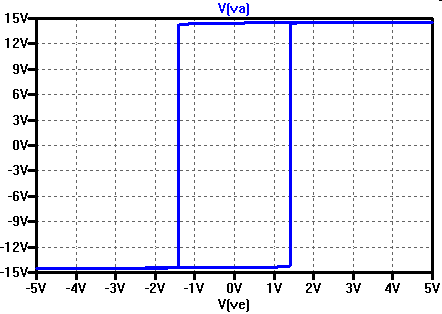

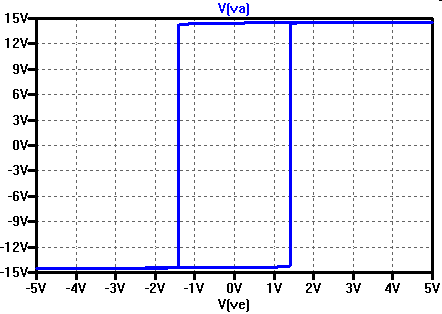

Realer Operationsverst‰rker \( U_{amax}, U_{amin} \) LTSPICE: DC Simulation zeigt keine Hysterese Transiente Simulation LTSPICE Mausklick auf x - Achse: V(ve) Hysterese: \( U_H = \left( U_{amax} - U_{amin} \right) \frac{R_1}{R_2} \) \( U_H = \left( 14 V - (- 14 V) \right) \frac{1 k\Omega}{10k\Omega} = 2.8 V \) Oszilloskopmessung: x-y Betrieb |

|

|

Flash ADC U3.16

Master Electrical Engineering: Interface Electronics

OperationResolution BSpeedPowerRelative Schrittweite: Least significant bit Relative \( LSB_{rel} = \frac{1}{2^B} \) Absolut: \( LSB_{abs} = \frac{V_{ref}}{2^B}\) B: Anzahl Bits Vref: Referenzspannung Vorsicht beim Runden vom LSB. | cmosedu_models.txt |

The Flash ADC generates a thermometer code.

For each level one comparator is needed. High count of comparators, high input capacitance.

High resolution requires low comparator offset and high gain to generate a full level digital signal.

The offset of a comparator depends on the size of the CMOS input transistors:

Voffset ∝ \( \frac{1}{\sqrt{W \cdot L}} \)

Lower noise means higher area and higher input capacitance.

If the requirement for comparator offset is not met or noise is present sparkle codes can happen.

The thermometer code is corrupted having more than one transition from 0 to 1.

The code for the first '01' transition is 'OR'ed with the code of the second '01' transition.

Additional digital circuit can be required.

Comparators can feedback noise to the reference voltage ladder. Capacitive coupling between comparator output and intput.

| Thermometer code | Binary Code | ||||||||

| T6 | T5 | T4 | T3 | T2 | T1 | T0 | B2 | B1 | B0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 |

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

For each level one comparator is needed. High count of comparators, high input capacitance.

High resolution requires low comparator offset and high gain to generate a full level digital signal.

| Number of Bits | Maximum Offset | Gain |

| 4 | 0.0625 · Vref | 16 |

| 8 | 0.004 · Vref | 256 |

| 10 | 0.001 · Vref | 1024 |

| 12 | 0.0025 · Vref | 4048 |

The offset of a comparator depends on the size of the CMOS input transistors:

Voffset ∝ \( \frac{1}{\sqrt{W \cdot L}} \)

Lower noise means higher area and higher input capacitance.

If the requirement for comparator offset is not met or noise is present sparkle codes can happen.

The thermometer code is corrupted having more than one transition from 0 to 1.

| Correct code: | 000000011111111 | Encoded binary code | 1000 |

| Sparkle code: | 000000010111111 | Encoded binary code | 1110 |

Additional digital circuit can be required.

Comparators can feedback noise to the reference voltage ladder. Capacitive coupling between comparator output and intput.

Analog-Digital-Wandler (ADC)

Master Electrical Engineering: Interface ElectronicsB: Anzahl Bits

Vref: Referenzspannung

Beispiel: B = 12, Vref = 4 V

\( LSB_{rel} = \frac{1}{2^{12}} = \frac{1}{4096} = 0.00024414 = 244 ppm \)

\( LSB_{abs} = \frac{4 V}{2^{12}} = \frac{4 V}{4096} = 976.56 uV \)

Achtung bei der Rundung vom LSB:

4095 * 976.56 uV = 3.999 V

4095 * 976 uV = 3.996 V

3 mV Unterschied in der Rechnung > 0.976 mV

Uniform sampled time signals: Aliasing

Samples spaced with sampling period \( T_S = \frac{1}{f_S} \).Multiple continous timesignals can generate the same discrete time signal.

fsample = 4 Hz, Tsample = 0.25 s,

fsignal = 2.4 Hz, Tsignal = 0.417 ms,

falias = fsample - fsignal = 1.6 Hz, Talias = 0.625 ms,

Red: sample points; blue and green 2 possible signals

The frequencies fsignal and n fsample ± fsignal, n integer, are indistinguishable in the discrete time domain.

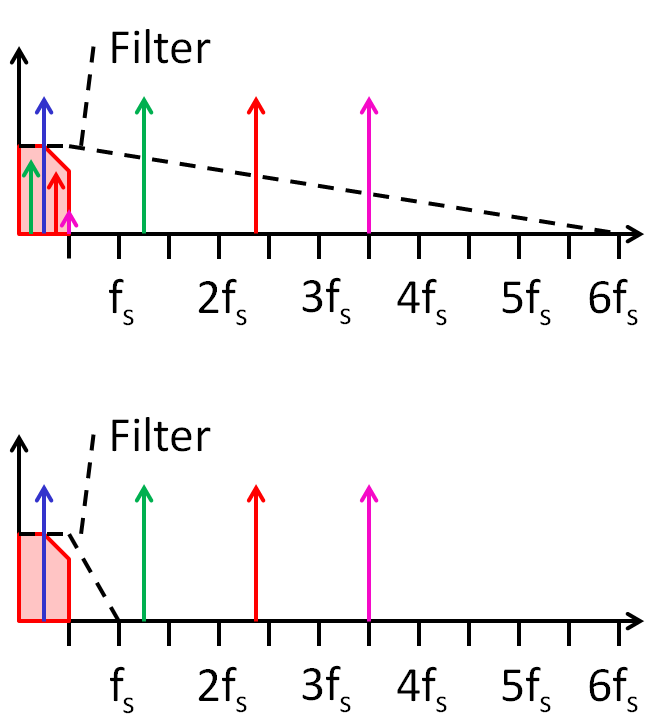

Frequency Domain: Aliasing

|

The frequencies fx and nfs ± fx, n integer, are indistinguishable in the discrete time domain Nyquist zones 1st: 0..fs/2; 2nd: fs/2..fs; 3rd: fs..3/2fs; 4th: 3/2 fs..2fs Anti aliasing filter |

|

Having a sampling frequency fS gives a frequency spectrum from 0 to fS/2.

Only this range of interested is highlighted in the figures.

The number of sampled points NFFT gives the minimum frequency and the frequency resolution:

fmin = fstep = fS * 2 / NFFT

The figure shows a linear scaling of the frequency x-axis.

Most of the time a logarithmic frequency scaling is used.

Only this range of interested is highlighted in the figures.

The number of sampled points NFFT gives the minimum frequency and the frequency resolution:

fmin = fstep = fS * 2 / NFFT

The figure shows a linear scaling of the frequency x-axis.

Most of the time a logarithmic frequency scaling is used.

Zusammenfassung und n‰chste Vorlesung

- Operationsverst‰rker

- Flash ADC

N‰chstes Mal