Elektronik 306 MOSFETProf. Dr. J÷rg Vollrath05 Diodenschaltungen |

|

|

Lõnge: 00:42:10 |

0:0:0 Bis 9.11.20 ▄bung 1 Aufgabe 1,2 ▄bung 2 Aufgabe 3, WS2011 Aufgabe 1; WS2012 Aufgabe 2 0:2:40 Was haben Sie im Praktikum gelernt? 0:4:4 Reflektieren was sie gelernt haben 0:6:50 Abbildung x U Diode, y I Diodenstrom 0:8:18 Ergebnissicherung 0:10:12 Messbereich Oszilloskop Formatf³llende Darstellung 0:12:40 2 Perioden 0:14:25 MOSFET Was nehmen Sie aus der Folie mit? 0:14:57 MOSFET Anschl³sse G, S, D, B 0:17:59 Schaltsymbole 0:19:43 Funktionsprinzip 0:20:59 NFET Kennlinienfeld 0:22:21 Ausgnagskennlinie IDS(UDS) ▄bertragungskennlinie I(UGS) 0:24:54 Negative Bulkspannung 0:26:54 Drain und Source werden durch angelegte Spannungen definiert 0:28:29 Typen des Feldeffekttransistors 0:31:33 Kennlinien 0:33:10 Vereinfachtes Schaltsymbol 0:34:54 Schalter und Verstõrker 0:35:54 Messaufbau f³r die Kennlinie V4 0:38:48 Gleichung des NFET 0:42:54 3 Parameter Uth, β , λ 0:53:8 Wichtige Kenngr÷▀en, W und L 0:55:39 Schwellspannung 0:57:31 Beispiel NMOS Arbeitsbereich und Strom 1:0:49 Arbeitsbereich Nicht im Sperrbereich 1:2:2 Gleichung f³r den Strom 1:2:54 1 + λ UDS 1:4:36 Datenblatt Vt, IDS, GOS 1:7:16 Betriebsbereich 1:10:4 PFET Absolutwerte |

Elektronik 3 alt Vorlesung und Video Differenzverstõrker

R³ckblick und Heute

Diode- Spannungsverdopplung

- Z-Diode: Spannungsquelle

MOSFET

- Physikalische Struktur

- Stromspiegel

- Differenzverstõrker

Elektronische Schaltungstechnik, Reinhold: Kapitel 6, S. 102-124

Microelectronic, Jaeger: Chapter 4, page: 145-216

NFET Kennlinienfeld

Querschnitt eines MOSFET

|

Ausgangskennlinie ▄bertragungskennlinie |

Im Querschnitt des n-Kanal MOSFETs (NFET, NMOS) sieht man in hellgr³n die

stark n-dotierten (n+) Gebiete von Source (S) und Drain (D) in einem schwach

p-dotiertem Silizium Wafer (Bulk Kontakt). Diese werden dar³ber mit

Aluminium-Metallkontakten nach oben verbunden (dunkelblau).

Zwischen Source und Drain befindet sich das isolierte (grau) Gate (orange, Polysilizium).

Das Isolationsmaterial ist meist SiO2 (Siliziumoxid, Glas) oder Si3N4 (Siliziumnitrid).

Die Animation zeigt, wie sich die Raumladungszone (Source-Bulk, Drain-Bulk, hell orange) und die Ladungstrõgerkonzentration (hellgr³n) sich bei angelegter Spannung õndert. Dabei wird der gewõhlte Arbeitspunkt im Kennlinienfeld (oben Ausgangskennlinie, unten ▄bertragungskennlinie) markiert.

Das Isolationsmaterial ist meist SiO2 (Siliziumoxid, Glas) oder Si3N4 (Siliziumnitrid).

Die Animation zeigt, wie sich die Raumladungszone (Source-Bulk, Drain-Bulk, hell orange) und die Ladungstrõgerkonzentration (hellgr³n) sich bei angelegter Spannung õndert. Dabei wird der gewõhlte Arbeitspunkt im Kennlinienfeld (oben Ausgangskennlinie, unten ▄bertragungskennlinie) markiert.

Wie sieht der Querschnitt und das Kennlinienfeld eines PFETS aus?

Die Gleichung des n-Kanal MOSFETs

|

\( I_{DS} = \cases{ 0 & \text{ Sperrbereich } \cr \text{ f³r } U_{GS} \leq U_{th} \cr \cr

\beta \left( U_{GS}-U_{th} \right)^2 \left( 1+\lambda U_{DS} \right) & \text{ Sõttigung}

\cr \text{ f³r } 0 \leq U_{GS} - U_{th} \lt U_{DS} \cr \cr

\beta \left( 2 \left( U_{GS}-U_{th} \right) U_{DS} - U_{DS}^2 \right) & \text{ Triodenbereich}

\cr \text{ f³r } 0\leq U_{GS} - U_{th} \geq U_{DS}

}

\) \( \beta = \frac{\mu_n \epsilon_{ox}}{2d_{ox}} \frac{W}{L} = \frac{1}{2} \mu_n C_{ox}^{'} \frac{W}{L} = \frac{1}{2} K_{n}^{'} \frac{W}{L} = \frac{1}{2} K_{n} = \frac{1}{2} KP \) |

- Uth : Schwellspannung [V]

- β : Steilheitsparameter [A V-2]

- λ : Kanallõngenmodulation [V-1]

Stromspiegel

Einsatz:

Es soll das Stromverhõltnis I2 zu I1 berechnet werden.

Die Transistoren befinden sich in der Sõttigung. Es gilt:

\( I_{DS} = \beta \left( U_{GS} - U_{Th} \right)^{2} \left( 1 + \lambda U_{DS} \right) \) \( U_{GS1} = U_{GS2} \) \( \frac{I_2}{I_1} = \frac{\beta_2}{\beta_1} \frac{ \left( 1 + \lambda U_{DS2} \right) }{\left( 1 + \lambda U_{DS1} \right)} = \frac{W_2 \cdot L_1 }{W_{1} \cdot L_{2}} \frac{ \left( 1 + \lambda U_{DS2} \right) }{\left( 1 + \lambda U_{DS1} \right)} \) mit \( L_{1} = L_{2} \) \( \frac{I_2}{I_1} \approx \frac{W_{2} }{W_{1}}\) \( \lambda \) ist sehr klein. Man kann mit einem Stromspiegel durch die Wahl eines geeigneten Weitenverhõltnisses oder der Anzahl der Transistoren einen Strom verstõrken. |

Ein Strom I1 durch M1 stellt eine Gate Source Spannung der Transistoren ein

und bewirkt einen Stromfluss I2 = I1 im Transistor M2.

Der Strom durch M2 bleibt bei Variation der Spannung VDD nahezu konstant (Stromquelle).

Der Strom durch M2 bleibt bei Variation der Spannung VDD nahezu konstant (Stromquelle).

Ausgangswiderstand des Stromspiegels

|

Bei einer realen Stromquelle interessiert der Innenwiderstand der Quelle. Ausgangswiderstand von M2

\( R_{out} = r_{D} \)

F³r die Sõttigung ist der Ausgangsleitwert definiert als: \( g_d = \frac{d I_{DS}}{d U_{DS}} = \frac{\beta \left( U_{GS} - U_{Th} \right)^{2} \left( 1 + \lambda U_{DS} \right)}{d U_{DS}} \) \( g_d = \frac{d I_{DS}}{d U_{DS}} = \beta \left( U_{GS} - U_{Th} \right)^{2} \lambda \approx I_{DS} \lambda \) Der Ausgangswiderstand oder Innenwiderstand einer Stromquelle sollte m÷glichst gro▀ sein MOSFET: \( R_{out} = \frac{1}{I_{DS} \lambda} \) Bipolar: \( R_{out} = \frac{U_{EA}}{I_{C}} \) \( \frac{1}{ \lambda} \) entspricht \( U_{EA} \) |

Beispiel MOS Stromspiegel

|

Berechnen Sie den Strom \( I_2 \) und den Ausgangswiderstand von folgender Schaltung. \( I_{1} = 150 \mu A, V_{DD} = 10 V,\) \( V_{Th} = 1 V, K_{n} = 250 \mu A V^{-2},\) \( \lambda = 0.0133 V^{-1} \)

\( I_{DS} = \frac{K_N}{2} \left( U_{GS} - U_{Th} \right)^{2} \left( 1 + \lambda U_{DS} \right) \)

Zur Berechnung des Arbeitspunktes wird der Term \( 1 + \lambda U_{DS} \) vernachlõssigt. \( U_{GS} = U_{Th} + \sqrt{ \frac{2 \cdot I_{1}}{K_N}} = 1V +\sqrt{\frac{2 \cdot 150 \mu A}{250 \mu A V^{-2}}} = 2.1 V \) \( I_2 \) unter Ber³cksichtigung von \( \lambda \) \( I_{2} = 150 \mu A \frac{1 + \lambda V_{DD}}{1 + \lambda U_{GS}} = 150 \mu A \frac{1 + 0.0133 \cdot 10 }{1 + 0.0133 \cdot 2.1} = 150 \mu A \frac{1.13}{1.028} = 165 \mu A \) Es gibt eine kleine Stromerh÷hung (10%) durch die Spannung \( U_{DS} \) von 10V. Ausgangswiderstand: \( R_{out} = \frac{1}{I_{DS} \cdot \lambda } = \frac{1}{165 \mu A \cdot 0.0133 V^{-1}} = 456 k \Omega \) Wollte man den Transistor durch einen ohmschen Widerstand ersetzen, ben÷tigt man folgende Spanung: \( U = I_{2} \cdot R_{out} = 165 \mu A \cdot 456 k \Omega = \frac{1}{\lambda} = 75V \) |

Nachdenken ³ber die L÷sung

- Wann kann man \( \left( 1 + \lambda U_{DS} \right) \) vernachlõssigen?

- Nicht ideales Spiegelverhõltnis

- \( U_{DS} \) ist unterschiedlich

- Ausgangswiderstand

- õquivalente Spannung \( \frac{1}{\lambda } \)

- Typischer Wert \( > 100k \Omega \)

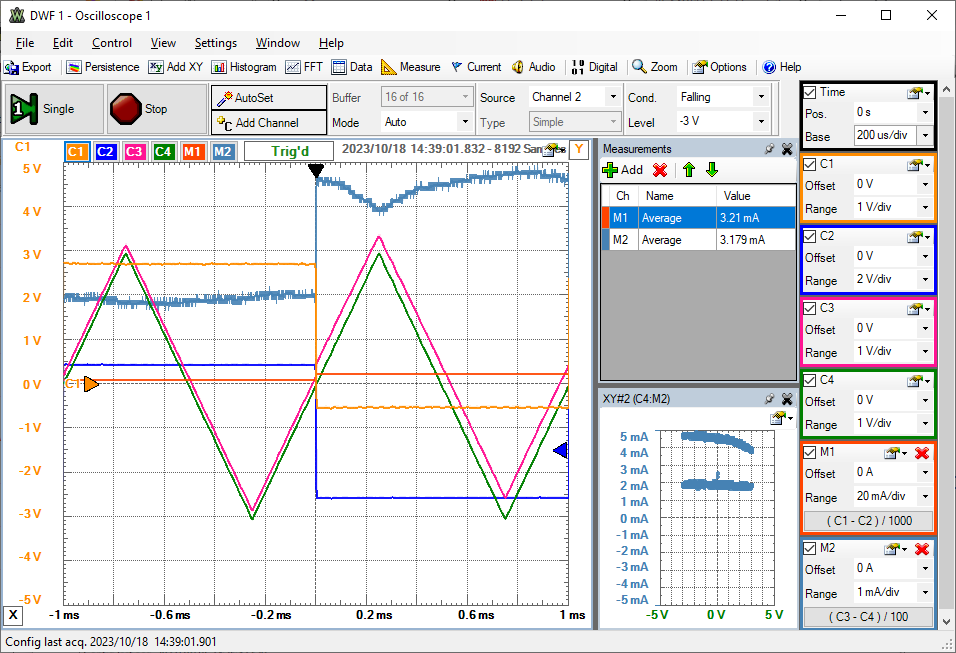

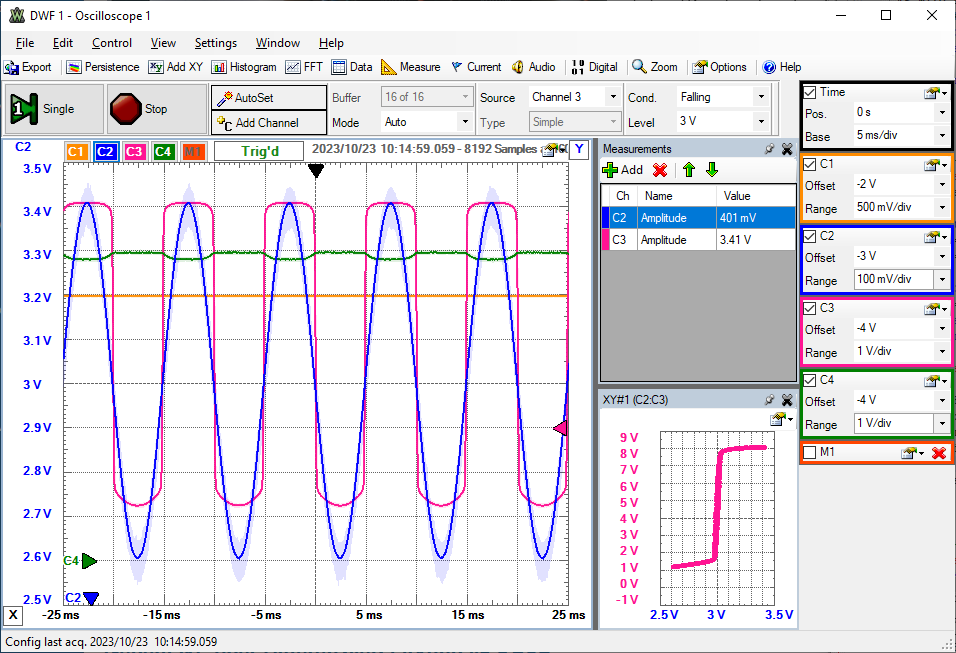

Simulation und Demonstration

|

|

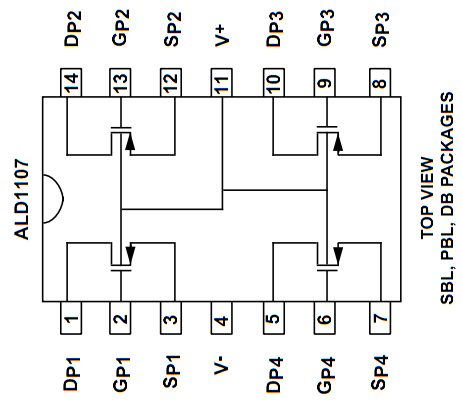

Ein PFET Array ALD1107 wird mit R1 = 1 kOhm und R2 = 100 Ohm verschaltet und

mit dem Electronic Explorer betrieben.

Die Versorgungsspannung VP+ = 8V liegt an. Bei grosser Variation der Ausgangsspannung VAWG2 verõndert sich der Ausgangsstrom \( I_{R2} = \frac{OSC3 - OSC4}{100} \) wegen des hohen Ausgangswiderstandes kaum.

Man bestimmt mit AWG1 = 1 V, -5 V (Rechtecksignal, f = 500 Hz, Amplitude = 3 V, Offset = -2 V) den Strom I1 (M1) = 2 mA, 4.5 mA und erkennt, dass bei Variation von AWG2 (Triangle, f = 1 kHz, Amplitude = 4 V, Offset = 0 V) von -3 V bis zu +3 V sich der Strom nur wenig õndert.

Die typische Stromquellen Kennlinie ist in der xy Darstellung zu sehen.

Die Versorgungsspannung VP+ = 8V liegt an. Bei grosser Variation der Ausgangsspannung VAWG2 verõndert sich der Ausgangsstrom \( I_{R2} = \frac{OSC3 - OSC4}{100} \) wegen des hohen Ausgangswiderstandes kaum.

Man bestimmt mit AWG1 = 1 V, -5 V (Rechtecksignal, f = 500 Hz, Amplitude = 3 V, Offset = -2 V) den Strom I1 (M1) = 2 mA, 4.5 mA und erkennt, dass bei Variation von AWG2 (Triangle, f = 1 kHz, Amplitude = 4 V, Offset = 0 V) von -3 V bis zu +3 V sich der Strom nur wenig õndert.

Die typische Stromquellen Kennlinie ist in der xy Darstellung zu sehen.

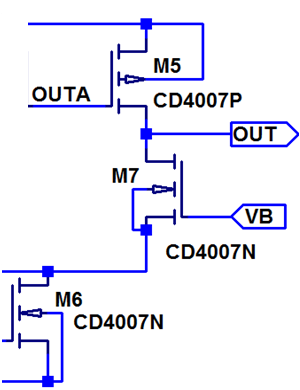

Differenzverstõrker: Schaltbild

|

Der zweite Eingang des Differenzverstõrkers erlaubt die Messung von Differenzen.

Schwankungen der Versorgungsspannung zeigen sich am Ausgang kaum.

Schwankungen der Versorgungsspannung zeigen sich am Ausgang kaum.

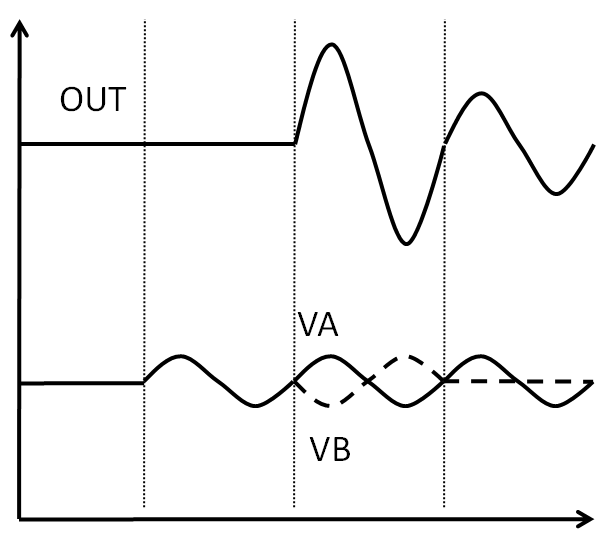

Gegentakt, Differenzverstõrker, Signale

|

|

- Eingangssignal:

| Gleichtakt: \( u_{gl} = \frac{u_A + u_B }{2} \) | Gegentakt, Differenz: \( u_D = u_A - u_B \) |

Direkte Einkopplung, keine Koppelkapazitõt, Gleichspannungsverstõrkung

Bei 2 Eingõngen kann man das Eingangssignal in einen Gleichtaktsignal und ein Gegentaktsignal zerlegen.

Idealerweise hat der Verstõrker eine gro▀e Gegentaktverstõrkung und keine Gleichtaktverstõrkung.

Idealerweise wirkt sich eine Versorgungsspannungsõnderung nicht auf das Ausgangssignal aus.

Im Allgemeinen spricht man von single ended und differentiellen (differential) Signalen.

Differentielle Signale sind nicht so st÷ranfõllig, da sich St÷rungen auf beide Signalleitungen auswirken und nachfolgende Differenzverstõrker mit geringer Gleichtaktverstõrkung diese St÷rungen unterdr³cken.

Bei 2 Eingõngen kann man das Eingangssignal in einen Gleichtaktsignal und ein Gegentaktsignal zerlegen.

Idealerweise hat der Verstõrker eine gro▀e Gegentaktverstõrkung und keine Gleichtaktverstõrkung.

Idealerweise wirkt sich eine Versorgungsspannungsõnderung nicht auf das Ausgangssignal aus.

Im Allgemeinen spricht man von single ended und differentiellen (differential) Signalen.

Differentielle Signale sind nicht so st÷ranfõllig, da sich St÷rungen auf beide Signalleitungen auswirken und nachfolgende Differenzverstõrker mit geringer Gleichtaktverstõrkung diese St÷rungen unterdr³cken.

Funktionsweise des Differenzverstõrkers

|

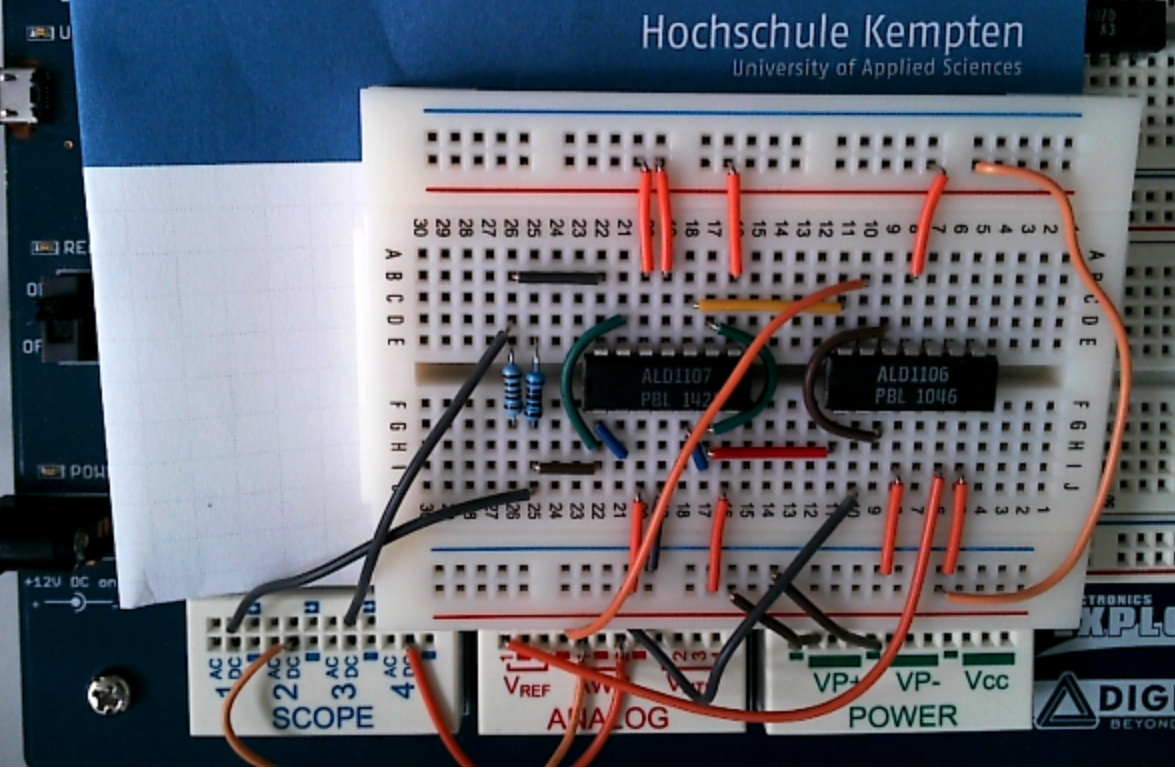

Differenzverstõrker Simulation und Demonstration

|

|

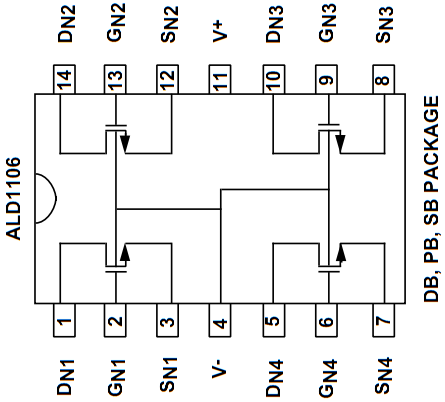

Ein PFET Array ALD1107 und NFET Array ALD1106 wird als Differenzverstõrker verschaltet und

mit dem Electronic Explorer betrieben.

Die Versorgungsspannung VP+ = 8V und die Referenzspannung Vref1 = 1.4 V liegt an. Bei einer Spannung VAWG1 = 3 V (Offset, 0V Amplitude) wird die Spannungsquelle VAWG2 mit einem Sinussignal (Offset = 3 V, Amplitude = 400 mV) betrieben.

Am Oszilloskop sieht man in blau (C2) die Eingangsspannung VAWG2 mit 400 mV Amplitude, die Spannung OUTA (gr³n, C4) und die verstõrkte Spannung OUT (pink, C3).

In einer x-y Darstellung von C3 ³ber C1 kann man die ▄bertragungskennlinie sehen und eine Verstõrkung von vdiff = dC3/dC2 = 4V / 10mV = 400 ablesen.

Folgende weitere Untersuchungen sind interessant:

1) Variation von Vref1: Wie õndert sich der Strom und die Spannungsverstõrkung?

Bei kleinerem Vref nimmt die Verstõrkung zu, aber man sieht auch eine Hysterese, bedingt durch eine Phasenverschiebung bei kleinerer Eckfrequenz.

2) Gleichtaktverstõrkung: Beide Eingõnge werden mit AWG2 betrieben.

vgl = d C3 / d C2 = 35 mV / 400 mV = 0.09

Berechnung der Common mode rejection rate.

CMRR = 20 log (vdiff / vgl ) = 20 log (400 / 0.09 ) = 72 dB

3) Power supply rejection rate: PSRR.

Signal an der Betriebsspannung: d VP+ (C1) = 100 mV; d Vout = 100 mV;

vb = d VP+ / dVout = 1

PSRR = 20 log(vdiff/ vb) = 20 log(400 / 1) = 52 dB

4) Frequenzgang

Wie õndert sich die Verstõrkung bei verschiedenen Frequenzen?

Die Versorgungsspannung VP+ = 8V und die Referenzspannung Vref1 = 1.4 V liegt an. Bei einer Spannung VAWG1 = 3 V (Offset, 0V Amplitude) wird die Spannungsquelle VAWG2 mit einem Sinussignal (Offset = 3 V, Amplitude = 400 mV) betrieben.

Am Oszilloskop sieht man in blau (C2) die Eingangsspannung VAWG2 mit 400 mV Amplitude, die Spannung OUTA (gr³n, C4) und die verstõrkte Spannung OUT (pink, C3).

In einer x-y Darstellung von C3 ³ber C1 kann man die ▄bertragungskennlinie sehen und eine Verstõrkung von vdiff = dC3/dC2 = 4V / 10mV = 400 ablesen.

Folgende weitere Untersuchungen sind interessant:

1) Variation von Vref1: Wie õndert sich der Strom und die Spannungsverstõrkung?

Bei kleinerem Vref nimmt die Verstõrkung zu, aber man sieht auch eine Hysterese, bedingt durch eine Phasenverschiebung bei kleinerer Eckfrequenz.

2) Gleichtaktverstõrkung: Beide Eingõnge werden mit AWG2 betrieben.

vgl = d C3 / d C2 = 35 mV / 400 mV = 0.09

Berechnung der Common mode rejection rate.

CMRR = 20 log (vdiff / vgl ) = 20 log (400 / 0.09 ) = 72 dB

3) Power supply rejection rate: PSRR.

Signal an der Betriebsspannung: d VP+ (C1) = 100 mV; d Vout = 100 mV;

vb = d VP+ / dVout = 1

PSRR = 20 log(vdiff/ vb) = 20 log(400 / 1) = 52 dB

4) Frequenzgang

Wie õndert sich die Verstõrkung bei verschiedenen Frequenzen?

Gegentakt- oder Differenzverstõrkung vD KESB

|

Das Bild zeigt das Kleinsignalersatzschaltbild in LTSPICE. Berechnung der Differenzverstõrkung: \( u_{out} = - \left( i_5 + i_7 \right) \cdot \left( r_{d5} || r_{d7} \right) \) \( u_{out} = - \left( u_{outa} \cdot g_{m5} + u_{b} \cdot g_{m7} \right) \cdot \left( r_{d5} || r_{d7} \right) \) \( u_{out} = - \left( - u_{a} \cdot g_{m2} \left( r_{D2} || r_{m4} \right) \cdot g_{m5} + u_{b} \cdot g_{m7} \right) \cdot \left( r_{d5} || r_{d7} \right) \) Nõherung \( r_{m4} \ll r_{D2} \) \( u_{out} \approx - \left( - u_{a} \cdot g_{m2} \frac{g_{m5}}{g_{m4}} + u_{b} \cdot g_{m7} \right) \cdot \left( r_{d5} || r_{d7} \right) \) Mit \( g_{m5} = g_{m4} \) und \( g_{m7} = g_{m2} \) und \( r_{d5} = r_{d7} \) \( u_{out} \approx \left( u_{a} - u_{b} \right) \frac{ r_{d7} \cdot g_{m7} }{2} \) |

Bei der Differenzverstõrkung ist Δ UA = - Δ UB und

Δ IA = - Δ IB. Damit bleibt der Knoten Vlow

auf konstanten Potential und M6 kann im Kleinsignalersatzschaltbild wegfallen.

Gleichtaktverstõrkung: uA = uB

vgl ist hier wegen der Nõherung \( r_{m4} \ll r_{D2} \) gleich 0.

Ber³cksichtigt man die Nõherung, ergibt sich:

\( u_{out} = - \left( 1 - \left( r_{D2} || r_{m4} \right) \cdot g_{m5} \right) u_{a} \cdot g_{m7} \cdot \left( r_{d5} || r_{d7} \right) \)

\( v_{gl} = - \left( 1 - \frac{r_{D2} || r_{m4}}{r_{m4}}\right) \cdot 2 \cdot v_{D} \)

Bei den bisherigen Beispielen war rD ≈ 100 · rm.

\( v_{gl} = \left( 1 - \frac{1}{1 + \frac{r_{m4}}{ r_{D2}}} \right) \cdot 2 \cdot v_{D} = 0.02 \cdot v_{D} \)

Gleichtaktverstõrkung: uA = uB

vgl ist hier wegen der Nõherung \( r_{m4} \ll r_{D2} \) gleich 0.

Ber³cksichtigt man die Nõherung, ergibt sich:

\( u_{out} = - \left( 1 - \left( r_{D2} || r_{m4} \right) \cdot g_{m5} \right) u_{a} \cdot g_{m7} \cdot \left( r_{d5} || r_{d7} \right) \)

\( v_{gl} = - \left( 1 - \frac{r_{D2} || r_{m4}}{r_{m4}}\right) \cdot 2 \cdot v_{D} \)

Bei den bisherigen Beispielen war rD ≈ 100 · rm.

\( v_{gl} = \left( 1 - \frac{1}{1 + \frac{r_{m4}}{ r_{D2}}} \right) \cdot 2 \cdot v_{D} = 0.02 \cdot v_{D} \)

Gleichtaktverstõrkung: vGl mit M6

\( I = - g_m \cdot v_{GS7} \frac{r_{D7}||\left( r_{D5} + 2 \cdot r_{D6}\right)}{r_{D5} + 2 \cdot r_{D6}}\) \( v_{Gl} = - \frac{1}{\frac{r_{D5} + 2 \cdot r_{D6}}{g_m \cdot \left( r_{D5} r_{D7}||\left( r_{D5} + 2 \cdot r_{D6}\right) \right)} + 2 \frac{r_{D6}}{r_{D5}}} \) \( v_{Gl} = - \frac{1}{\frac{r_{D5} + 2 \cdot r_{D6} + r_{D7}}{g_m \cdot r_{D5} \cdot r_{D7} } + 2 \frac{r_{D6}}{r_{D5}}} \) \( v_{Gl} = - \frac{r_{D5}}{2 \cdot r_{D6}} \frac{1}{1 + \frac{r_{D5} + 2 \cdot r_{D6} + r_{D7}}{2 \cdot g_m \cdot r_{D6} \cdot r_{D7} }} \approx - \frac{r_{D5}}{2 \cdot r_{D6}} \)

St÷rsignale auf beiden Eingõngen A und B erscheinen nicht am Ausgang und werden unterdr³ckt. |

|

Gleichtaktunterdr³ckung

- Common mode rejection rate (CMRR)

- Angabe in Dezibel (dB)

\( G = \frac{v_{D}}{v_{Gl}} = \frac{g_m \left( r_{D2} || r_{D4}\right)} {\frac{r_{D4}}{2 \cdot r_{D6}}} = \frac{2 \cdot g_m \cdot r_{D2} \cdot r_{D6}}{r_{D2}+r_{D4}} \)

\( CMRR = 20 log G \) - Power supply rejection ratio (PSRR)

- ─nderung des Ausgangssignals bei Spannungsversorgungsõnderung

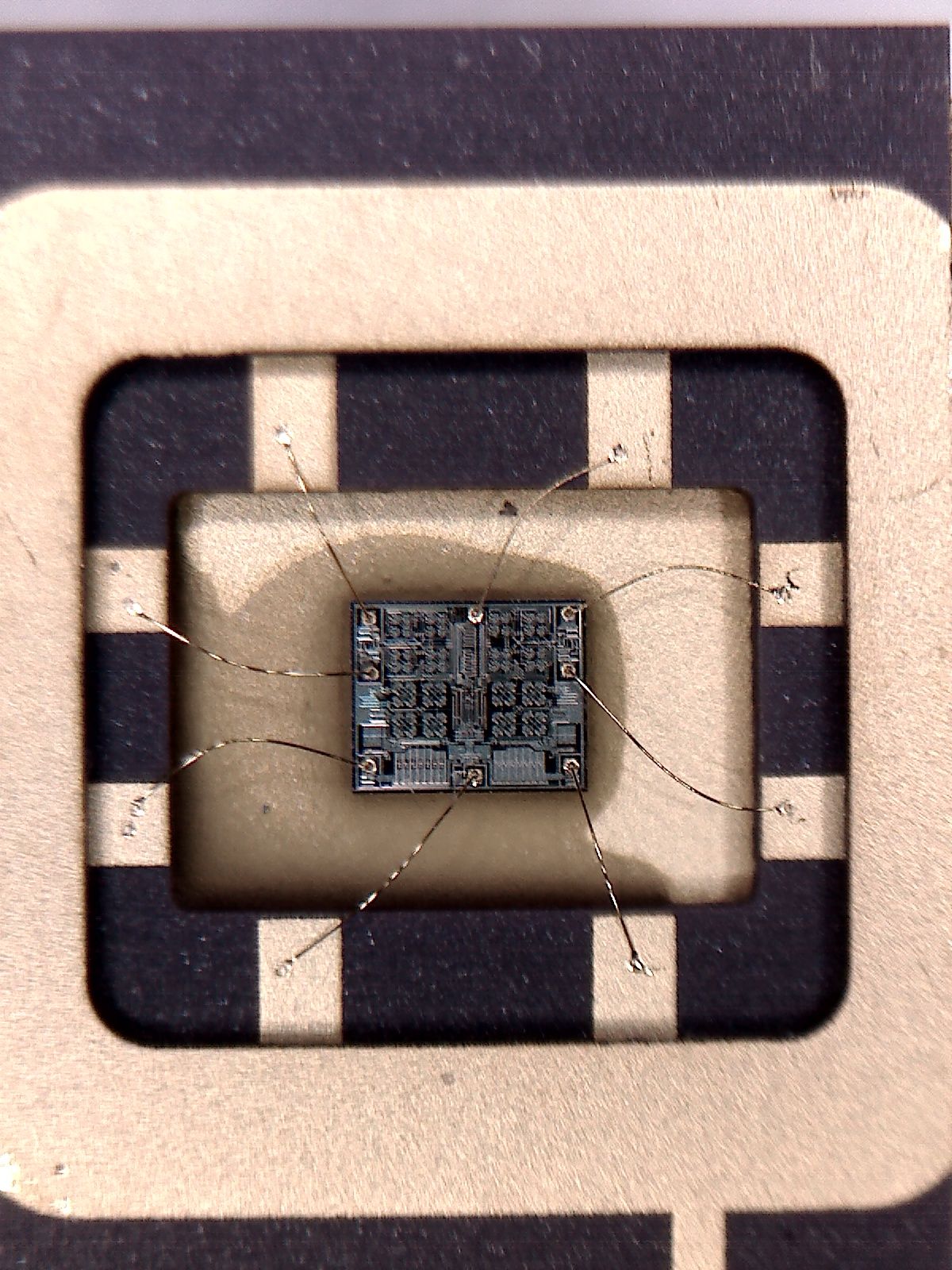

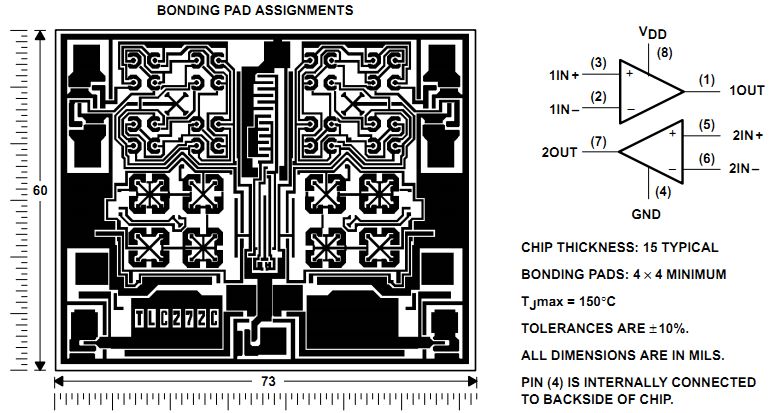

CMOS Operationsverstõrker TLC272 gebondeter Chip

|

|

Man kann integrierte Bauelemente auch als Wafer oder Chips bekommen.

Das Bild zeigt den Chip TLC272 dessen Bondpads mit feinen Golddrõhten (25 µm Dicke) mit dem Gehõuse verbunden sind.

Pin 1 ist bei dem Bild rechts oben, damit die Eingõnge links und die Ausgõnge rechts sind.

Die Chips wurden hier an der Hochschule Kempten im Labor Mikrosystemtechnik gebondet.

Es befinden sich 2 Operationsverstõker auf dem Chip. Einer oben und einer unten.

Die Spannungsversorgungspads befinden sich in der Mitte rechts (VDD) und links (GND).

Links oben und unten befinden sich jeweils die beiden Eingõnge.

Links In+ rechts In-.

Rechts oben und unten befinden sich die Ausgõnge.

Der Chip ist 1.524 mm x 1.8542 mm (60 mil x 73 mil) gross.

Weitere Informationen findet man auch im Datenblatt.

Das Bild zeigt den Chip TLC272 dessen Bondpads mit feinen Golddrõhten (25 µm Dicke) mit dem Gehõuse verbunden sind.

Pin 1 ist bei dem Bild rechts oben, damit die Eingõnge links und die Ausgõnge rechts sind.

Die Chips wurden hier an der Hochschule Kempten im Labor Mikrosystemtechnik gebondet.

Es befinden sich 2 Operationsverstõker auf dem Chip. Einer oben und einer unten.

Die Spannungsversorgungspads befinden sich in der Mitte rechts (VDD) und links (GND).

Links oben und unten befinden sich jeweils die beiden Eingõnge.

Links In+ rechts In-.

Rechts oben und unten befinden sich die Ausgõnge.

Der Chip ist 1.524 mm x 1.8542 mm (60 mil x 73 mil) gross.

Weitere Informationen findet man auch im Datenblatt.

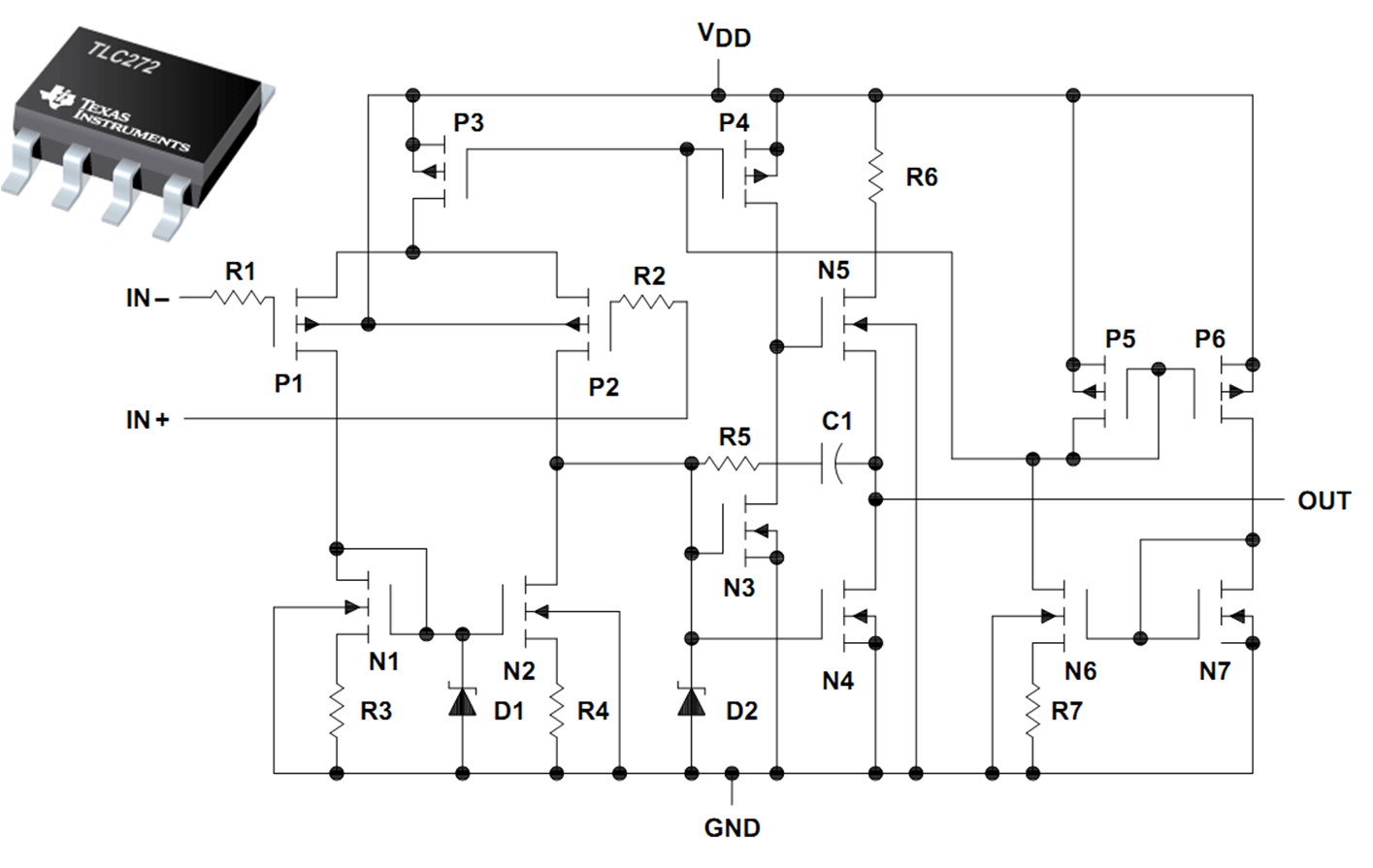

CMOS Operationsverstõrker TLC272

Quelle: Texas Instruments Datenblatt tlc272a.pdf

Referenzstromquelle rechts: P5, P6, N6, N7, R7

Differenzverstõrker: P1, P2, P3, N1, N2

Zenerdiode f³r den Startup

2.te Verstõrkerstufe: Sourceschaltung: N3, P4

Ausgangsstufe: N4, N5

Frequenzgangkompensation: R5, C1

Input/Output rail-to-rail Operationsverstõrker:

TLV246

MCP6022

Differenzverstõrker: P1, P2, P3, N1, N2

Zenerdiode f³r den Startup

2.te Verstõrkerstufe: Sourceschaltung: N3, P4

Ausgangsstufe: N4, N5

Frequenzgangkompensation: R5, C1

Input/Output rail-to-rail Operationsverstõrker:

TLV246

MCP6022

Nõchstes Mal:

- MOSFET-Stromquelle

- Differenzverstõrkerschaltung und Messung

- Input/Output rail-to-rail Operationsverstõrker MCP6022

07 Bipolartransistor