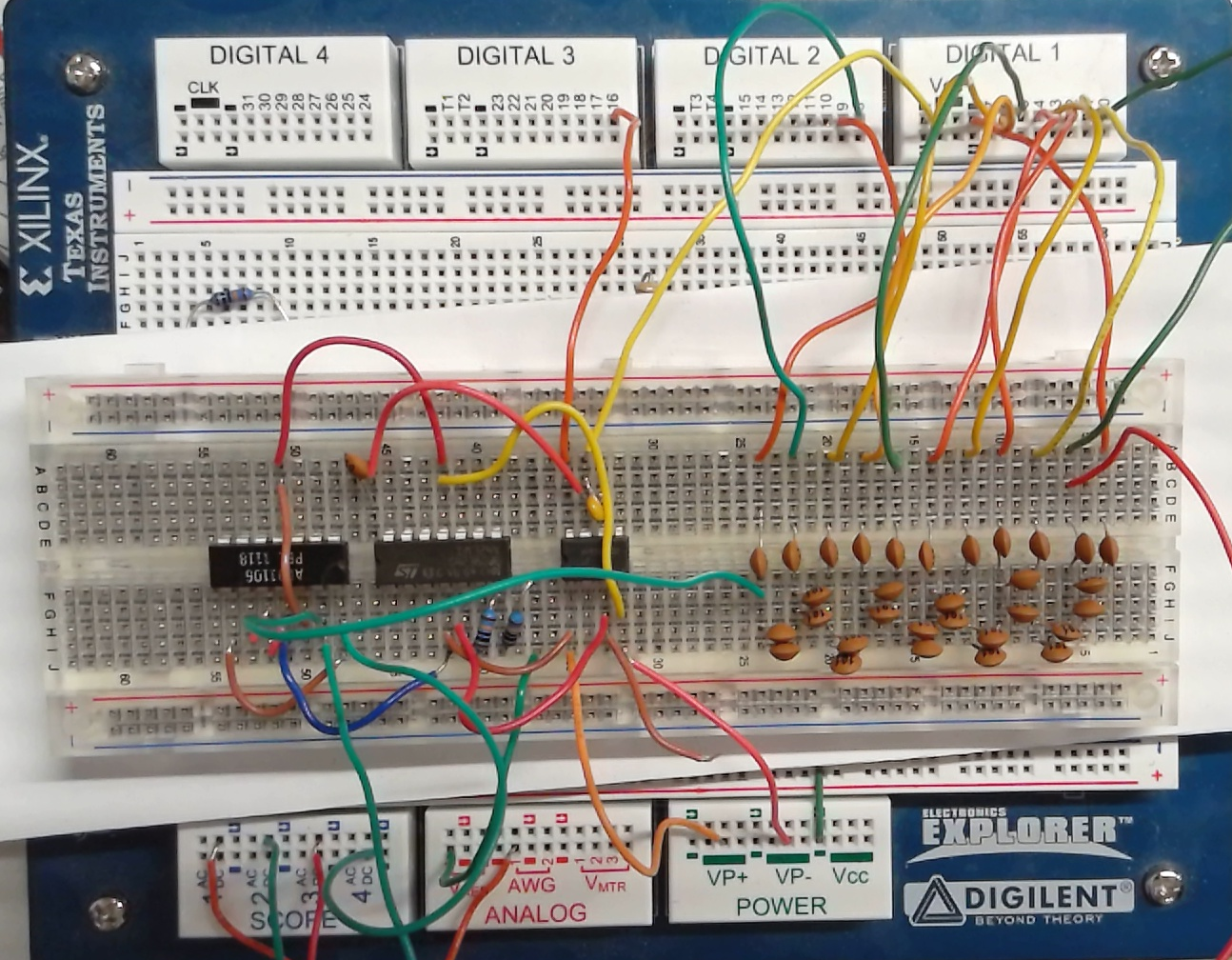

Laboratory 4: Measuring a 10 Bit C2C DACComponents:1 x Breadboard 22 x Capacitors (10 pF, 100 pF, 1 nF) Amplifier and sample and hold: 1 x LF398 1 x LM324 1 x ALD1106 1 x ALD1107 2 x Resistors 100 kΩ Easy wiring: 5 x 12 Pin connectors |

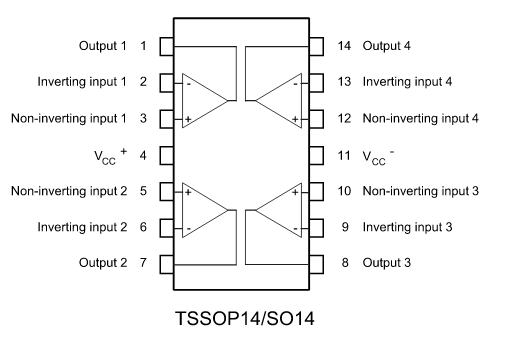

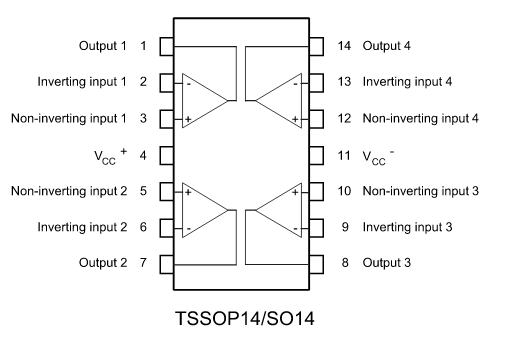

Operational amplifier LM324:

|

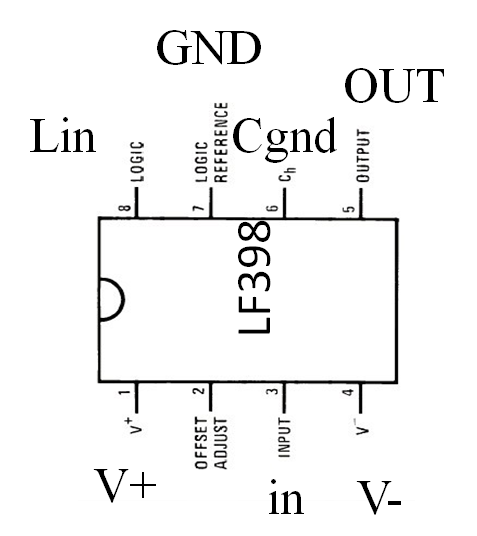

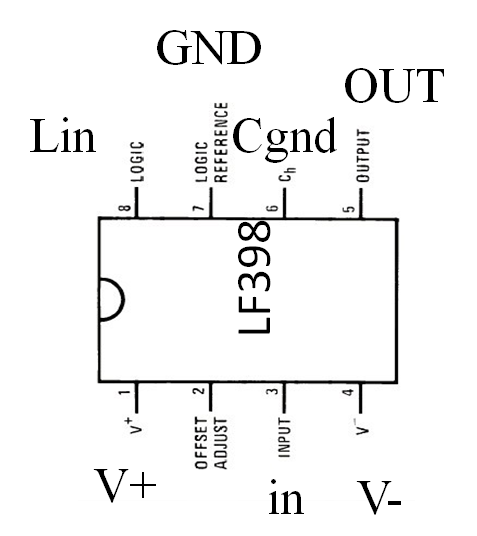

Sample and hold LF398: |

| Name | C1 | C2 | C3 | C4 | C5 | C6 | C7 | C8 | C9 | C10 | C11 | C12 |

| C [pF] | ||||||||||||

| Name | C13 | C14 | C15 | C16 | C17 | C18 | C19 | C20 | C21 | C22 | C23 | C24 |

| C [pF] | ||||||||||||

| Name | C25 | C26 | C27 | C28 | C29 | C30 | C31 | |||||

| C [pF] |