Elektronik 313 DigitaltechnikProf. Dr.Jörg Vollrath12 Schaltregler |

|

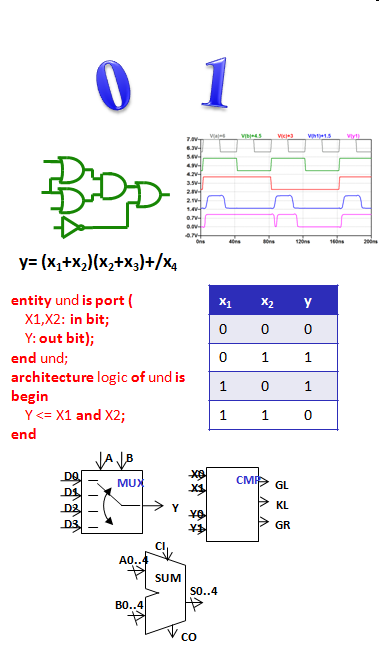

Video Digitaltechnik Transistorrealisierung

Video Digitaltechnik Logische Verknüpfung

Video Verzögerungszeiten

Digitaltechnik

|

|

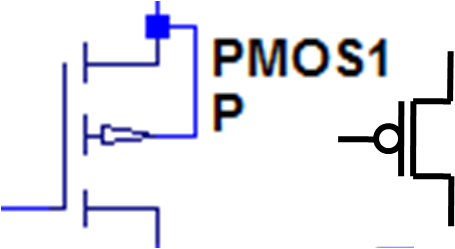

CMOS Transistoren als Schalter

| Symbol | Eingang: Gate | |||

PFET Transistor:

|

| 0

| 1

| |

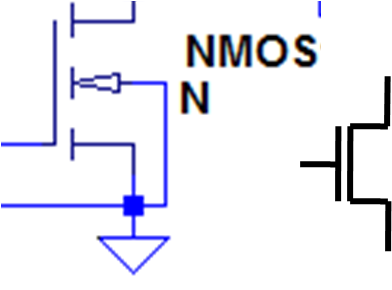

NFET Transistor:

|

| 0

| 1

| |

Zur Realisierung von booleschen Funktionen werden MOSFET (metal oxide semiconductor field effect transistor)

Transistoren eingesetzt.

Dabei werden Halbleiter (semiconductor, Silizium) verwendet, bei denen man durch Einbringen von Femdatomen (Dotierung) die Leitfähigkeit (Elektronen, Löcher) verändern kann.

Der MOS Transistor hat drei Anschlüsse Gate, Drain und Source.

Das Gate ist der Eingang. An der Drain ist der Ausgang und an der Source ist VDD (Betriebsspannnung, PFET) oder GND (0 V, NFET).

FET Feldeffekttransistor ist der Überbegriff für Halbleiterbaulemente, bei denen das elektrische Feld zwischen Gate und Kanal den Kanalwiderstand steuert bzw die Verbindung zwischen Drain und Source trennt oder schliesst.

Es gibt PFETs (PMOSFETs, Löcherleitung, positive Ladungsträger, Löcher) und NFETs (NMOSFETs, negative Ladungsträger, Elektronen) deren Verhalten komplementär sind (complementary metal oxide semiconductors, CMOS).

Ist die Gatesourcespannung beim NFET positiv, größer als eine Schwellspannung (threshold voltage), wird die Verbindung zwischen Drain und Source leitend (Ein Schalter wird geschlossen).

Ist die Gatesourcespannung beim PFET negativ, kleiner als eine Schwellspannung, wird die Verbindung zwischen Drain und Source leitend (Ein Schalter wird geschlossen).

Durch geschicktes Kombinieren der Transistoren können Logikfunktionen technisch realisiert werden.

Fast alle modernen Mikroprozessoren und digitalen Schaltungen werden mit CMOS Transistoren realisiert.

Dabei werden Halbleiter (semiconductor, Silizium) verwendet, bei denen man durch Einbringen von Femdatomen (Dotierung) die Leitfähigkeit (Elektronen, Löcher) verändern kann.

Der MOS Transistor hat drei Anschlüsse Gate, Drain und Source.

Das Gate ist der Eingang. An der Drain ist der Ausgang und an der Source ist VDD (Betriebsspannnung, PFET) oder GND (0 V, NFET).

FET Feldeffekttransistor ist der Überbegriff für Halbleiterbaulemente, bei denen das elektrische Feld zwischen Gate und Kanal den Kanalwiderstand steuert bzw die Verbindung zwischen Drain und Source trennt oder schliesst.

Es gibt PFETs (PMOSFETs, Löcherleitung, positive Ladungsträger, Löcher) und NFETs (NMOSFETs, negative Ladungsträger, Elektronen) deren Verhalten komplementär sind (complementary metal oxide semiconductors, CMOS).

Ist die Gatesourcespannung beim NFET positiv, größer als eine Schwellspannung (threshold voltage), wird die Verbindung zwischen Drain und Source leitend (Ein Schalter wird geschlossen).

Ist die Gatesourcespannung beim PFET negativ, kleiner als eine Schwellspannung, wird die Verbindung zwischen Drain und Source leitend (Ein Schalter wird geschlossen).

Durch geschicktes Kombinieren der Transistoren können Logikfunktionen technisch realisiert werden.

Fast alle modernen Mikroprozessoren und digitalen Schaltungen werden mit CMOS Transistoren realisiert.

CMOS Inverter (NOT) als Transistorschaltung

Der Schaltplan zeigt einen Inverter, eine Nicht (NOT) Funktion.

Nach der Wahrheitstabelle soll bei einer '1' am Eingang eine '0' am Ausgang erscheinen.

Das Signal wird invertiert.

Jeder Logikschaltkreis benötigt eine Spannungsversorgung (VDD).

Früher wurde für die Darstellung der '1' 5 V verwendet. Mit der Verkleinerung der Transistoren wurde die Geometrie kleiner. Damit die auftretenden elektrischen Feldstärken gleich blieben, wurde auch die Versorgungsspannung verkleinert.

2018 arbeitet man mit Versorgungsspannungen um die 1 V.

Dieser Pegel wird auch für die Logiksimulation verwendet. Im Praktikum sind Bausteine im Einsatz, die eine Versorgungsspannung zwischen 2.5 V und 5 V benötigen.

Nach der Wahrheitstabelle soll bei einer '1' am Eingang eine '0' am Ausgang erscheinen.

Das Signal wird invertiert.

Jeder Logikschaltkreis benötigt eine Spannungsversorgung (VDD).

Früher wurde für die Darstellung der '1' 5 V verwendet. Mit der Verkleinerung der Transistoren wurde die Geometrie kleiner. Damit die auftretenden elektrischen Feldstärken gleich blieben, wurde auch die Versorgungsspannung verkleinert.

2018 arbeitet man mit Versorgungsspannungen um die 1 V.

Dieser Pegel wird auch für die Logiksimulation verwendet. Im Praktikum sind Bausteine im Einsatz, die eine Versorgungsspannung zwischen 2.5 V und 5 V benötigen.

CMOS Inverter (NOT) Funktionalität

|

|

In der Simulation wird die Kennlinie eines Inverters dargestellt.

Bei der Simulation wird am Eingang die Spannung Vin von 0 auf 1 V verändert und

die Ausgangsspannung beobachtet.

Die Ausgangsspannung Vout ändert sich um Vin = 0.5 V von 1 V auf 0 V.

Man sieht in Grün, dass der Strom bei 0.5 V maximal ist. Bei 0 V und 1 V Eingangsspannung fließt fast kein Strom.

In Rot ist noch die Idealkennlinie eines Inverters dargestellt. Die reale Kennlinie ist sehr nah an der idealen Kennlinie.

Da um 0.5 V ein digitales Ergebnis nicht klar definiert ist, spezifiziert man mindest Eingangspegel VI und Ausgangspegel VO (output) für '0' low (L) und '1' high (H), mit denen das digitale System korrekt arbeitet.

Die Ausgangsspannung Vout ändert sich um Vin = 0.5 V von 1 V auf 0 V.

Man sieht in Grün, dass der Strom bei 0.5 V maximal ist. Bei 0 V und 1 V Eingangsspannung fließt fast kein Strom.

In Rot ist noch die Idealkennlinie eines Inverters dargestellt. Die reale Kennlinie ist sehr nah an der idealen Kennlinie.

Da um 0.5 V ein digitales Ergebnis nicht klar definiert ist, spezifiziert man mindest Eingangspegel VI und Ausgangspegel VO (output) für '0' low (L) und '1' high (H), mit denen das digitale System korrekt arbeitet.

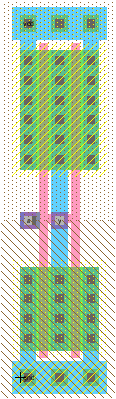

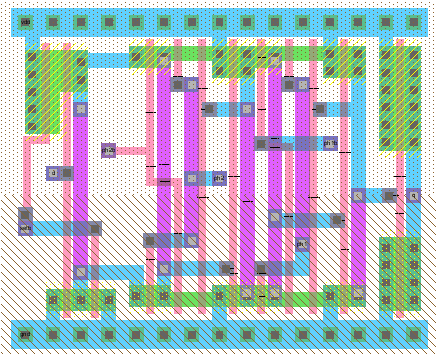

Physikalische Realisierung: CMOS Layout

In integrierten Schaltungen werden Transistoren durch Strukturierung

von verschiedenen Lagen von Materialien durch phototechnische Schritte erzeugt.

Die Strukturen für die Realisierung werden dabei in einem Layout festgelegt.

Unterschiedlich farbige Flächen stehen für unterschiedliche Materialien in unterschiedlichen übereinanderliegenden Ebenen.

Im Beispiel sind blaue und violette Flächen Metallverbindungen meist aus Aluminium.

Schwarze und graue Punkte sind Verbindungen (Kontakte) zwischen verschiedenen Ebenen.

Kreuzungen zwischen grünen Flächen und orangenen Linien erzeugen Transistoren.

Ist der Hintergrund punktiert entsteht ein PFET, ist der Hintergrund liniert ein NFET.

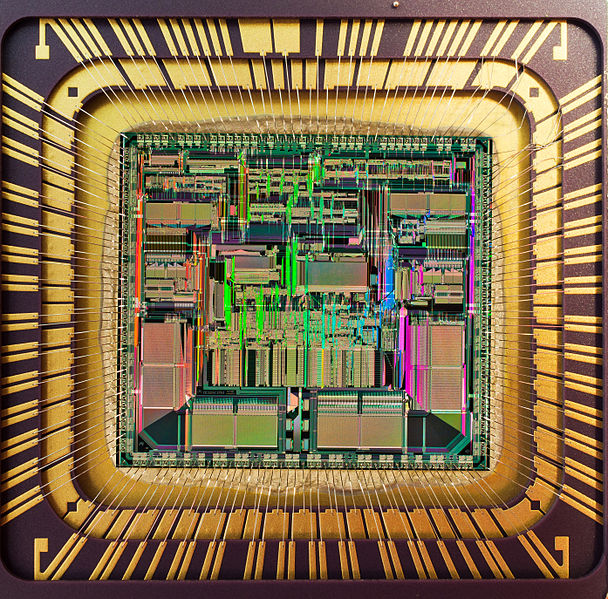

Einfache Strukturen werden nebeneinander gelegt und ergeben komplexere Funktionen, bis hin zum rechts gezeigten Mikroprozessor.

Typische Strukturgrößen reichen von früher einigen µm bis 2018 einigen nm.

Die Strukturen für die Realisierung werden dabei in einem Layout festgelegt.

Unterschiedlich farbige Flächen stehen für unterschiedliche Materialien in unterschiedlichen übereinanderliegenden Ebenen.

Im Beispiel sind blaue und violette Flächen Metallverbindungen meist aus Aluminium.

Schwarze und graue Punkte sind Verbindungen (Kontakte) zwischen verschiedenen Ebenen.

Kreuzungen zwischen grünen Flächen und orangenen Linien erzeugen Transistoren.

Ist der Hintergrund punktiert entsteht ein PFET, ist der Hintergrund liniert ein NFET.

Einfache Strukturen werden nebeneinander gelegt und ergeben komplexere Funktionen, bis hin zum rechts gezeigten Mikroprozessor.

Typische Strukturgrößen reichen von früher einigen µm bis 2018 einigen nm.

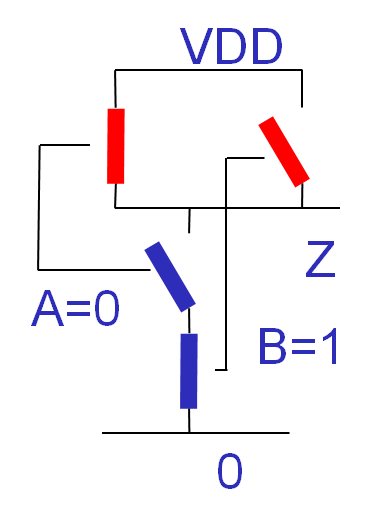

Bsp: Bestimmung einer Schaltfunktion

|

|

Die Transistoren werden im ersten Schritt durch Schalter ersetzt.

Bei einer gewählten Eingangssignalkombination wird dann verfolgt, ob der Ausgang mit VDD oder GND (0 V) verbunden ist, und sich so eine '1' oder '0' ergibt.

Daraus ergibt sich dann eine Wahrheitstabelle.

Bei einer gewählten Eingangssignalkombination wird dann verfolgt, ob der Ausgang mit VDD oder GND (0 V) verbunden ist, und sich so eine '1' oder '0' ergibt.

Daraus ergibt sich dann eine Wahrheitstabelle.

Darstellung boolescher Verknüpfungen NAND

SchaltfunktionY = f(X1,X2) = /(X1 ^ X2) = !(X1 · X2) X1, X2: Eingangsvariablen Y: Ausgangsvariable ^: Operationssymbol |

Schaltzeichen, Schaltsymbol

| |||||||||||||||

Wahrheitstabelle

|

Textuelle VHDL Beschreibung

|

Boolesche Algebra Grundfunktionen

Schaltfunktion |

Schaltsymbol |

Wahrheitstabelle | ||||||

NICHT, NOT\( Y = \overline{X} = !X = /X \) Y <= not (X); Y = !X; |

|

|

Zur vereinfachten Darstellung kann statt eines Inverters ein Kreis am Eingang gezeichnet werden.

Boolesche Algebra Grundfunktionen

Schaltfunktion |

Schaltsymbol |

Wahrheitstabelle | |||||||||||||||

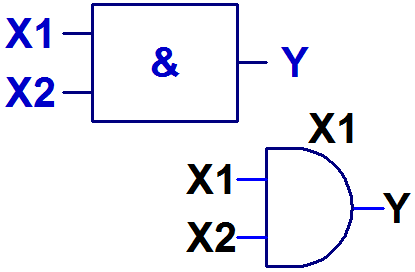

UND, ANDY = X1 ^ X2 = X1 · X2 Y <= X1 and X2; y = X1 && X2; |

|

| |||||||||||||||

ODER, ORY = X1 v X2 = X1 + X2 Y <= X1 or X2; y = X1 || X2; |

|

|

Diese Grundfunktionen finden sich in Formelsammlungen wieder oder werden auswendig gelernt.

Die Namen entsprechen der erwartenden Funktion (sprechende Namen).

UND: Nur wenn Eingang X1 und Eingang X2 '1' sind ergibt sich am Ausgang eine '1'.

ODER: Immer wenn Eingang X1 oder Eingang X2 '1' ist ergibt sich am Ausgang eine '1'.

Die Namen entsprechen der erwartenden Funktion (sprechende Namen).

UND: Nur wenn Eingang X1 und Eingang X2 '1' sind ergibt sich am Ausgang eine '1'.

ODER: Immer wenn Eingang X1 oder Eingang X2 '1' ist ergibt sich am Ausgang eine '1'.

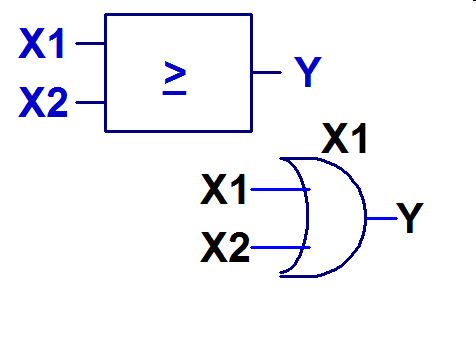

Boolesche Algebra Grundfunktionen

Schaltfunktion |

Schaltsymbol |

Wahrheitstabelle | |||||||||||||||

NAND\( Y = \overline{X1 \wedge X2} \) \( Y = \overline{X1 · X2} \) Y <= not (X1 and X2); y = not(X1 && X2); |

|

| |||||||||||||||

NOR\( Y = \overline{X1 \vee X2} \) \( Y = \overline{X1 + X2} \) Y <= not( X1 or X2); y = not( X1 || X2); |

|

|

Das vorgestellte N steht für not oder nicht.

Das Ausgangssignal der UND oder ODER Funktion wird invertiert.

Weitere Grundfunktionen

EXOR, XOR |

||||||||||||||||

Wahrheitstabelle | ||||||||||||||||

|

y=(not(X1) and X2) or (X1 and not(X2)) y=not(X1 and X2) and (X1 or X2) Y= X1 xor X2; |

| |||||||||||||||

Logikgatter Wikipedia

Logikfunktionen

Logikfunktionen in Excel

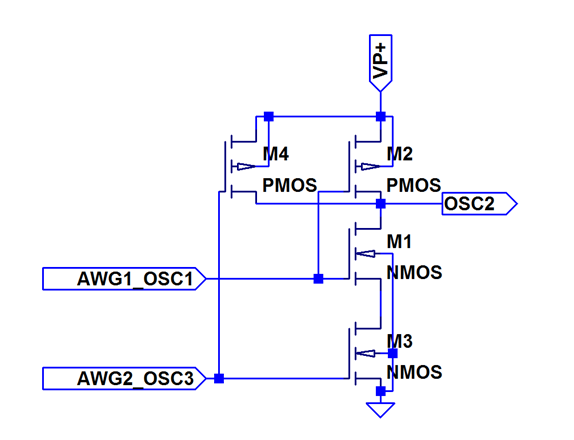

Simulation und Messung boolescher Verknüpfungen

Boolesche Algebra

Genauso wie für die Rechenregeln und Gesetze für natürliche Zahlen gibt es Rechenregeln und Gesetze für die boolesche Algebra.

Mehr Eingänge

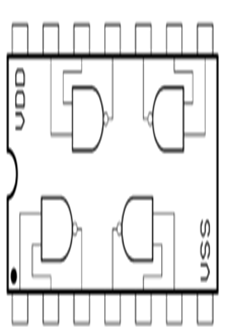

Physikalische Realisierung

7400 4-fach NAND mit 2 Eingängen (Dual in line DIL14 Gehäuse)

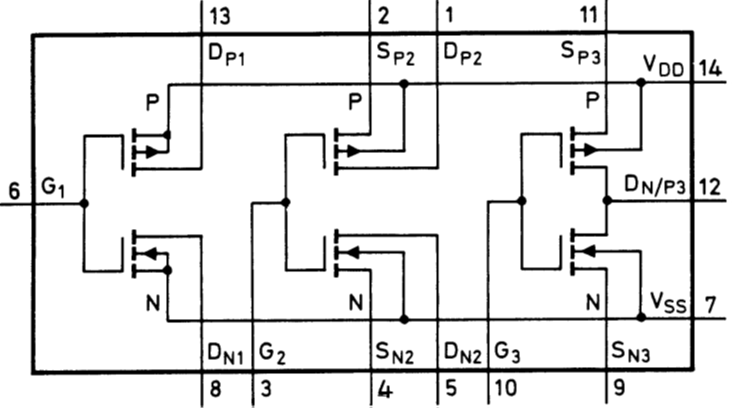

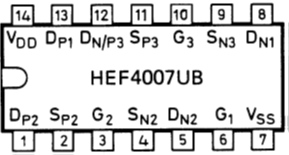

Logiktransistorarray 4007

4007 Transistorarray |

4007 Transistorarray |

4007 Transistorarray |

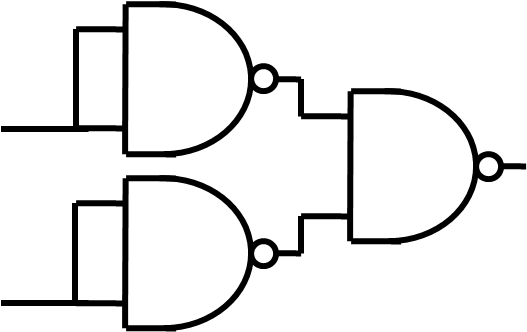

NAND Gatter |

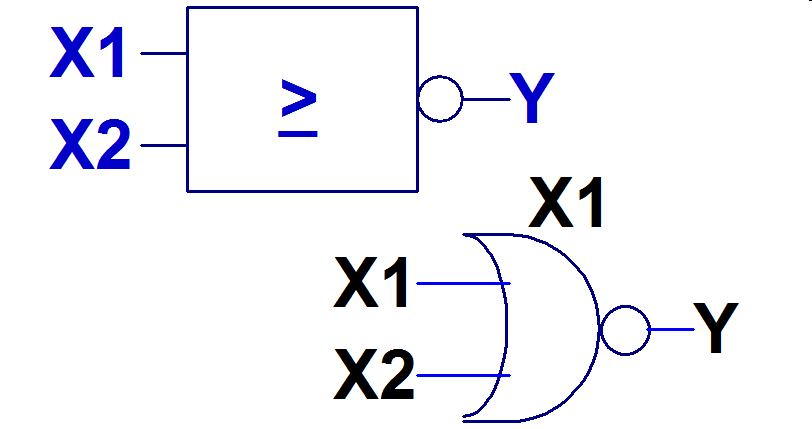

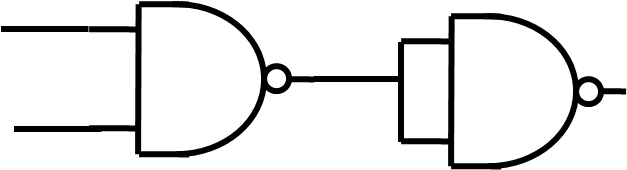

Darstellung von NICHT, UND, ODER durch NAND Funktionen

NICHT: Inverter

|

ODER

|

UND

|

Der Beweis der Äquivalenz ergibt sich entweder durch Vergleich der Wahrheitstabellen

oder durch Umformung der Gleichung mit der booleschen Algebra.

NAND: y = /(x1 · x2)

NICHT: /x = /(x · x)

UND: x1 · x2 = /(/(x1 · x2))

ODER: x1 + x2 = /(/x1 · /x2)

NAND: y = /(x1 · x2)

NICHT: /x = /(x · x)

UND: x1 · x2 = /(/(x1 · x2))

ODER: x1 + x2 = /(/x1 · /x2)

| x1 | x2 | NICHT(X1) /x1 | NICHT(X2) /x2 |

NAND / (x1 · x2) | UND x1 · x2 | ODER x1 + x2 |

NOR /x1 · /x2 |

| 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

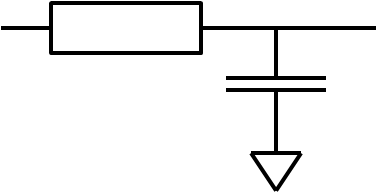

Verzögerungszeit

Propagation delay|

Vorstellung in der Elektrotechnik: Aufladung eines Kondensators (RC Delay) |

|

|

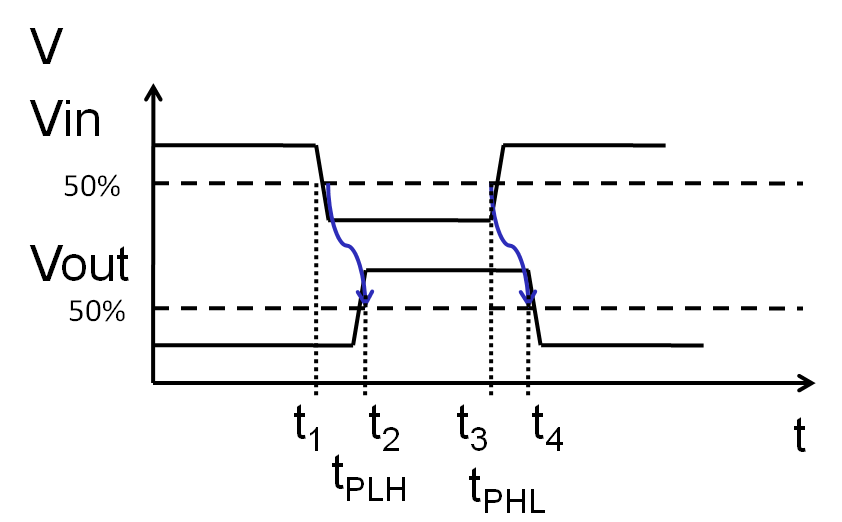

Propagation Delay tP: Blaue Pfeile Unterschiedlich für fallende und steigende Signale (Flanken) Unterschiedliche Transistoren sind aktiv. |

|

Beispiel

Definition

Die Zeit wird von der Änderung des Eingangssignals zur Änderung des Ausgangssignals gemessen.Eine Lastkapazität (Eingangskapazität C der nächsten Logikschaltung) wird durch einen Transitor mit einem Kanalwiderstand RDSon aufgeladen.

Bezugspegel zur Messung der Zeit sind 50% der Versorgungsspannung (Logisch '1').

Die Verzögerungszeit kann je nach steigender (PFET) oder fallender (NFET) Flanke des Signals am Ausgang variieren.

Die Verzögerungszeit kann bei verschiedenen Musterwechseln am Eingang unterschiedlich sein.

tpdLH= t2 - t1; Der Ausgang geht von Low (0) auf High (1)

tpdHL= t4 - t3; Der Ausgang geht von High (1) auf Low (0)

Ursache

Jeder CMOS Transistor hat eine Eingangskapazität am isolierten Gate und einen Widerstand zwischen Drain und Source.Über den Widerstand wird die Eingangskapazität des nächsten Gatters aufgeladen oder entladen.

Dies benötigt etwas Zeit.

Zusammenfassung und nächste Vorlesung

- Transistorrealisierung der boolschen Grundfunktionen

Nächstes Mal