Interface ElectronicsLaboratory 04: R2R DAC instructionsProf. Jörg Vollrath |

Overview

- R2R DAC

- Resistance measurement and LTSPICE schematic

- LTSPICE simulation: Ramp

- INL, DNL extraction

- LTSPICE simulation: sine

- FFT, INL, DNL, SNR

- Summary

This is a laboratory to simulate a R2R DAC with real resistor component values.

R2R DAC LTSPICE Simulation

|

The schematic shows a 4-bit R2R DAC.

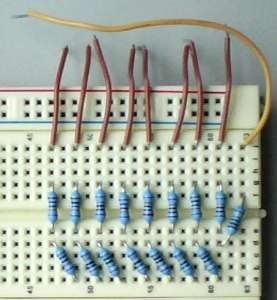

Build the circuit on a breadboard.

Measure the values of the resistors and document it in a table.

Build a 8-bit R2R DAC in LTSPICE with the measured resistance values.

Create a symbol and hook it up to the ADC DAC test circuit from last week.

Expand the test circuit like the slide "Test for 12 Bit ADC" in the presentation LTSPICE .

Simulate ramp and sine and extract INL, DNL and SNR data.

Simulate a ramp test.

Extract the simulated values with Read Raw File .

Calculate INL, DNL with any tool or use ReadOsci.html and paste the extracted values from LTSPICE into the input field.

Document and discuss INL and DNL values.

Simulate a sine signal test.

Extract the simulated values with Read Raw File .

Calculate FFT, INL, DNL with FFT webpage and paste the extracted values from LTSPICE into the input field.

Document and discuss FFT, INL, DNL and SNR values.

DAC measurement procedure

- Measure settling time: Full scale, mid scale

- Measure ramp

Extract oscilloscope data

Generate calibration data

Generate calibrated ramp - Measure calibrated ramp

Extract oscilloscope data - Generate sine data

Measure sine

Extract oscilloscope data

Analyze sine with FFT - Generate calibrated sine data

Measure sine

Extract oscilloscope data

Analyze sine with FFT

Define in the digital pattern generator one more channel for oscilloscope trigger.

Full scale: Define in the pattern generator a PP (push pull) clock

Mid scale: Put MSB on a separate channel as PP clock with 180° phase difference.

This gives you a mid scale 011111..100000 pattern.

For waveform generation DDS (direct digital synthesis) web page is used.

Fill in the number of bits. Push button "Generate a default calibration" table.

The number of points should be 4 times the number of used codes.

At the bottom of the page the EE vector data can be found.

A ramp up and down minimizes settling time issues.

Background for the need to extract data from oscilloscope data is given lecture: DAC practical considerations

Settling time

Full scale: Define in the pattern generator a PP (push pull) clock

Mid scale: Put MSB on a separate channel as PP clock with 180° phase difference.

This gives you a mid scale 011111..100000 pattern.

Ramp generation

For waveform generation DDS (direct digital synthesis) web page is used.

Fill in the number of bits. Push button "Generate a default calibration" table.

The number of points should be 4 times the number of used codes.

At the bottom of the page the EE vector data can be found.

A ramp up and down minimizes settling time issues.

Data extraction and analysis

Background for the need to extract data from oscilloscope data is given lecture: DAC practical considerations

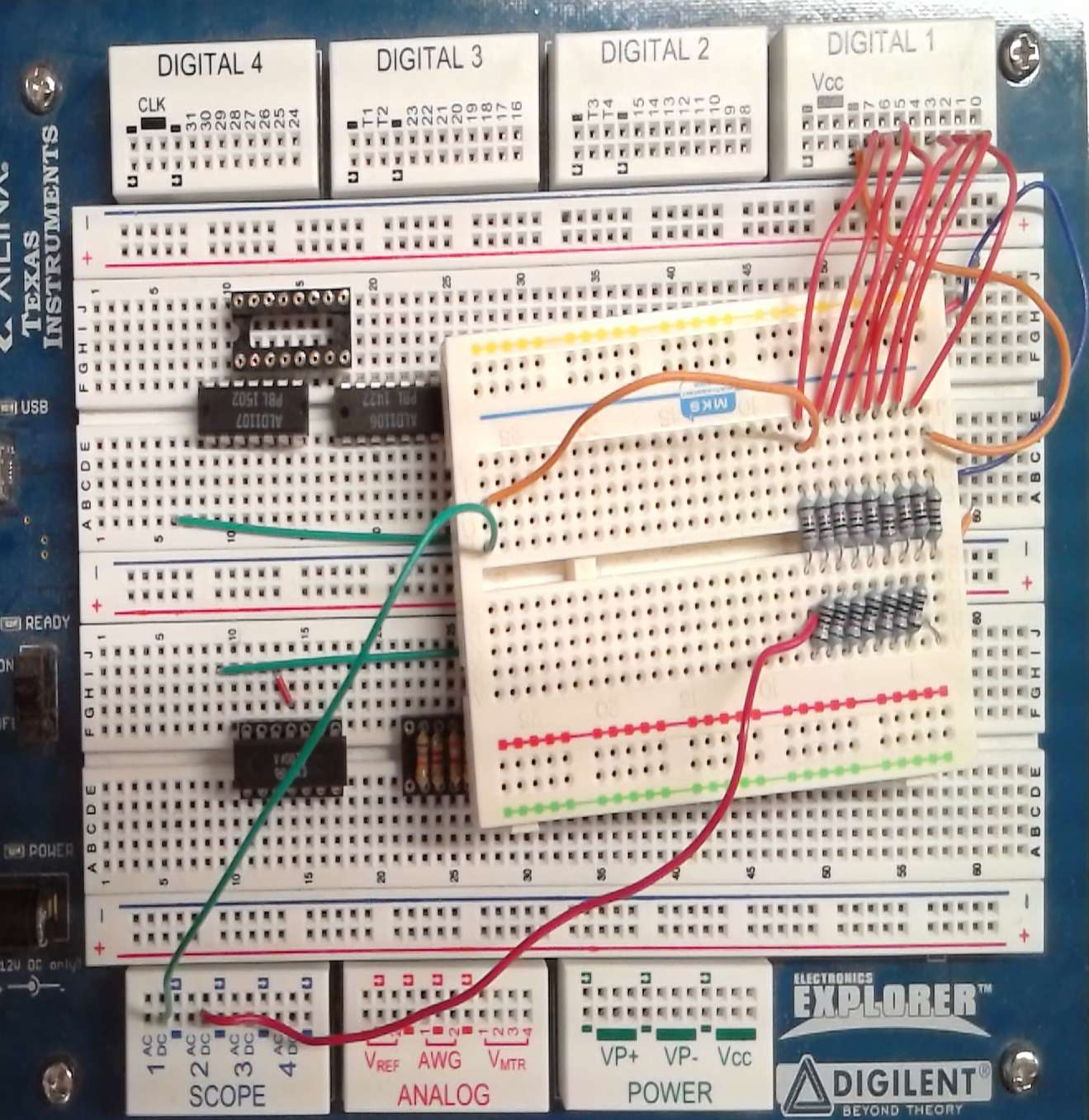

Breadboard R2R DAC

|

Duration 14:27 min 2019_V04_R2R_DAC_ramp.mp4 |

Start the digital pattern generator and oscilloscope for a ramp measurement.

Extract INL and DNL.

Details:

Data inputs are realized with DIGITAL1 0..7. All GND pins (Bold dash or small white arrow on colored background) are connected on the Electronic Explorer.

Connect D7 to SCOPE 1 DC input. This will be the trigger signal.

Connect Vout to SCOPE 2 DC input. This is the output of the DAC.

Make a photo of your setup connected to the Electronic Explorer.

Start Waveforms.

Start the oscilloscope: Scope

Start the digital Patterns

Select DI0..DI7 as bus and counter to generate a rising ramp

Generate a binary counter pattern with the pattern generator and look with the oscilloscope at the output of the 10-bit DAC.

Data inputs are realized with DIGITAL1 0..7. All GND pins (Bold dash or small white arrow on colored background) are connected on the Electronic Explorer.

Connect D7 to SCOPE 1 DC input. This will be the trigger signal.

Connect Vout to SCOPE 2 DC input. This is the output of the DAC.

Make a photo of your setup connected to the Electronic Explorer.

Start Waveforms.

Start the oscilloscope: Scope

Start the digital Patterns

Select DI0..DI7 as bus and counter to generate a rising ramp

Generate a binary counter pattern with the pattern generator and look with the oscilloscope at the output of the 10-bit DAC.

- Measure the resistance values with a multi meter.

- What is the offset, maximum voltage, LSB and settling time of the DAC?

Measure the signal Vout.

Details:

Open the 'Patterns' window.

Create a bus with D[0]..D[7].

Use the type binary counter, output PP.

Select a frequency of 10 MHz, 1 MHz, 100 kHz, 10 kHz under 'parameter' for the counter.

Connect the MSB to SCOPE 1 DC as a trigger signal.

Connect the output of the DAC to SCOPE 2 DC and change the counter frequency until you have a sawtooth curve.

- Measure and extract INL and DNL using

ReadOsci.html

Details:

With the oscilloscope do export data.

Copy the data into the 'input data' field.

Make sure to measure a positive ramp.

Set 'DNL, INL start', 'DNL, INL averaging length', 'DNL, INL step' and 'DNL, INL number of values' to appropriate values.

Set option for measurement analysis to 'Ramp INL, DNL'.

Do 'Process oscilloscope data'.

Document and discuss the result.

Select a frequency of 10 MHz, 1 MHz, 100 kHz, 10 kHz under 'parameter' for the counter.

What is the best frequency for the pattern generator for operation?

Document challenges, effort and results and discuss your results.

2019.11.11: Added task:

Show results of good extracted ramp data versus bad extracted ramp data.

Discuss the difference.

- Select the best frequency from the previous task.

Can you improve the INL and DNL of the transfer characteristic by changing resistors?

Measure the improved circuit.

Document the improved resistance values.

Document challenges, effort and results and discuss your results.

Settling time of R2R DAC

Duration 11:02 min 2019_V04_R2R_DAC_settling.mp4

Measure settling times for full level and mid level transition.

Measure it for rising and falling waveform.

Make sure that the settling time of the signal is ok for a full level transition.

Use the full vertical range of the oscilloscope to minimize error.

Channel 1 should show D7 and channel 2 should show the output voltage.

Measure settling time using a '00..0', '11..1' pattern:

Details:

Open the 'Patterns' window.

Select clock for the bus with values of 0 and 255.

Vary the clock frequency.

Select clock for the bus with values of 127 and 128, by moving MSB, DIO7 to a separate signal with aphase of 180°.

Vary the clock frequency.

Measure the settling time and switching noise of Vout.

Document challenges, effort and results and discuss your results.

Use the full vertical range of the oscilloscope to minimize error.

Channel 1 should show D7 and channel 2 should show the output voltage.

Measure settling time using a '00..0', '11..1' pattern:

Details:

Open the 'Patterns' window.

Select clock for the bus with values of 0 and 255.

Vary the clock frequency.

Select clock for the bus with values of 127 and 128, by moving MSB, DIO7 to a separate signal with aphase of 180°.

Vary the clock frequency.

Measure the settling time and switching noise of Vout.

Document challenges, effort and results and discuss your results.

Sine measurement of R2R DAC

Duration 11:02 min 2019_V04_R2R_DAC_sine.mp4

Measure a sine signal and extract SNR via FFT.

- Use a digital sine input and measure signal to noise ratio using a FFT.

Import 10Bit_Sine43Periods.csv into the pattern generator of the Electronic Explorer.

Details generating a sine signal:

New calibrated ramp data is loaded into the digital pattern generator with Type: Custom, Output: PP, Edit: Parameters, Import file, open file, Browse, Ok, Import.

Import 10Bit_Sine1Period.csv into the pattern generator of the Electronic Explorer.

You can use DDS_Sim_Javascript_2016.html to generate other digital sine signals.

Measure with different signal frequencies and analyze data with FFT_Javascript_2017_Calibration.html .

2019.11.11: Added task:

Show results of FFT of good extracted sine data versus bad extracted ramp data.

Discuss the difference.

Document challenges, effort and results and discuss your results.

Sine measurement of digital calibrated R2R DAC

Duration 11:02 min 2019_V04_R2R_DAC_cal.mp4

- Generate a calibration lookup table with ramp measurement

- Generate a new calibrated sine pattern

- Measure INL, DNL and FFT with calibrated sine pattern

- Use ReadOsci.html

to calculate a calibration lookup table and generate a better ramp

DDS_Sim_Javascript_2016.html and sine signal.

Details, Step by Step:

1) Start with DDS Javascript and fill 0..255 into Calibration, use 1024 number of points and do 'Ramp EE vector with calibration'

2) Save the generated vectors on the drive and import them into the digital pattern generator:

type custom, edit parameters, Import file, open file, browse ok import

3) Measure the ramp with the oscilloscope and export the data

4) Do ReadOsci.html

and do 'Digital calibrated INL, DNL'

The calibration data appear at the bottom

5) Copy the calibration data into the DDS Javascript Calibration data and generate 1024 vectors.

6) Use this vectors for the pattern generator.

7) Look at the oscilloscope data with Read osci and the reduced number of codes and look for INL and DNL

8) Use a sine waveform with calibration data and without, and compare SNR

Can you improve the INL and DNL of the transfer ramp characteristic by using digital calibration?

Can you improve the INL, DNL and signal to noise ratio of the sine characteristic by using digital calibration?

Measure the improved circuit.

Document challenges, effort and results and discuss your results.

- Document your results.

Summary

- Ramp measurement

fmax = ; INL = ; DNL - Settling time

fmeasure = ;

tfull scale, up = ; tfull scale, down = ; tmid scale, up = ; tmid scale, down = ; - Sine measurement

fmeasure = ;

SNR = ; SDR = ; ENOB = - Analog calibration

Rchange =

INL, DNL, SNR

- Digital calibration

#codes =

INL, DNL, SNR