Vollrath, Jörg

Prof. Dr.-Ing.

|

Vollrath, JörgProf. Dr.-Ing. |

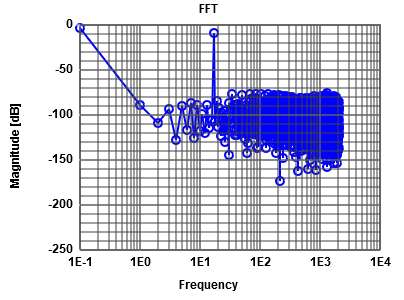

A Web based FFT playgroundA web page to do FFT is available for ADCs and DACs. The FFT playground should make it possible to investigate changing input signals (sine, square, sawtooth, triangle, AM, FM modulation) and FFT parameters (Number of point, sampling time) in a webpage. It is a project using HTML and JavaScript. |  |

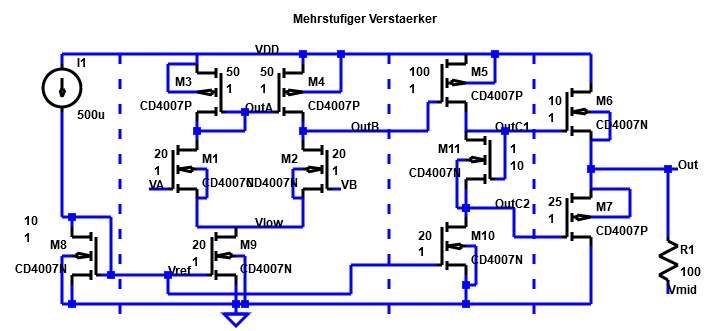

Operational amplifier investigationUsing LTSPICE an operational amplifier is built. A test suite is developed to be able to measure data sheet parameters: IDD, A0, slew rate, ft, CMM input range, CMRR, VDDRR and output range. Investigations of transistor sizing and data sheet parameters are done. |  |

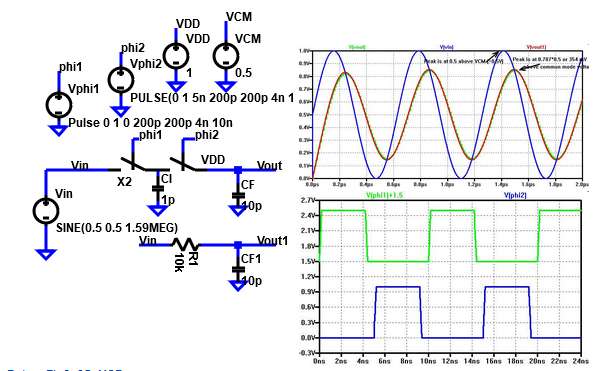

Switched capacitor circuitsA low pass circuit should be built and simulated using LTSPICE using RC circuit, SC circuit and a digital filter. Complex transfer function, H(z) and digital filter coefficients should be matched. |  |

|

With an ESP8266 kit realize a web oscilloscope interface for the 1 channel ADC

and a 4 channel SPI ADC extension board. Starting point: NodeMCU und ESP8266 - Einstieg in die Programmierung |  |

|

WS2020, Patil, Madhu With the StereoPi kit a 3D video for Cardboard or beamer and a depth map should be taken. Web page Crowd Supply Crowd funding platform, Web page StereoPi |  |

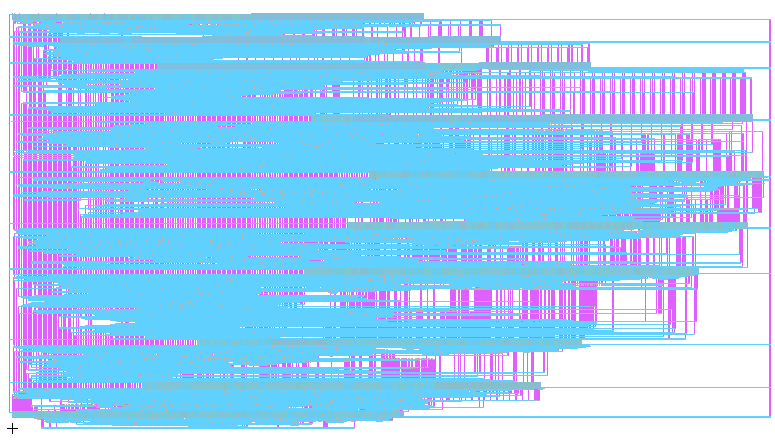

Open Access Microelectronics CourseA master level class Microelectronics is presented with the accompanying web page, tools usage of LTSPICE, Electric and ISE Webpack for design of a UART. It enables open access to an example of chip design. |  |

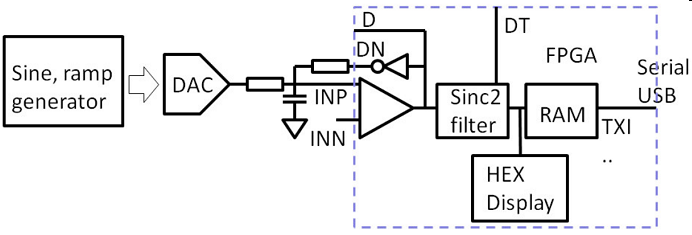

Implementation and Testing of a FPGA Based Sigma Delta Analog to Digital ConverterIn this work a 10-bit sigma-delta analog to digital converter was implemented using only a NEXYS 3 FPGA board in combination with some passive components. INL and DNL was measured for both devices. The overall setup revealed a SNR of 33.8 dB with an ENOB of 5.3 bits. |  |

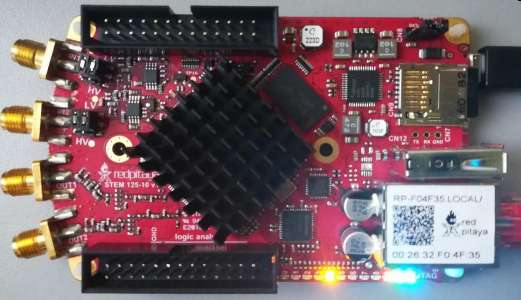

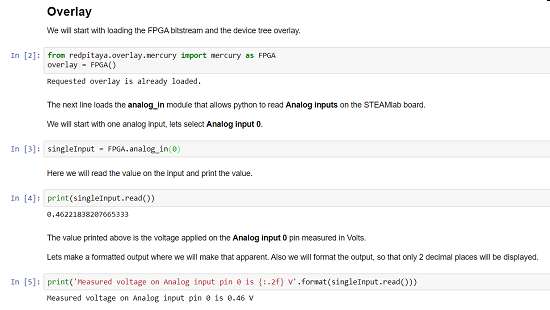

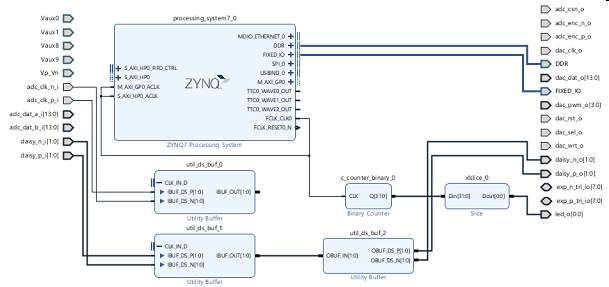

Corredor A Jupyter Notebook on Red Pitaya: LED control and FPGA design2020A redpitaya is an open source multifunctional laboratory instrument which contains an FPGA and ARM processor, ADC, DAC and LEDs. This project realizes user applications either using the available "default" design configuration with phyton and node.js or changing the FPGA design. |

|

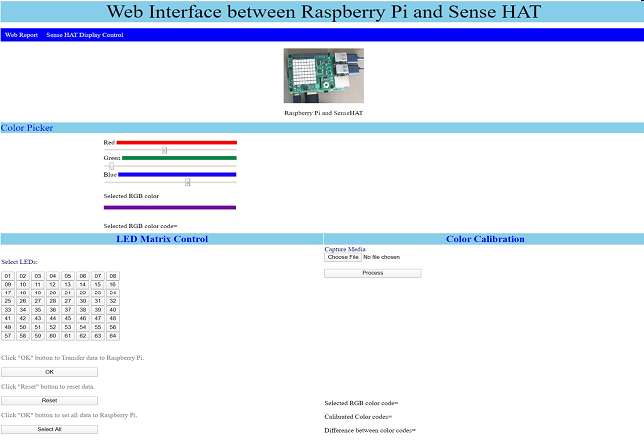

Hossain A Web-interface for a Sense HAT for Raspberry Pi2020The main goal of this scientific project is to run a Node.js server on Raspberry Pi and to control the LED matrix of the Sense HAT by a webpage. And at the same time, calibrate the color of LEDs of the Sense HAT. |

|